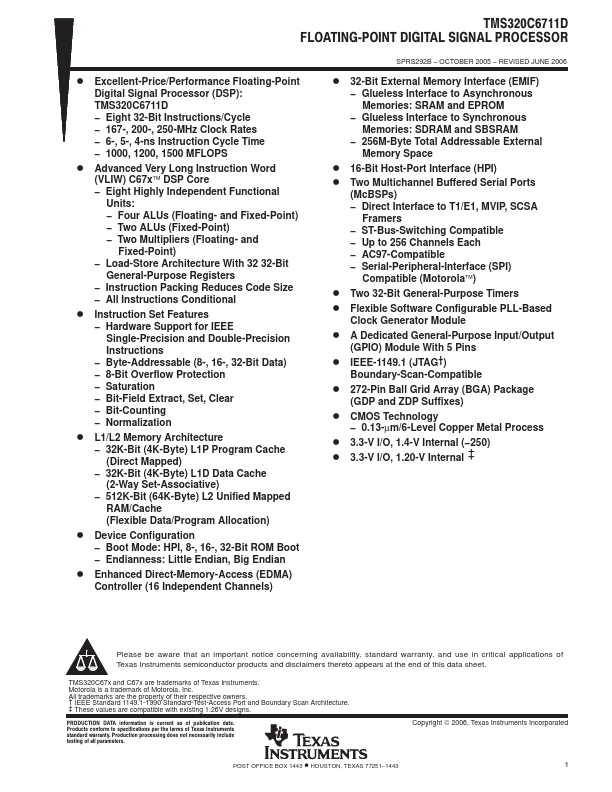

TMS320C6711D

TMS320C6711D is Floating-Point Digital Signal Processor manufactured by Texas Instruments.

Features

- Hardware Support for IEEE Single-Precision and Double-Precision Instructions

- Byte-Addressable (8-, 16-, 32-Bit Data)

- 8-Bit Overflow Protection

- Saturation

- Bit-Field Extract, Set, Clear

- Bit-Counting

- Normalization

D L1/L2 Memory Architecture

- 32K-Bit (4K-Byte) L1P Program Cache (Direct Mapped)

- 32K-Bit (4K-Byte) L1D Data Cache (2-Way Set-Associative)

- 512K-Bit (64K-Byte) L2 Unified Mapped RAM/Cache (Flexible Data/Program Allocation)

D Device Configuration

- Boot Mode: HPI, 8-, 16-, 32-Bit ROM Boot

- Endianness: Little Endian, Big Endian

D Enhanced Direct-Memory-Access (EDMA)

Controller (16 Independent Channels)

SPRS292B

- OCTOBER 2005

- REVISED JUNE 2006

D 32-Bit External Memory Interface (EMIF)

- Glueless Interface to Asynchronous Memories: SRAM and EPROM

- Glueless Interface to Synchronous Memories: SDRAM and SBSRAM

- 256M-Byte Total Addressable External Memory Space

D 16-Bit Host-Port Interface (HPI) D Two Multichannel Buffered Serial Ports

(Mc BSPs)

- Direct Interface to T1/E1, MVIP, SCSA

Framers

- ST-Bus-Switching patible

- Up to 256 Channels Each

- AC97-patible

- Serial-Peripheral-Interface (SPI) patible (Motorola)

D Two 32-Bit General-Purpose Timers D Flexible Software Configurable PLL-Based

Clock Generator Module

D A Dedicated General-Purpose Input/Output

(GPIO) Module With 5 Pins

D IEEE-1149.1 (JTAG†)

Boundary-Scan-patible

D 272-Pin Ball Grid Array (BGA) Package

(GDP and ZDP...