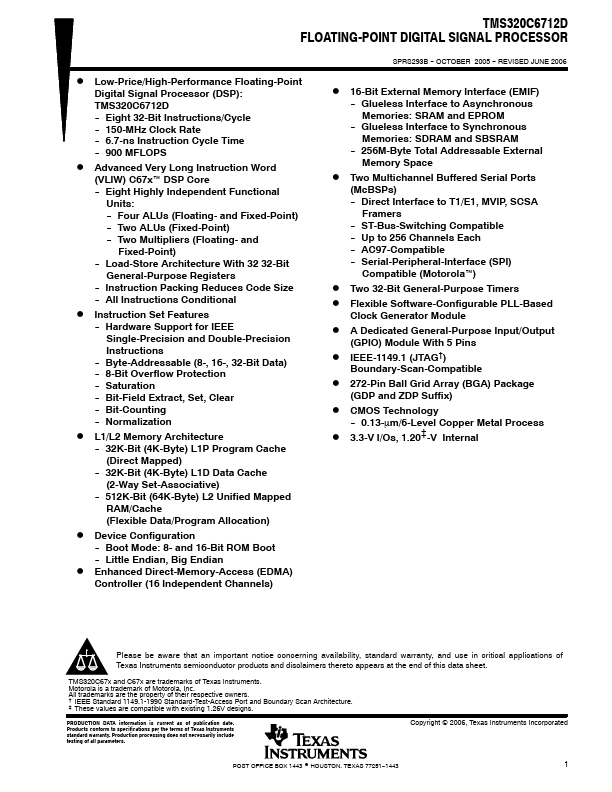

TMS320C6712D

TMS320C6712D is FLOATING-POINT DIGITAL SIGNAL PROCESSOR manufactured by Texas Instruments.

Features

-- Hardware Support for IEEE Single-Precision and Double-Precision Instructions

-- Byte-Addressable (8-, 16-, 32-Bit Data) -- 8-Bit Overflow Protection -- Saturation -- Bit-Field Extract, Set, Clear -- Bit-Counting -- Normalization

D L1/L2 Memory Architecture

-- 32K-Bit (4K-Byte) L1P Program Cache (Direct Mapped)

-- 32K-Bit (4K-Byte) L1D Data Cache (2-Way Set-Associative)

-- 512K-Bit (64K-Byte) L2 Unified Mapped RAM/Cache (Flexible Data/Program Allocation)

D Device Configuration

-- Boot Mode: 8- and 16-Bit ROM Boot -- Little Endian, Big Endian

D Enhanced Direct-Memory-Access (EDMA)

Controller (16 Independent Channels)

SPRS293B -- OCTOBER 2005 -- REVISED JUNE 2006

D 16-Bit External Memory Interface (EMIF)

-- Glueless Interface to Asynchronous Memories: SRAM and EPROM

-- Glueless Interface to Synchronous Memories: SDRAM and SBSRAM

-- 256M-Byte Total Addressable External Memory Space

D Two Multichannel Buffered Serial Ports

(Mc BSPs) -- Direct Interface to T1/E1, MVIP, SCSA

Framers -- ST-Bus-Switching patible -- Up to 256 Channels Each -- AC97-patible -- Serial-Peripheral-Interface (SPI) patible (Motorola)

D Two 32-Bit General-Purpose Timers D Flexible Software-Configurable PLL-Based

Clock Generator Module

D A Dedicated General-Purpose Input/Output

(GPIO) Module With 5 Pins

D IEEE-1149.1 (JTAG†)

Boundary-Scan-patible

D 272-Pin Ball Grid Array (BGA) Package

(GDP and ZDP Suffix)

D CMOS Technology

-- 0.13-m/6-Level Copper Metal Process

D 3.3-V I/Os, 1.20‡-V Internal

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

TMS320C67x and C67x are trademarks of Texas Instruments. Motorola is a trademark of Motorola, Inc. All trademarks are the property of their respective owners. † IEEE Standard 1149.1-1990 Standard-Test-Access Port and Boundary Scan Architecture. ‡ These values are patible with...