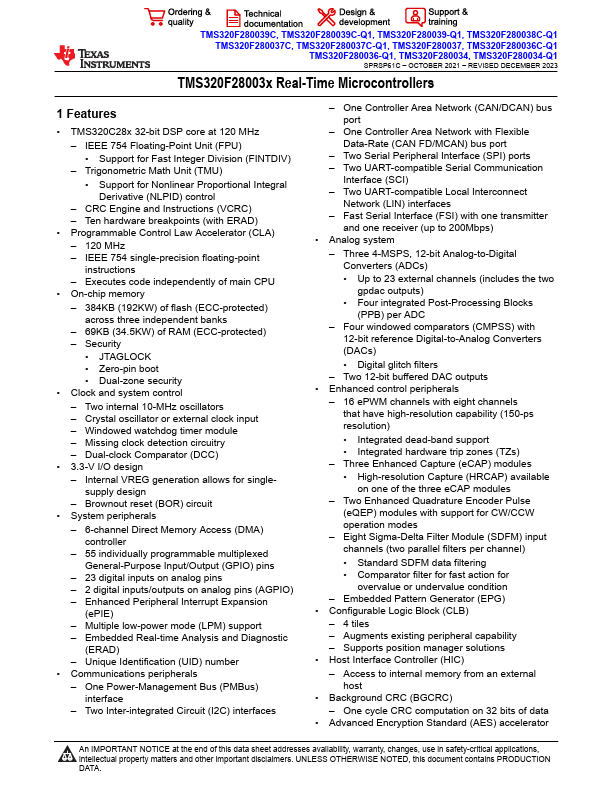

TMS320F280036C-Q1

Overview

- TMS320C28x 32-bit DSP core at 120 MHz - IEEE 754 Floating-Point Unit (FPU)

- Support for Fast Integer Division (FINTDIV) - Trigonometric Math Unit (TMU)

- Support for Nonlinear Proportional Integral Derivative (NLPID) control - CRC Engine and Instructions (VCRC) - Ten hardware breakpoints (with ERAD)

- Programmable Control Law Accelerator (CLA) - 120 MHz - IEEE 754 single-precision floating-point instructions - Executes code independently of main CPU

- On-chip memory - 384KB (192KW) of flash (ECC-protected) across three independent banks - 69KB (34.5KW) of RAM (ECC-protected) - Security

- JTAGLOCK

- Zero-pin boot

- Dual-zone security

- Clock and system control - Two internal 10-MHz oscillators - Crystal oscillator or external clock input - Windowed watchdog timer module - Missing clock detection circuitry - Dual-clock Comparator (DCC)

- 3.3-V I/O design - Internal VREG generation allows for singlesupply design - Brownout reset (BOR) circuit