TMS320F28015

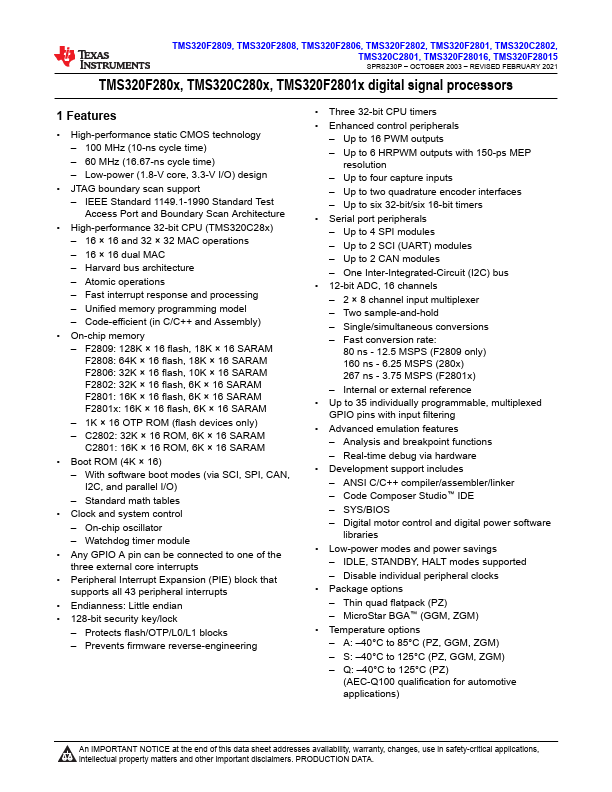

Features

- High-performance static CMOS technology

- 100 MHz (10-ns cycle time)

- 60 MHz (16.67-ns cycle time)

- Low-power (1.8-V core, 3.3-V I/O) design

- JTAG boundary scan support

- IEEE Standard 1149.1-1990 Standard Test Access Port and Boundary Scan Architecture

- High-performance 32-bit CPU (TMS320C28x)

- 16 × 16 and 32 × 32 MAC operations

- 16 × 16 dual MAC

- Harvard bus architecture

- Atomic operations

- Fast interrupt response and processing

- Unified memory programming model

- Code-efficient (in C/C++ and Assembly)

- On-chip memory

- F2809: 128K × 16 flash, 18K × 16 SARAM F2808: 64K × 16 flash, 18K × 16 SARAM F2806: 32K × 16 flash, 10K × 16 SARAM F2802: 32K × 16 flash, 6K × 16 SARAM F2801: 16K × 16 flash, 6K × 16 SARAM F2801x: 16K × 16 flash, 6K × 16 SARAM

- 1K × 16 OTP ROM (flash devices only)

- C2802: 32K × 16 ROM, 6K × 16 SARAM C2801: 16K × 16 ROM, 6K × 16 SARAM

- Boot ROM (4K × 16)

- With software boot modes (via SCI, SPI, CAN, I2C, and parallel I/O)

- Standard math...