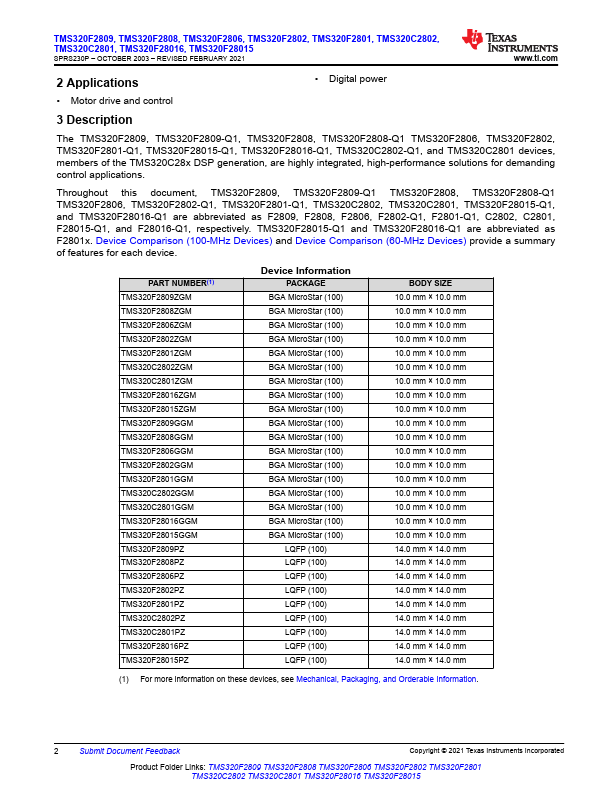

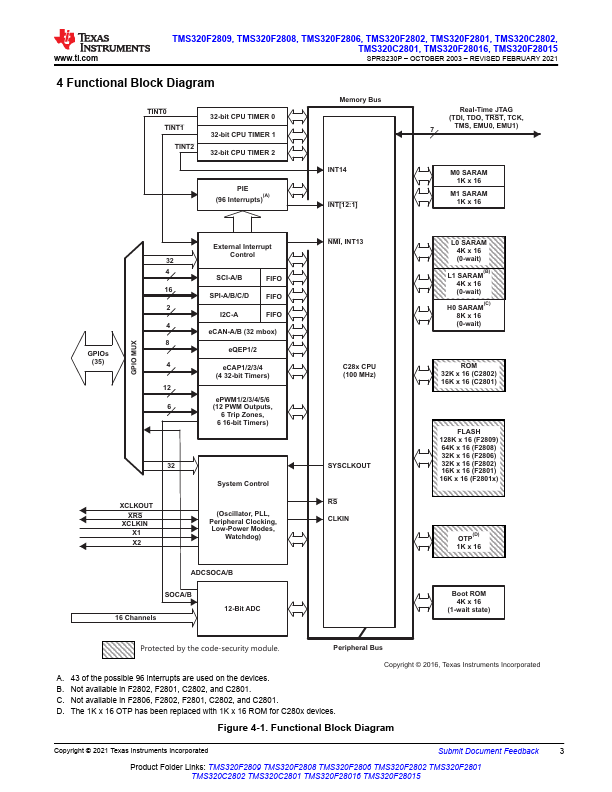

TMS320F2809 Description

.ti. TMS320F2809, TMS320F2808, TMS320F2806, TMS320F2802, TMS320F2801, TMS320C2802, TMS320F2809, TMS320F2808, TMS320F2806T,MTSM3S2302C02F820810,2T, MTMS3S2302F02F82081061,, TTMMSS332200FC228800125, TMSSPR3S2203C0P28 0O1C,TTOMBESR322000F3.

TMS320F2809 Key Features

- High-performance static CMOS technology

- 100 MHz (10-ns cycle time)

- 60 MHz (16.67-ns cycle time)

- Low-power (1.8-V core, 3.3-V I/O) design

- JTAG boundary scan support

- IEEE Standard 1149.1-1990 Standard Test Access Port and Boundary Scan Architecture

- High-performance 32-bit CPU (TMS320C28x)

- 16 × 16 and 32 × 32 MAC operations

- 16 × 16 dual MAC

- Harvard bus architecture