TPS53317

Description

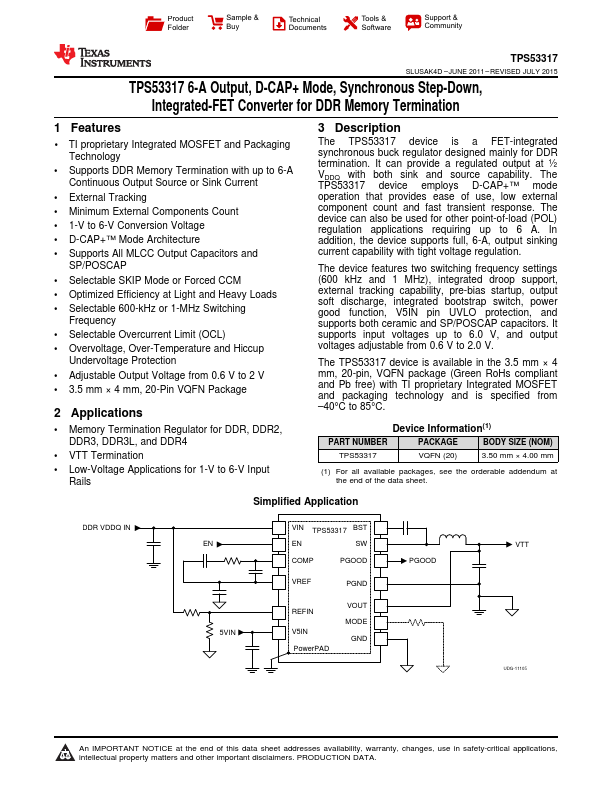

The TPS53317 device is a FET-integrated synchronous buck regulator designed mainly for DDR termination.

Key Features

- 1 TI proprietary Integrated MOSFET and Packaging Technology

- Supports DDR Memory Termination with up to 6-A Continuous Output Source or Sink Current

- External Tracking

- 1-V to 6-V Conversion Voltage

- D-CAP+™ Mode Architecture

- Supports All MLCC Output Capacitors and

- Selectable SKIP Mode or Forced CCM

- Optimized Efficiency at Light and Heavy Loads

- Selectable 600-kHz or 1-MHz Switching

- Selectable Overcurrent Limit (OCL)

Applications

- Memory Termination Regulator for DDR, DDR2, DDR3, DDR3L, and DDR4