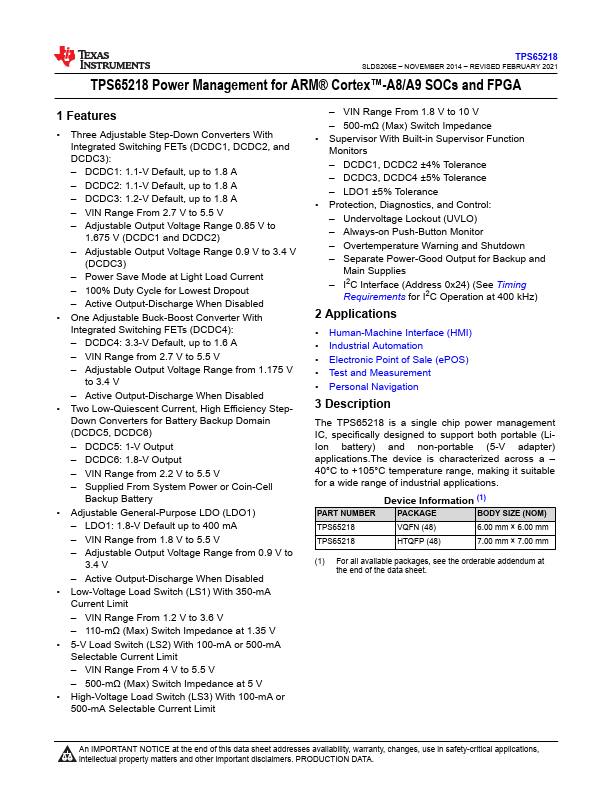

TPS65218

TPS65218 is Power Management manufactured by Texas Instruments.

Three Adjustable Step-Down Converters With Integrated Switching FETs (DCDC1, DCDC2, and DCDC3):

- DCDC1: 1.1-V Default, up to 1.8 A

- DCDC2: 1.1-V Default, up to 1.8 A

- DCDC3: 1.2-V Default, up to 1.8 A

- VIN Range From 2.7 V to 5.5 V

- Adjustable Output Voltage Range 0.85 V to 1.675 V (DCDC1 and DCDC2)

- Adjustable Output Voltage Range 0.9 V to 3.4 V (DCDC3)

- Power Save Mode at Light Load Current

- 100% Duty Cycle for Lowest Dropout

- Active Output-Discharge When Disabled

- One Adjustable Buck-Boost Converter With Integrated Switching FETs (DCDC4):

- DCDC4: 3.3-V Default, up to 1.6 A

- VIN Range from 2.7 V to 5.5 V

- Adjustable Output Voltage Range from 1.175 V to 3.4 V

- Active Output-Discharge When Disabled

- Two Low-Quiescent Current, High Efficiency Step Down Converters for Battery Backup Domain (DCDC5, DCDC6)

- DCDC5: 1-V Output

- DCDC6: 1.8-V Output

- VIN Range from 2.2 V to 5.5 V

- Supplied From System Power or Coin-Cell Backup Battery

- Adjustable General-Purpose LDO (LDO1)

- LDO1: 1.8-V Default up to 400 m A

- VIN Range from 1.8 V to 5.5 V

- Adjustable Output Voltage Range from 0.9 V to 3.4 V

- Active Output-Discharge When Disabled

- Low-Voltage Load Switch (LS1) With 350-m A Current Limit

- VIN Range From 1.2 V to 3.6 V

- 110-mΩ (Max) Switch Impedance at 1.35 V

- 5-V Load Switch (LS2) With 100-m A or 500-m A Selectable Current Limit

- VIN Range From 4 V to 5.5...