TPS7A37

TPS7A37 is Low-Dropout Regulator manufactured by Texas Instruments.

ures

- 1 Stable with 1-μF or Larger Ceramic Output Capacitor

- Input Voltage Range: 2.2 V to 5.5 V

- Ultralow Dropout Voltage:

- 200-m V Maximum at 1 A

- Excellent Load Transient Response- Even With

Only 1-μF Output Capacitor

- NMOS Topology Delivers Low Reverse Leakage

Current

- Excellent Accuracy:

- 0.23% Nominal Accuracy

- 1% Overall Accuracy Over Line, Over Load, and Over Temperature

- Less Than 20-n A typical IQ in Shutdown Mode

- Thermal Shutdown and Current Limit for Fault

Protection

2 Applications

- Point of Load Regulation for DSPs, FPGAs, ASICs, and Microprocessors

- Post-Regulation for Switching Supplies

- Portable and Battery-Powered Equipment

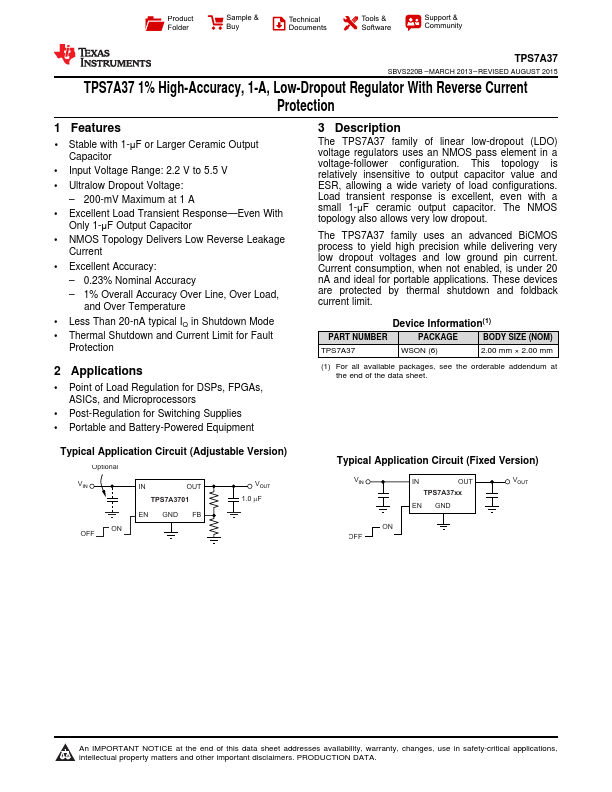

SPACE Typical Application Circuit (Adjustable Version)

Optional

VIN IN OUT

VOUT

TPS7A3701

1.0 m F

EN GND FB

3 Description

The TPS7A37 family of linear low-dropout (LDO) voltage regulators uses an NMOS pass element in a voltage-follower configuration. This topology is relatively insensitive to output capacitor value and ESR, allowing a wide variety of load configurations. Load transient response is excellent, even with a small 1-μF ceramic output capacitor. The NMOS topology also allows very low dropout.

The TPS7A37 family uses an advanced Bi CMOS process to yield high precision while delivering very low dropout voltages and low ground pin current. Current consumption, when not enabled, is under 20 n A and ideal for portable applications. These devices are protected by thermal shutdown and foldback current limit.

Device...