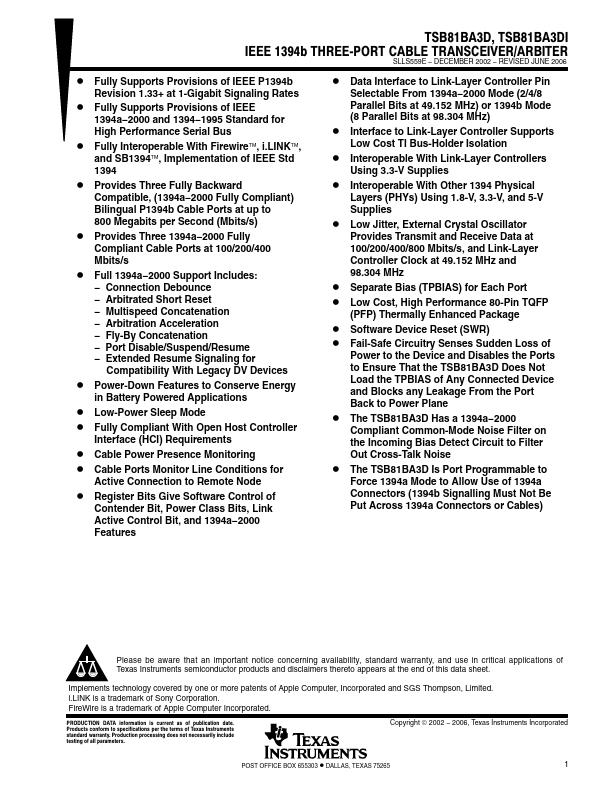

TSB81BA3D

Overview

- Low-Power Sleep Mode

- Fully Compliant With Open Host Controller Interface (HCI) Requirements

- Cable Power Presence Monitoring

- Cable Ports Monitor Line Conditions for Active Connection to Remote Node

- Register Bits Give Software Control of Contender Bit, Power Class Bits, Link Active Control Bit, and 1394a-2000 Features

- Data Interface to Link-Layer Controller Pin Selectable From 1394a-2000 Mode (2/4/8 Parallel Bits at 49.152 MHz) or 1394b Mode (8 Parallel Bits at 98.304 MHz)

- Interface to Link-Layer Controller Supports Low Cost TI Bus-Holder Isolation

- Interoperable With Link-Layer Controllers Using 3.3-V Supplies

- Interoperable With Other 1394 Physical Layers (PHYs) Using 1.8-V, 3.3-V, and 5-V Supplies

- Low Jitter, External Crystal Oscillator Provides Transmit and Receive Data at 100/200/400/800 Mbits/s, and Link-Layer Controller Clock at 49.152 MHz and 98.304 MHz