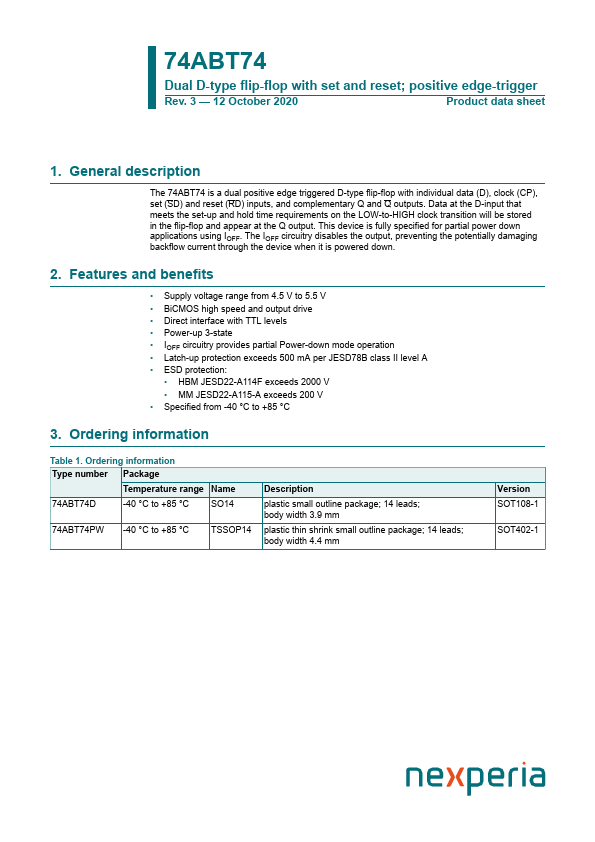

74ABT74

Description

The 74ABT74 is a dual positive edge triggered D-type flip-flop with individual data (D), clock (CP), set (SD) and reset (RD) inputs, and plementary Q and Q outputs.

Key Features

- Supply voltage range from 4.5 V to 5.5 V

- BiCMOS high speed and output drive

- Direct interface with TTL levels

- Power-up 3-state

- IOFF circuitry provides partial Power-down mode operation

- Latch-up protection exceeds 500 mA per JESD78B class II level A

- ESD protection

- HBM JESD22-A114F exceeds 2000 V

- MM JESD22-A115-A exceeds 200 V

- Specified from -40 °C to +85 °C