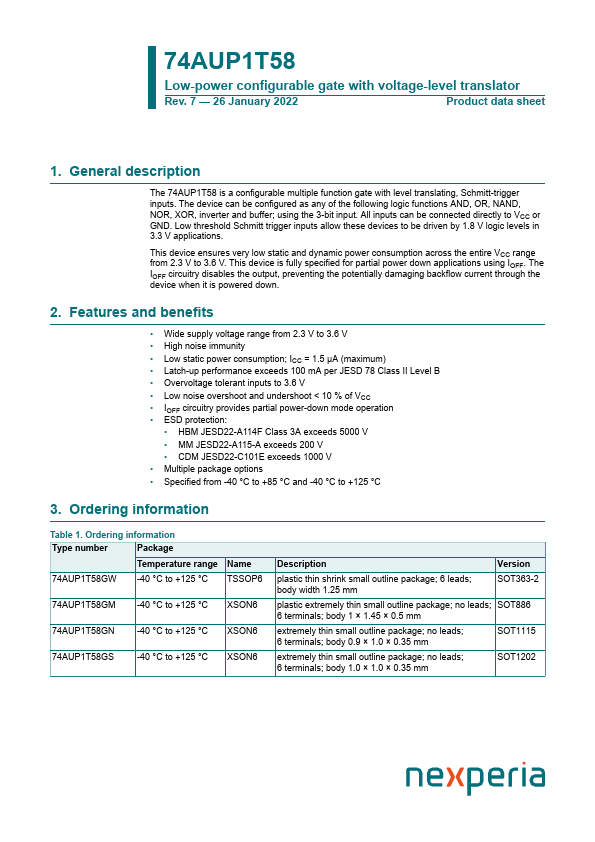

74AUP1T58

74AUP1T58 is Low-power configurable gate manufactured by Nexperia.

Low-power configurable gate with voltage-level translator

Rev. 7

- 26 January 2022

Product data sheet

1. General description

The 74AUP1T58 is a configurable multiple function gate with level translating, Schmitt-trigger inputs. The device can be configured as any of the following logic functions AND, OR, NAND, NOR, XOR, inverter and buffer; using the 3-bit input. All inputs can be connected directly to VCC or GND. Low threshold Schmitt trigger inputs allow these devices to be driven by 1.8 V logic levels in 3.3 V applications.

This device ensures very low static and dynamic power consumption across the entire VCC range from 2.3 V to 3.6 V. This device is fully specified for...