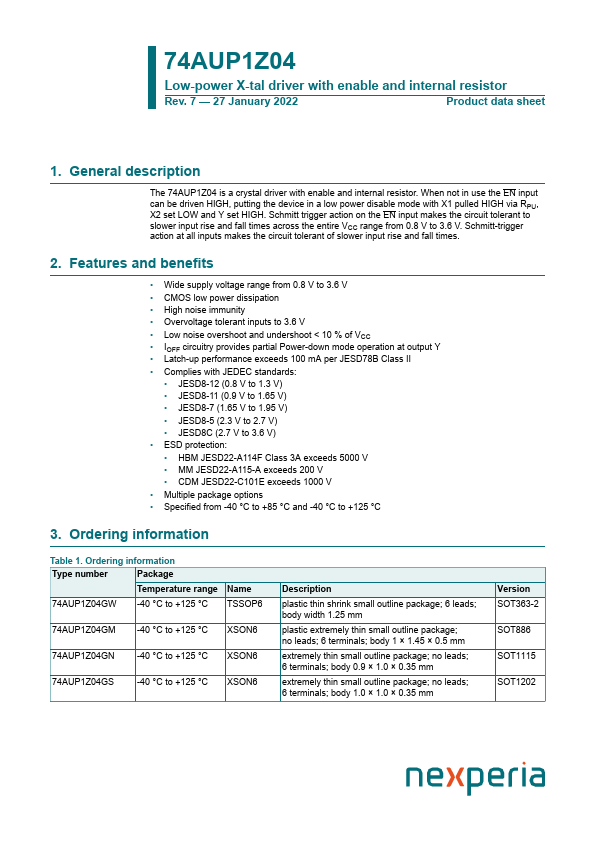

74AUP1Z04

Description

The 74AUP1Z04 is a crystal driver with enable and internal resistor. When not in use the EN input can be driven HIGH, putting the device in a low power disable mode with X1 pulled HIGH via RPU, X2 set LOW and Y set HIGH.

Key Features

- Wide supply voltage range from 0.8 V to 3.6 V

- CMOS low power dissipation

- High noise immunity

- Overvoltage tolerant inputs to 3.6 V

- Low noise overshoot and undershoot < 10 % of VCC

- IOFF circuitry provides partial Power-down mode operation at output Y

- Latch-up performance exceeds 100 mA per JESD78B Class II

- complies with JEDEC standards

- JESD8C (2.7 V to 3.6 V)

- ESD protection