Datasheet Summary

16-bit edge triggered D-type flip-flop; 3.6 V tolerant; 3-state

Rev. 3

- 16 August 2013

Product data sheet

1. General description

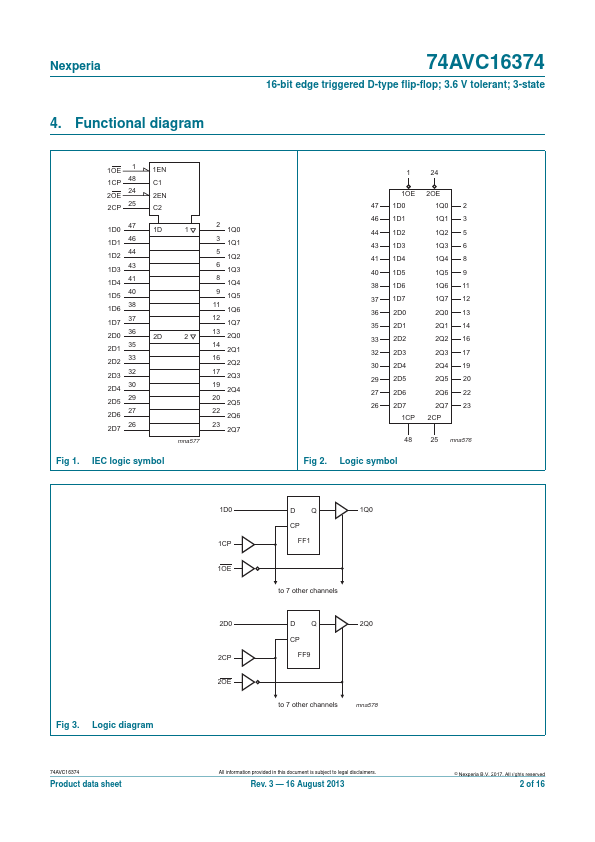

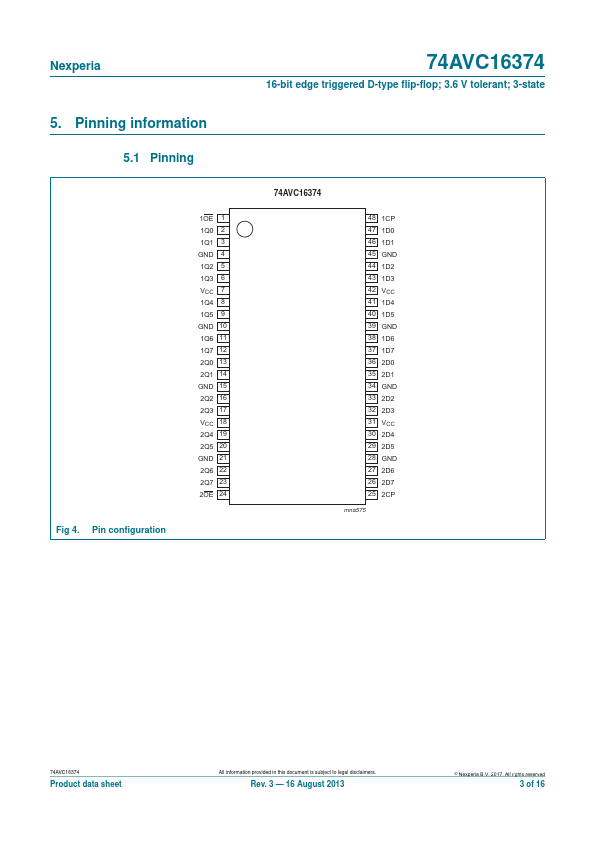

The 74AVC16374 is a 16-bit edge triggered flip-flop featuring separate D-type inputs for each flip-flop and 3-state outputs for bus-oriented applications. The 74AVC16374 consist of 2 sections of 8 edge-triggered flip-flops. A clock input (CP) and an output enable (OE) are provided per 8-bit section.

The 74AVC16374 is designed to have an extremely fast propagation delay and a minimum amount of power consumption.

To ensure the high-impedance output state during power-up or power-down, nOE should be tied to VCC through a pull-up resistor (Live...