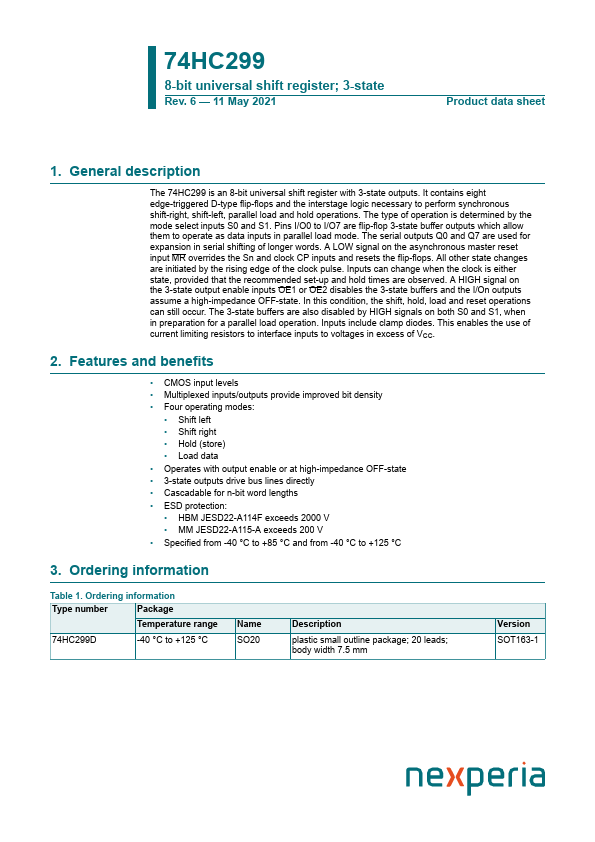

74HC299D

Overview

The 74HC299 is an 8-bit universal shift register with 3-state outputs. It contains eight edge-triggered D-type flip-flops and the interstage logic necessary to perform synchronous shift-right, shift-left, parallel load and hold operations.

- CMOS input levels

- Multiplexed inputs/outputs provide improved bit density

- Four operating modes:

- Shift left

- Shift right

- Hold (store)

- Load data

- Operates with output enable or at high-impedance OFF-state

- 3-state outputs drive bus lines directly

- Cascadable for n-bit word lengths