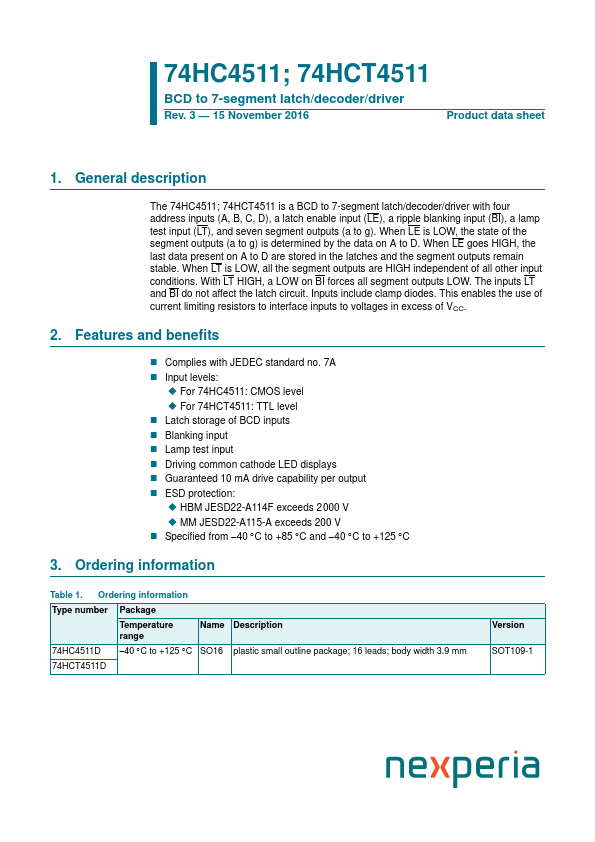

74HC4511D

Overview

The 74HC4511; 74HCT4511 is a BCD to 7-segment latch/decoder/driver with four address inputs (A, B, C, D), a latch enable input (LE), a ripple blanking input (BI), a lamp test input (LT), and seven segment outputs (a to g). When LE is LOW, the state of the segment outputs (a to g) is determined by the data on A to D.

- Complies with JEDEC standard no. 7A

- Input levels:; For 74HC4511: CMOS level; For 74HCT4511: TTL level

- Latch storage of BCD inputs

- Blanking input

- Lamp test input

- Driving common cathode LED displays

- Guaranteed 10 mA drive capability per output

- ESD protection:; HBM JESD22-A114F exceeds 2000 V; MM JESD22-A115-A exceeds 200 V

- Specified from -40 °C to +85 °C and -40 °C to +125 °C