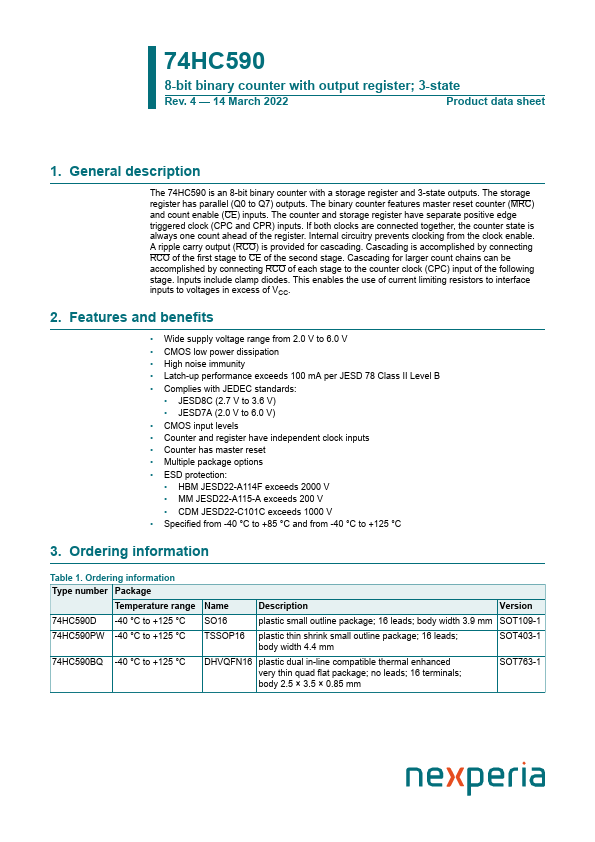

74HC590D

Description

The 74HC590 is an 8-bit binary counter with a storage register and 3-state outputs. The storage register has parallel (Q0 to Q7) outputs.

Key Features

- Wide supply voltage range from 2.0 V to 6.0 V

- CMOS low power dissipation

- High noise immunity

- Latch-up performance exceeds 100 mA per JESD 78 Class II Level B

- complies with JEDEC standards

- JESD8C (2.7 V to 3.6 V)

- JESD7A (2.0 V to 6.0 V)

- CMOS input levels

- Counter and register have independent clock inputs

- Counter has master reset