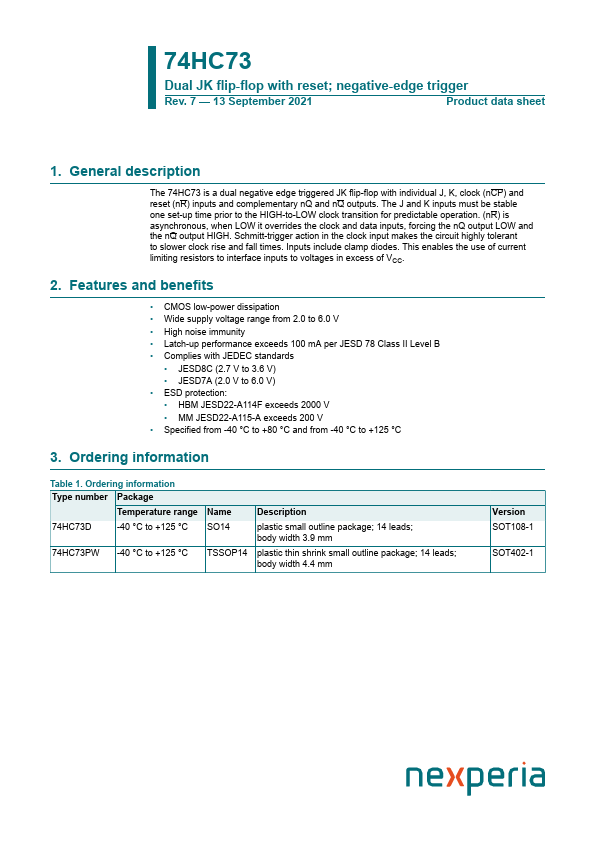

74HC73D

74HC73D is Dual JK flip-flop manufactured by Nexperia.

- Part of the 74HC73 comparator family.

- Part of the 74HC73 comparator family.

74HC73

Dual JK flip-flop with reset; negative-edge trigger

Rev. 7

- 13 September 2021

Product data sheet

1. General description

The 74HC73 is a dual negative edge triggered JK flip-flop with individual J, K, clock (nCP) and reset (nR) inputs and plementary nQ and nQ outputs. The J and K inputs must be stable one set-up time prior to the HIGH-to-LOW clock transition for predictable operation. (nR) is asynchronous, when LOW it overrides the clock and data inputs, forcing the nQ output LOW and the nQ output HIGH. Schmitt-trigger action in the clock input makes the circuit highly tolerant to slower clock rise and fall times. Inputs include clamp diodes. This enables the use of current...