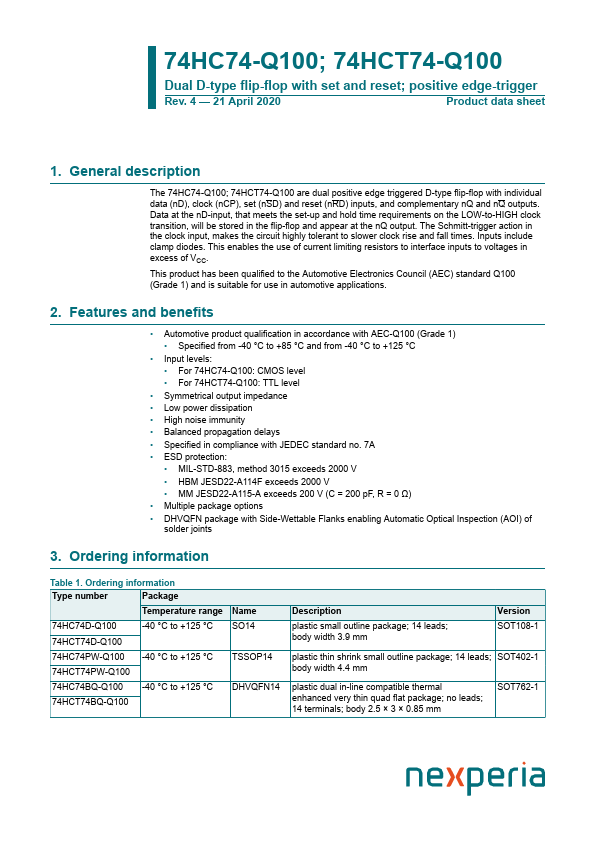

74HC74-Q100

Description

The 74HC74-Q100; 74HCT74-Q100 are dual positive edge triggered D-type flip-flop with individual data (nD), clock (nCP), set (nSD) and reset (nRD) inputs, and plementary nQ and nQ outputs. Data at the nD-input, that meets the set-up and hold time requirements on the LOW-to-HIGH clock transition, will be stored in the flip-flop and appear at the nQ output.

Key Features

- Automotive product qualification in accordance with AEC-Q100 (Grade

- Specified from -40 °C to +85 °C and from -40 °C to +125 °C

- Input levels

- For 74HC74-Q100: CMOS level

- For 74HCT74-Q100: TTL level

- Symmetrical output impedance

- Low power dissipation

- High noise immunity

- Balanced propagation delays

- Specified in pliance with JEDEC standard no. 7A