74HC75D

description

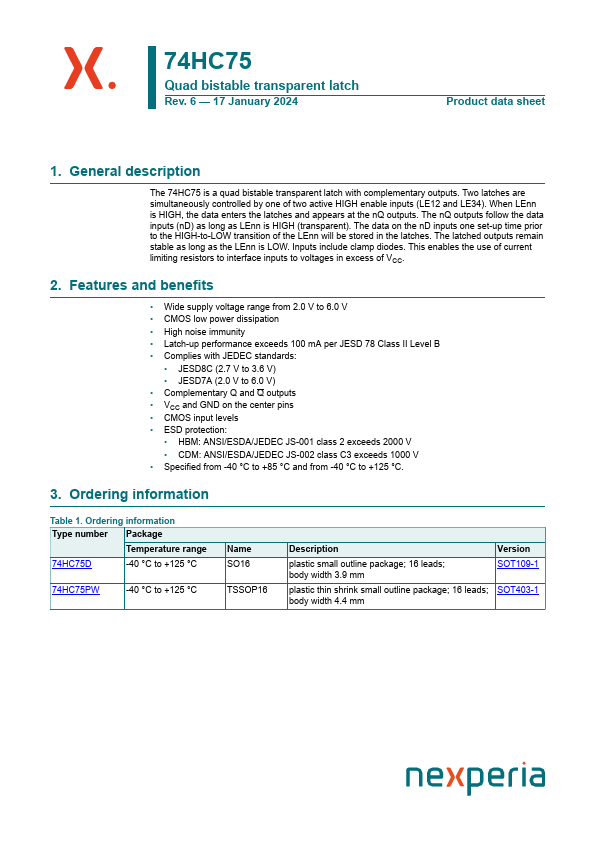

The 74HC75 is a quad bistable transparent latch with plementary outputs. Two latches are simultaneously controlled by one of two active HIGH enable inputs (LE12 and LE34). When LEnn is HIGH, the data enters the latches and appears at the n Q outputs. The n Q outputs follow the data inputs (n D) as long as LEnn is HIGH (transparent). The data on the n D inputs one set-up time prior to the HIGH-to-LOW transition of the LEnn will be stored in the latches. The latched outputs remain stable as long as the LEnn is LOW. Inputs include clamp diodes. This enables the use of current limiting resistors to interface inputs to voltages in excess of VCC.

2. Features and benefits

- Wide supply voltage range from 2.0 V to 6.0 V

- CMOS low power dissipation

- High noise immunity

- Latch-up performance exceeds 100 m A per JESD 78 Class II Level B

- plies with JEDEC standards:

- JESD8C (2.7 V to 3.6 V)

- JESD7A (2.0 V to 6.0 V)

- plementary Q and Q outputs

- VCC and GND on the center pins

- CMOS...