74HCT1G02

74HCT1G02 is 2-input NOR gate manufactured by Nexperia.

- Part of the 74HC1G02 comparator family.

- Part of the 74HC1G02 comparator family.

description

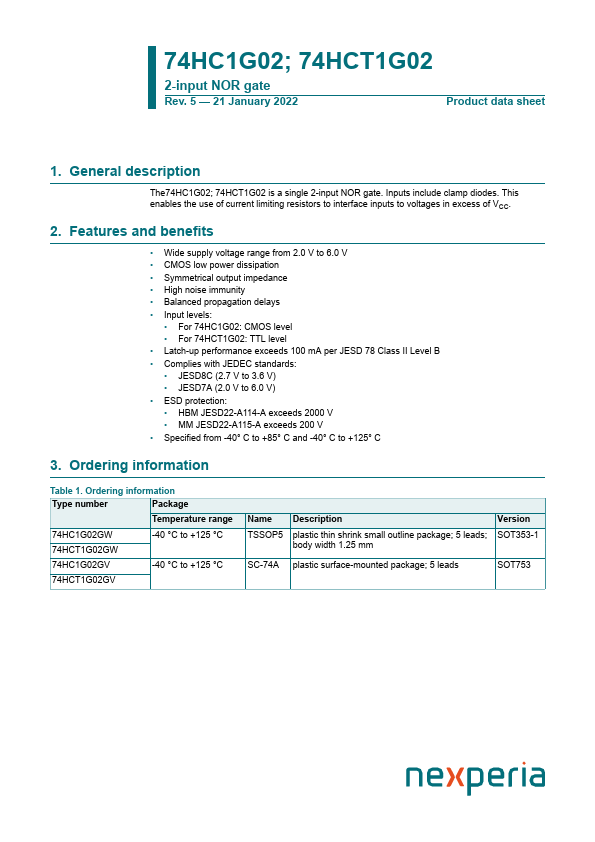

The74HC1G02; 74HCT1G02 is a single 2-input NOR gate. Inputs include clamp diodes. This enables the use of current limiting resistors to interface inputs to voltages in excess of VCC.

2. Features and benefits

- Wide supply voltage range from 2.0 V to 6.0 V

- CMOS low power dissipation

- Symmetrical output impedance

- High noise immunity

- Balanced propagation delays

- Input levels:

- For 74HC1G02: CMOS level

- For 74HCT1G02: TTL level

- Latch-up performance exceeds 100 m A per JESD 78 Class II Level B

- plies with JEDEC standards:

- JESD8C (2.7 V to 3.6 V)

- JESD7A (2.0 V to 6.0 V)

- ESD protection:

- HBM JESD22-A114-A exceeds 2000 V

- MM JESD22-A115-A exceeds 200 V

- Specified from -40° C to +85° C and -40° C to +125° C

3. Ordering information

Table 1. Ordering information

Type number

Package

Temperature range

74HC1G02GW

-40 °C to +125 °C

74HCT1G02GW

74HC1G02GV

-40 °C to +125 °C

74HCT1G02GV

Name TSSOP5

Description plastic thin shrink small outline package; 5 leads; body width 1.25 mm

Version SOT353-1

SC-74A plastic surface-mounted package; 5 leads

SOT753

Nexperia

74HC1G02; 74HCT1G02

2-input NOR gate

4. Marking

Table 2. Marking codes Type number 74HC1G02GW 74HCT1G02GW 74HC1G02GV...