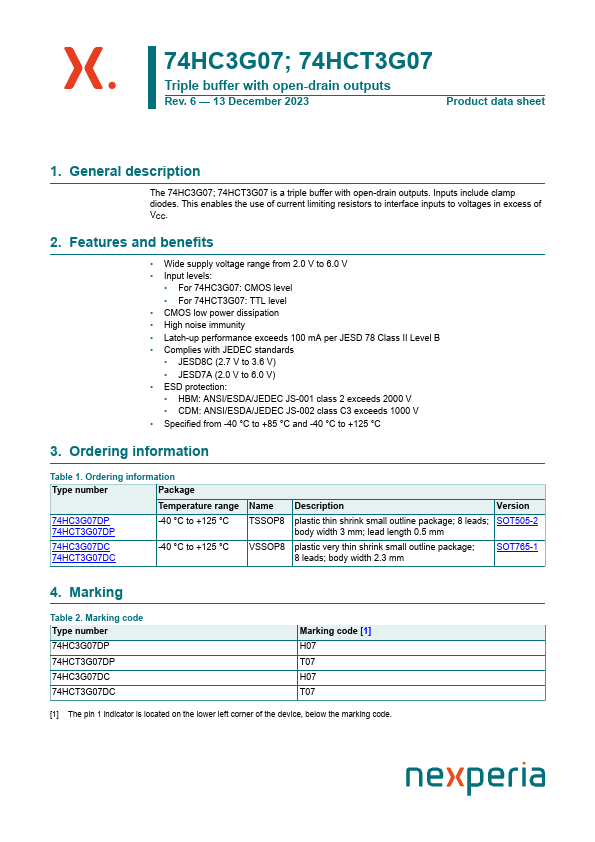

74HCT3G07DP Overview

Key Specifications

Package: TSSOP

Mount Type: Surface Mount

Pins: 8

Operating Voltage: 5 V

Description

The 74HC3G07; 74HCT3G07 is a triple buffer with open-drain outputs. Inputs include clamp diodes.

Key Features

- Wide supply voltage range from 2.0 V to 6.0 V

- Input levels

- For 74HC3G07: CMOS level

- For 74HCT3G07: TTL level

- CMOS low power dissipation