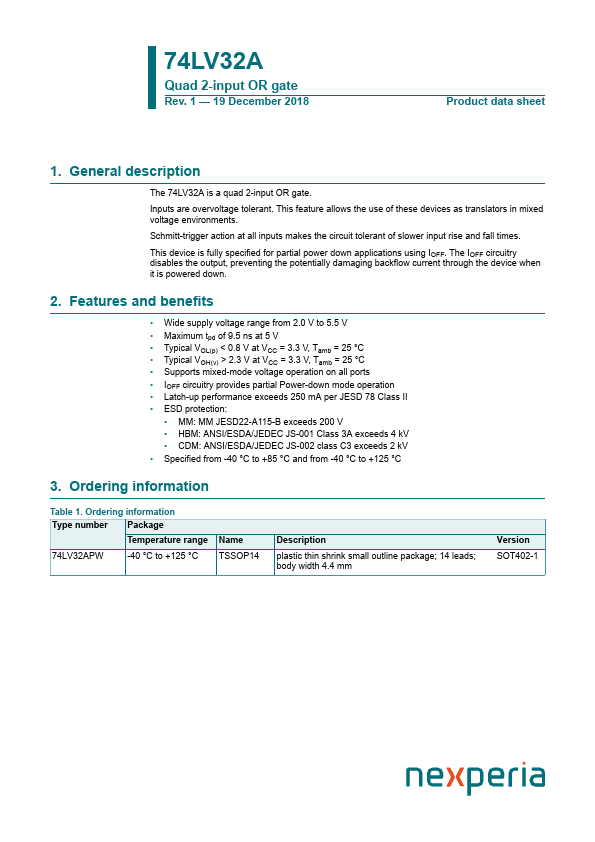

74LV32A

74LV32A is Quad 2-input OR gate manufactured by Nexperia.

Quad 2-input OR gate

Rev. 1

- 19 December 2018

Product data sheet

1. General description

The 74LV32A is a quad 2-input OR gate.

Inputs are overvoltage tolerant. This feature allows the use of these devices as translators in mixed voltage environments.

Schmitt-trigger action at all inputs makes the circuit tolerant of slower input rise and fall times.

This device is fully specified for partial power down applications using IOFF. The IOFF circuitry disables the output, preventing the potentially damaging backflow current through the device when it is powered down.

2. Features and benefits

- Wide supply voltage range from 2.0 V to 5.5 V

- Maximum tpd of 9.5 ns at 5 V

- Typical...