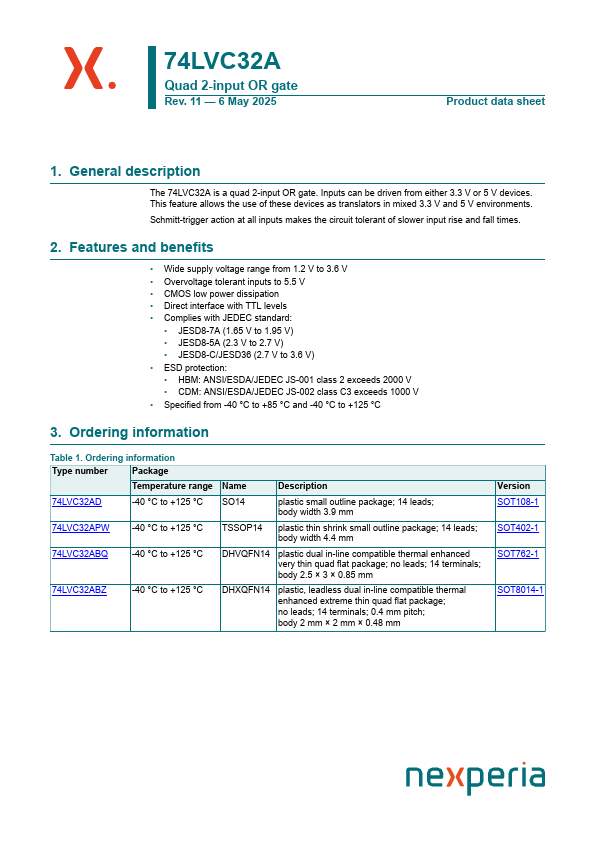

74LVC32AD

Overview

The 74LVC32A is a quad 2-input OR gate. Inputs can be driven from either 3.3 V or 5 V devices.

- Features and benefits

- Wide supply voltage range from 1.2 V to 3.6 V

- Overvoltage tolerant inputs to 5.5 V

- CMOS low power dissipation

- Direct interface with TTL levels

- Complies with JEDEC standard:

- JESD8-7A (1.65 V to 1.95 V)

- JESD8-5A (2.3 V to 2.7 V)

- JESD8-C/JESD36 (2.7 V to 3.6 V)

- ESD protection: