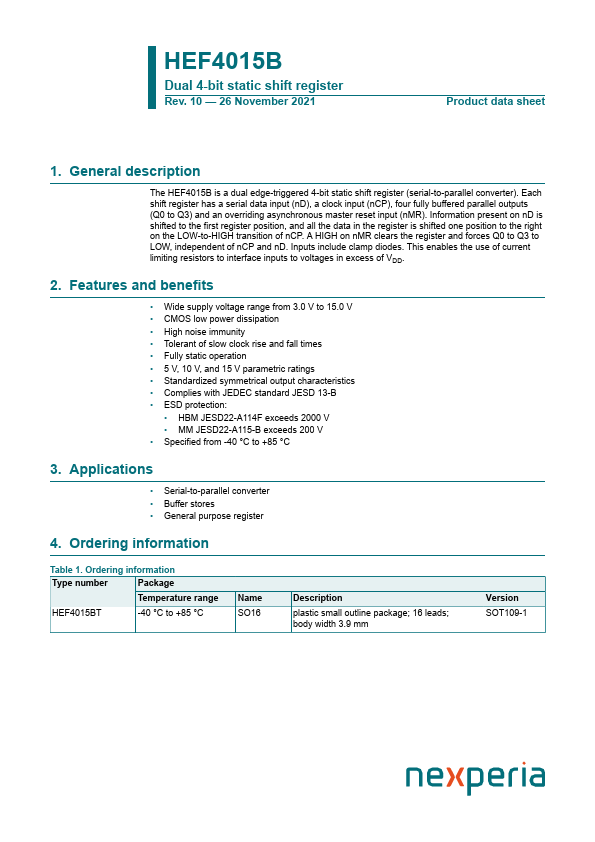

HEF4015B

Description

The HEF4015B is a dual edge-triggered 4-bit static shift register (serial-to-parallel converter).

Key Features

- Wide supply voltage range from 3.0 V to 15.0 V

- CMOS low power dissipation

- High noise immunity

- Tolerant of slow clock rise and fall times

- Fully static operation

- 5 V, 10 V, and 15 V parametric ratings

- Standardized symmetrical output characteristics

- plies with JEDEC standard JESD 13-B

- ESD protection

- HBM JESD22-A114F exceeds 2000 V

Applications

- Serial-to-parallel converter