HEF40175B

Description

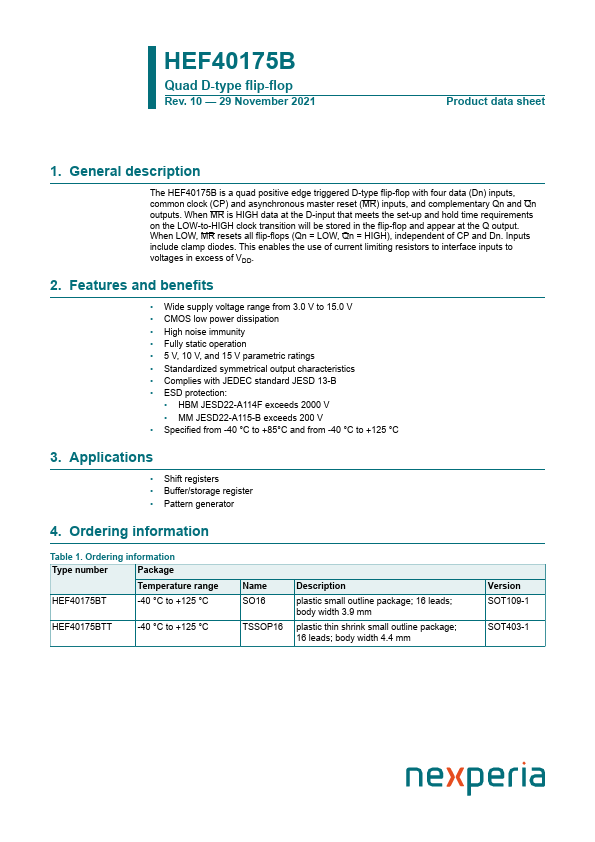

The HEF40175B is a quad positive edge triggered D-type flip-flop with four data (Dn) inputs, common clock (CP) and asynchronous master reset (MR) inputs, and complementary Qn and Qn outputs. When MR is HIGH data at the D-input that meets the set-up and hold time requirements on the LOW-to-HIGH clock transition will be stored in the flip-flop and appear at the Q output.

Key Features

- Wide supply voltage range from 3.0 V to 15.0 V

- CMOS low power dissipation

- High noise immunity

- Fully static operation

- 5 V, 10 V, and 15 V parametric ratings

- Standardized symmetrical output characteristics

- Complies with JEDEC standard JESD 13-B

- ESD protection:

- HBM JESD22-A114F exceeds 2000 V

- MM JESD22-A115-B exceeds 200 V