SN54LS73A Datasheet

SN54LS73A Datasheet (Motorola Semiconductor)

Motorola Semiconductor

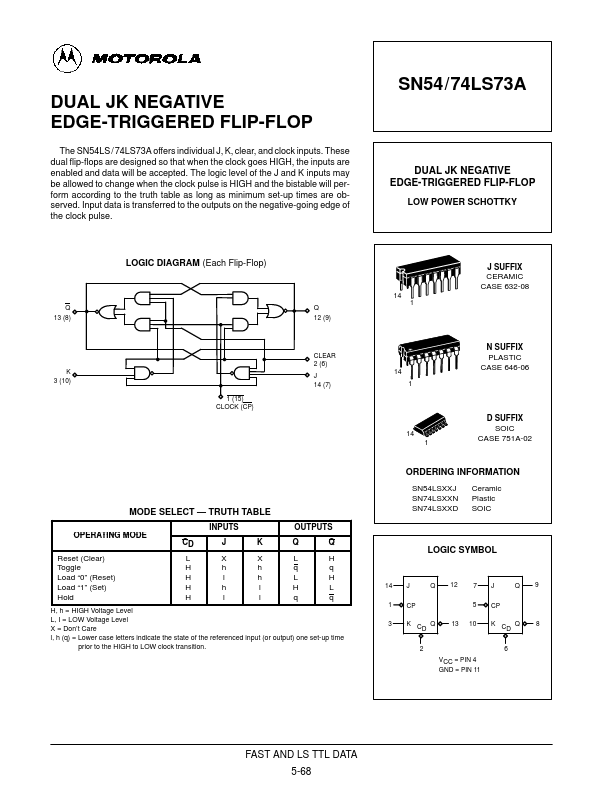

SN54/74LS73A DUAL JK NEGATIVE EDGE-TRIGGERED FLIP-FLOP The SN54LS / 74LS73A offers individual J, K, clear, and clock inputs. These dual flip-flops are designed so that when the clock goes HIGH, the in.

et) Load “1” (Set) Hold L H H H H J X h l h l LOGIC SYMBOL 14 1 3 J CP Q 12 7 5 J CP Q 9 H, h = HIGH Voltage Level L, I = LOW Voltage Level X = Don’t Care l, h (q) = Lower case letters indicate the state of the referenced input (or output) one set-up time l, h (q) = prior to the HIGH to LO.

SN54LS73A Datasheet (Texas Instruments)

Texas Instruments

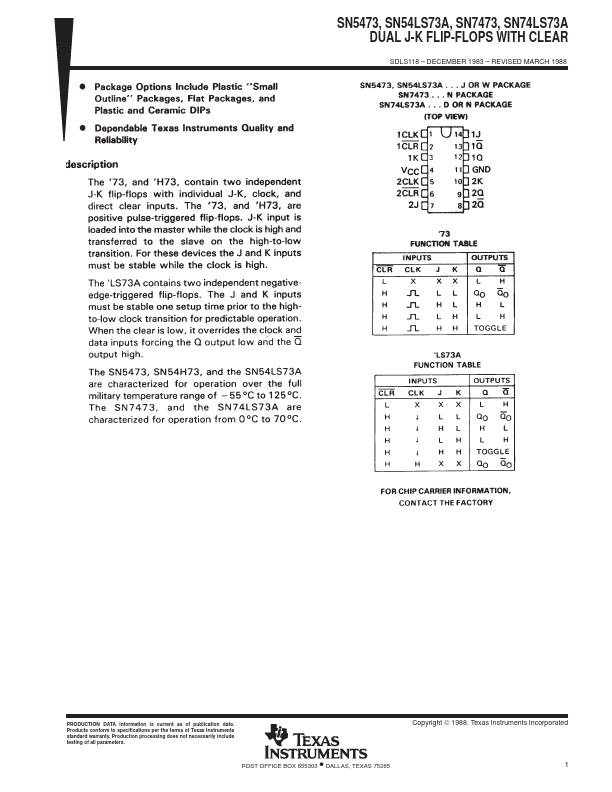

SN5473, SN54LS73A, SN7473, SN74LS73A DUAL J-K FLIP-FLOPS WITH CLEAR SDLS118 – DECEMBER 1983 – REVISED MARCH 1988 PRODUCTION DATA information is current as of publication date. Products conform to spe.

DLS118

* DECEMBER 1983

* REVISED MARCH 1988

* POST OFFICE BOX 655303 DALLAS, TEXAS 75265

5

PACKAGE OPTION ADDENDUM

PACKAGING INFORMATION

Orderable Device 5962-9675101QCA

Status Package Type Package Pins Package Eco Plan

(1)

Drawing

Qty

(2)

ACTIVE

CDIP

J

14

1

Non-RoHS &

N.