SN54LS77 Datasheet

SN54LS77 Datasheet (Motorola Semiconductor)

Motorola Semiconductor

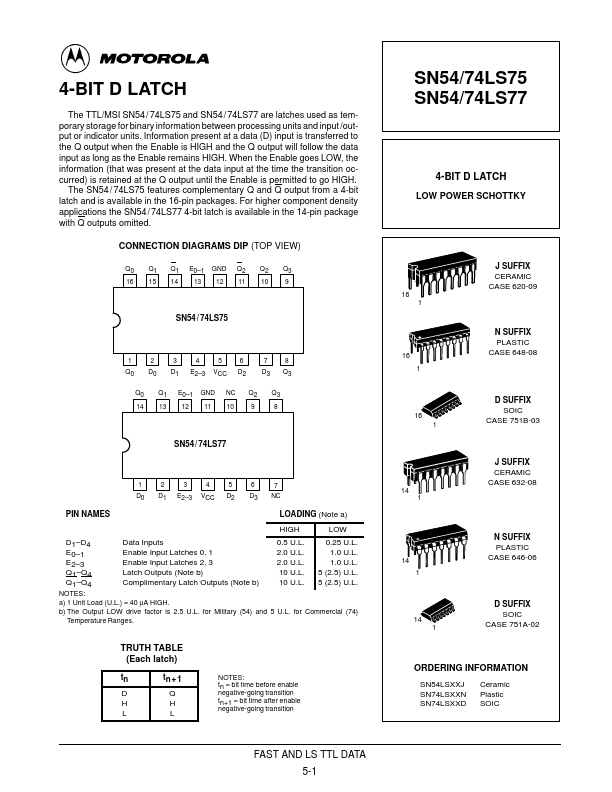

4-BIT D LATCH The TTL/MSI SN54 / 74LS75 and SN54 / 74LS77 are latches used as temporary storage for binary information between processing units and input /output or indicator units. Information presen.

complementary Q and Q output from a 4-bit latch and is available in the 16-pin packages. For higher component density applications the SN54 / 74LS77 4-bit latch is available in the 14-pin package with Q outputs omitted. CONNECTION DIAGRAMS DIP (TOP VIEW)

Q0 16 Q1 15 Q1 14 E0

*1 GND 13 12 Q2 11 Q2 10 .

SN54LS77 Datasheet (Texas Instruments)

Texas Instruments

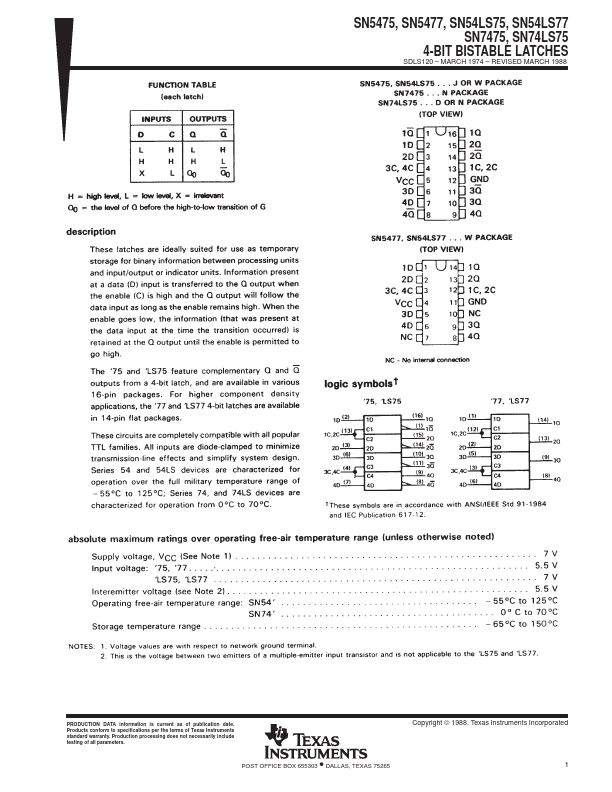

SN5475, SN5477, SN54LS75, SN54LS77 SN7475, SN74LS75 4-BIT BISTABLE LATCHES SDLS120 – MARCH 1974 – REVISED MARCH 1988 PRODUCTION DATA information is current as of publication date. Products conform to.

-BIT BISTABLE LATCHES

SDLS120

* MARCH 1974

* REVISED MARCH 1988

* POST OFFICE BOX 655303 DALLAS, TEXAS 75265

5

TAPE AND REEL INFORMATION

PACKAGE MATERIALS INFORMATION

14-Jul-2012

*All dimensions are nominal

Device

Package Package Pins Type Drawing

SN74LS75DR SN74LS75NSR

SOIC SO

.