# PIC12C5XX

## 8-Pin, 8-Bit CMOS Microcontrollers

#### Devices included in this Data Sheet:

- PIC12C508 PIC12C508A PIC12CE518

- PIC12C509 PIC12C509A PIC12CE519

- PIC12CR509A

- Note: Throughout this data sheet PIC12C5XX refers to the PIC12C508, PIC12C509, PIC12C508A, PIC12C509A, PIC12CR509A, PIC12CE518 and PIC12CE519. PIC12CE5XX refers to PIC12CE518 and PIC12CE519.

#### High-Performance RISC CPU:

- Only 33 single word instructions to learn

- All instructions are single cycle (1 µs) except for program branches which are two-cycle

- Operating speed: DC 4 MHz clock input DC - 1 μs instruction cycle

|             |                  | •              |             |                |  |  |  |  |  |  |  |

|-------------|------------------|----------------|-------------|----------------|--|--|--|--|--|--|--|

|             | Memory           |                |             |                |  |  |  |  |  |  |  |

| Device      | EPROM<br>Program | ROM<br>Program | RAM<br>Data | EEPROM<br>Data |  |  |  |  |  |  |  |

| PIC12C508   | 512 x 12         |                | 25          |                |  |  |  |  |  |  |  |

| PIC12C508A  | 512 x 12         |                | 25          |                |  |  |  |  |  |  |  |

| PIC12C509   | 1024 x 12        |                | 41          |                |  |  |  |  |  |  |  |

| PIC12C509A  | 1024 x 12        |                | 41          |                |  |  |  |  |  |  |  |

| PIC12CE518  | 512 x 12         |                | 25          | 16             |  |  |  |  |  |  |  |

| PIC12CE519  | 1024 x 12        |                | 41          | 16             |  |  |  |  |  |  |  |

| PIC12CR509A |                  | 1024 x 12      | 41          |                |  |  |  |  |  |  |  |

12-bit wide instructions

- 8-bit wide data path

- Seven special function hardware registers

- Two-level deep hardware stack

- Direct, indirect and relative addressing modes for data and instructions

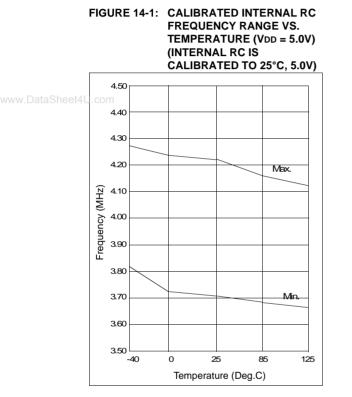

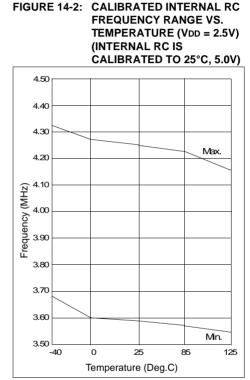

- Internal 4 MHz RC oscillator with programmable calibration

- · In-circuit serial programming

#### **Peripheral Features:**

- 8-bit real time clock/counter (TMR0) with 8-bit programmable prescaler

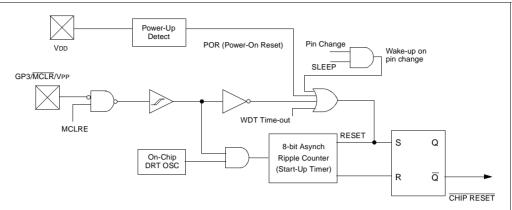

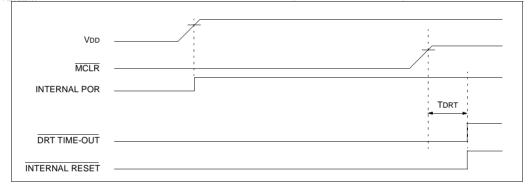

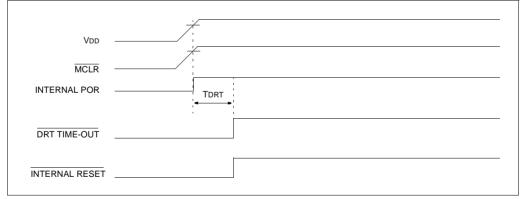

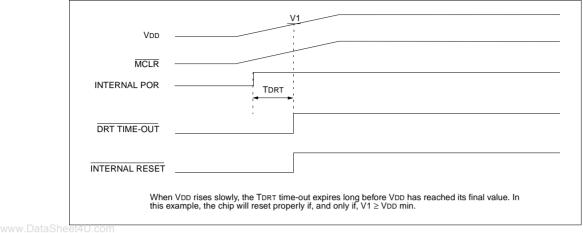

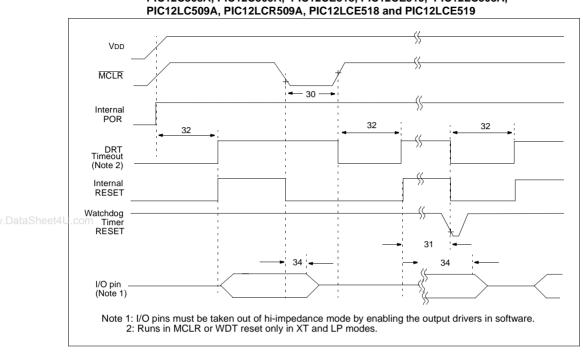

- Power-On Reset (POR)

- Device Reset Timer (DRT)

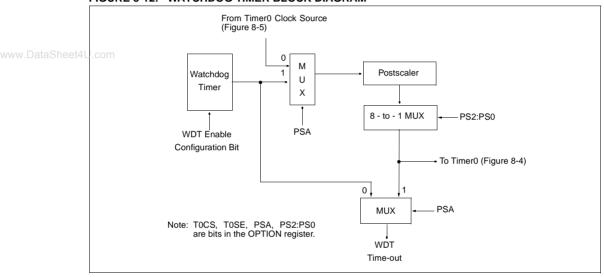

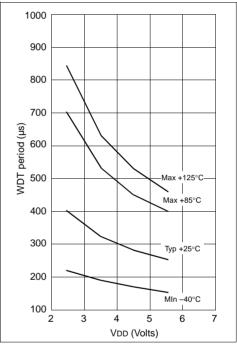

- Watchdog Timer (WDT) with its own on-chip RC oscillator for reliable operation

- · Programmable code-protection

- 1,000,000 erase/write cycle EEPROM data memory

- EEPROM data retention > 40 years

- · Power saving SLEEP mode

- · Wake-up from SLEEP on pin change

- Internal weak pull-ups on I/O pins

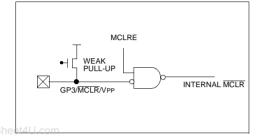

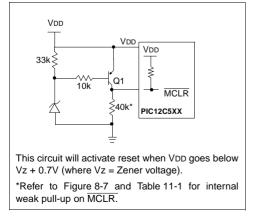

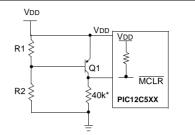

- Internal pull-up on MCLR pin

- Selectable oscillator options:

- INTRC: Internal 4 MHz RC oscillator

- EXTRC: External low-cost RC oscillator

- XT: Standard crystal/resonator

- LP: Power saving, low frequency crystal

#### CMOS Technology:

- Low power, high speed CMOS EPROM/ROM technology

- · Fully static design

- · Wide operating voltage range

- Wide temperature range:

- Commercial: 0°C to +70°C

- Industrial: -40°C to +85°C

- Extended: -40°C to +125°C

- Low power consumption

- < 2 mA @ 5V, 4 MHz

- 15  $\mu\text{A}$  typical @ 3V, 32 KHz

- < 1 µA typical standby current

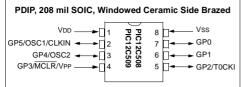

#### Pin Diagram - PIC12C508/509

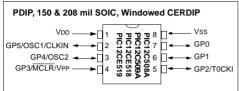

#### Pin Diagram - PIC12C508A/509A, PIC12CE518/519

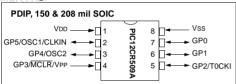

#### Pin Diagram - PIC12CR509A

#### **Device Differences**

| Device      | Voltage<br>Range | Oscillator | Oscillator<br>Calibration <sup>2</sup><br>(Bits) | Process<br>Technology<br>(Microns) |

|-------------|------------------|------------|--------------------------------------------------|------------------------------------|

| PIC12C508A  | 3.0-5.5          | See Note 1 | 6                                                | 0.7                                |

| PIC12LC508A | 2.5-5.5          | See Note 1 | 6                                                | 0.7                                |

| PIC12C508   | 2.5-5.5          | See Note 1 | 4                                                | 0.9                                |

| PIC12C509A  | 3.0-5.5          | See Note 1 | 6                                                | 0.7                                |

| PIC12LC509A | 2.5-5.5          | See Note 1 | 6                                                | 0.7                                |

| PIC12C509   | 2.5-5.5          | See Note 1 | 4                                                | 0.9                                |

| PIC12CR509A | 2.5-5.5          | See Note 1 | 6                                                | 0.7                                |

| PIC12CE518  | 3.0-5.5          | -          | 6                                                | 0.7                                |

| PIC12LCE518 | 2.5-5.5          | -          | 6                                                | 0.7                                |

| PIC12CE519  | 3.0-5.5          | -          | 6                                                | 0.7                                |

| PIC12LCE519 | 2.5-5.5          | -          | 6                                                | 0.7                                |

**Note 1:** If you change from the PIC12C50X to the PIC12C50XA or to the PIC12CR50XA, please verify oscillator characteristics in your application.

Note 2: See Section 7.2.5 for OSCCAL implementation differences.

#### TABLE OF CONTENTS

|      | 1.0   | General Description                                                                   | 4   |

|------|-------|---------------------------------------------------------------------------------------|-----|

|      | 2.0   | PIC12C5XX Device Varieties                                                            | 7   |

|      | 3.0   | Architectural Overview                                                                | 9   |

|      | 4.0   | Memory Organization                                                                   | 13  |

|      | 5.0   | I/O Port                                                                              |     |

|      | 6.0   | Timer0 Module and TMR0 Register                                                       |     |

|      | 7.0   | EEPROM Peripheral Operation                                                           |     |

|      | 8.0   | Special Features of the CPU                                                           |     |

|      | 9.0   | Instruction Set Summary                                                               | 47  |

|      | 10.0  | Development Support                                                                   | 59  |

|      | 11.0  | Electrical Characteristics - PIC12C508/PIC12C509                                      | 65  |

|      | 12.0  | DC and AC Characteristics - PIC12C508/PIC12C509                                       | 75  |

|      |       | Electrical Characteristics PIC12C508A/PIC12C509A/PIC12LC508A/PIC12LC509A/PIC12CR509A/ |     |

|      |       | PIC12CE518/PIC12CE519/                                                                |     |

|      |       | PIC12LCE518/PIC12LCE519/PIC12LCR509A                                                  | 79  |

|      | 14.0  | DC and AC Characteristics                                                             |     |

|      |       | PIC12C508A/PIC12C509A/PIC12LC508A/PIC12LC509A/PIC12CE518/PIC12CE519/PIC12CR509A/      |     |

|      |       | PIC12LCE518/PIC12LCE519/ PIC12LCR509A                                                 | 93  |

| ot/1 | 15.0  | Packaging Information                                                                 |     |

|      |       |                                                                                       |     |

|      |       | 2C5XX Product Identification System                                                   |     |

|      |       | and Support:                                                                          |     |

|      | Jales | anu ouppon                                                                            | 109 |

#### To Our Valued Customers

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number. e.g., DS30000A is version A of document DS30000.

#### Errata

An errata sheet may exist for current devices, describing minor operational differences (from the data sheet) and recommended workarounds. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (602) 786-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Corrections to this Data Sheet**

We constantly strive to improve the quality of all our products and documentation. We have spent a great deal of time to ensure that this document is correct. However, we realize that we may have missed a few things. If you find any information that is missing or appears in error, please:

- Fill out and mail in the reader response form in the back of this data sheet.

- E-mail us at webmaster@microchip.com.

We appreciate your assistance in making this a better document.

### 1.0 GENERAL DESCRIPTION

The PIC12C5XX from Microchip Technology is a family of low-cost, high performance, 8-bit, fully static, EEPROM/EPROM/ROM-based CMOS microcontrollers. It employs a RISC architecture with only 33 single word/single cycle instructions. All instructions are single cycle (1 µs) except for program branches which take two cycles. The PIC12C5XX delivers performance an order of magnitude higher than its competitors in the same price category. The 12-bit wide instructions are highly symmetrical resulting in 2:1 code compression over other 8-bit microcontrollers in its class. The easy to use and easy to remember instruction set reduces development time significantly.

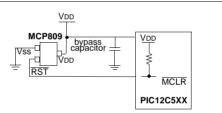

The PIC12C5XX products are equipped with special features that reduce system cost and power requirements. The Power-On Reset (POR) and Device Reset Timer (DRT) eliminate the need for external reset circuitry. There are four oscillator configurations to choose from, including INTRC internal oscillator mode and the power-saving LP (Low Power) oscillator mode. Power saving SLEEP mode, Watchdog Timer and code protection features also improve system cost, power and reliability.

The PIC12C5XX are available in the cost-effective One-Time-Programmable (OTP) versions which are suitable for production in any volume. The customer can take full advantage of Microchip's price leadership in OTP microcontrollers while benefiting from the OTP's flexibility.

The PIC12C5XX products are supported by a full-featured macro assembler, a software simulator, an in-circuit emulator, a 'C' compiler, fuzzy logic support tools, a low-cost development programmer, and a full featured programmer. All the tools are supported on IBM<sup>®</sup> PC and compatible machines.

#### 1.1 Applications

The PIC12C5XX series fits perfectly in applications ranging from personal care appliances and security systems to low-power remote transmitters/receivers. The EPROM technology makes customizing application programs (transmitter codes, appliance settings, receiver frequencies. etc.) extremely fast and convenient, while the EEPROM data memory technology allows for the changing of calibration factors and security codes. The small footprint packages, for through hole or surface mounting, make this microcontroller series perfect for applications with space limitations. Low-cost, low-power, high performance, ease of use and I/O flexibility make the PIC12C5XX series very versatile even in areas where no microcontroller use has been considered before (e.g., timer functions, replacement of "glue" logic and PLD's in larger systems, coprocessor applications).

|             |                                               | PIC12C508(A)           | PIC12C509(A)           | PIC12CR509A        | PIC12CE518             | PIC12CE519             | PIC12C671              | PIC12C672              | PIC12CE673       | PIC12CE         |

|-------------|-----------------------------------------------|------------------------|------------------------|--------------------|------------------------|------------------------|------------------------|------------------------|------------------|-----------------|

| Clock       | Maximum<br>Frequency<br>of Operation<br>(MHz) | 4                      | 4                      | 4                  | 4                      | 4                      | 10                     | 10                     | 10               | 10              |

| Mamaan      | EPROM<br>Program<br>Memory                    | 512 x 12               | 1024 x 12              | 1024 x 12<br>(ROM) | 512 x 12               | 1024 x 12              | 1024 x 14              | 2048 x 14              | 1024 x 14        | 2048 x 1        |

| Memory      | RAM Data<br>Memory<br>(bytes)                 | 25                     | 41                     | 41                 | 25                     | 41                     | 128                    | 128                    | 128              | 128             |

|             | EEPROM<br>Data Memory<br>(bytes)              | —                      | —                      | —                  | 16                     | 16                     | —                      | —                      | 16               | 16              |

| Peripherals | Timer<br>Module(s)                            | TMR0                   | TMR0                   | TMR0               | TMR0                   | TMR0                   | TMR0                   | TMR0                   | TMR0             | TMR0            |

|             | A/D Con-<br>verter (8-bit)<br>Channels        | —                      | _                      | —                  | _                      | -                      | 4                      | 4                      | 4                | 4               |

| J.com       | Wake-up<br>from SLEEP<br>on pin<br>change     | Yes                    | Yes                    | Yes                | Yes                    | Yes                    | Yes                    | Yes                    | Yes              | Yes             |

| 0.0011      | Interrupt<br>Sources                          | —                      | —                      | —                  |                        |                        | 4                      | 4                      | 4                | 4               |

| Features    | I/O Pins                                      | 5                      | 5                      | 5                  | 5                      | 5                      | 5                      | 5                      | 5                | 5               |

|             | Input Pins                                    | 1                      | 1                      | 1                  | 1                      | 1                      | 1                      | 1                      | 1                | 1               |

|             | Internal<br>Pull-ups                          | Yes                    | Yes                    | Yes                | Yes                    | Yes                    | Yes                    | Yes                    | Yes              | Yes             |

|             | In-Circuit<br>Serial<br>Programming           | Yes                    | Yes                    | _                  | Yes                    | Yes                    | Yes                    | Yes                    | Yes              | Yes             |

|             | Number of<br>Instructions                     | 33                     | 33                     | 33                 | 33                     | 33                     | 35                     | 35                     | 35               | 35              |

|             | Packages                                      | 8-pin DIP,<br>JW, SOIC | 8-pin DIP,<br>JW, SOIC | 8-pin DIP,<br>SOIC | 8-pin DIP,<br>JW, SOIC | 8-pin DIP,<br>JW, SOIC | 8-pin DIP,<br>JW, SOIC | 8-pin DIP,<br>JW, SOIC | 8-pin DIP,<br>JW | 8-pin DIF<br>JW |

#### TABLE 1-1: PIC12CXXX & PIC12CEXXX FAMILY OF DEVICES

All PIC12CXXX & PIC12CEXXX devices have Power-on Reset, selectable Watchdog Timer, selectable code protect and high I/O current capability.

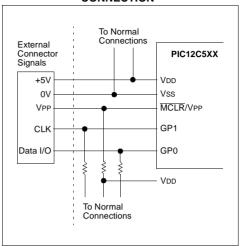

All PIC12CXXX & PIC12CEXXX devices use serial programming with data pin GP0 and clock pin GP1.

## PIC12C5XX

### NOTES:

www.DataSheet4U.com

### 2.0 PIC12C5XX DEVICE VARIETIES

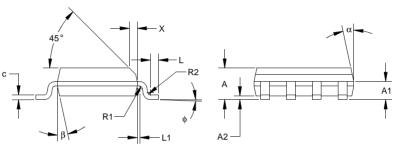

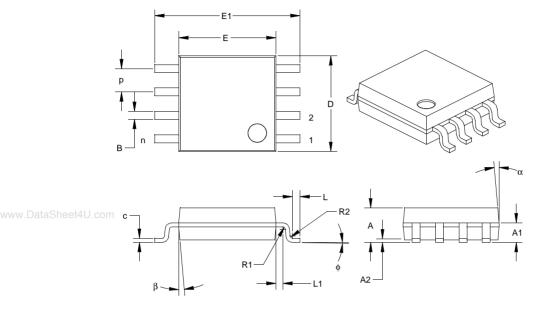

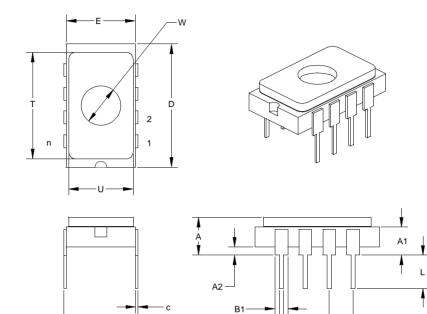

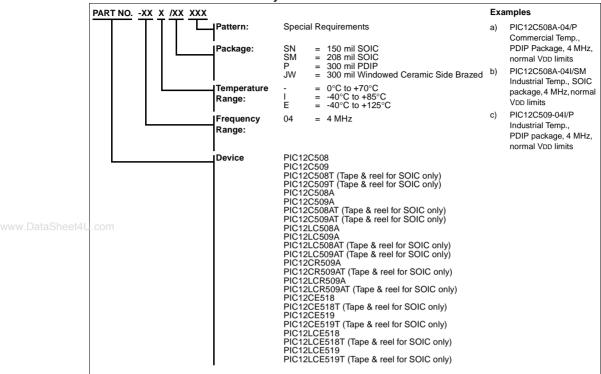

A variety of packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in this section. When placing orders, please use the PIC12C5XX Product Identification System at the back of this data sheet to specify the correct part number.

#### 2.1 UV Erasable Devices

The UV erasable version, offered in ceramic side brazed package, is optimal for prototype development and pilot programs.

The UV erasable version can be erased and reprogrammed to any of the configuration modes.

Note:

Please note that erasing the device will also erase the pre-programmed internal calibration value for the internal oscillator. The calibration value must be saved prior to erasing the part.

> Microchip's PICSTART<sup>®</sup> PLUS and PRO MATE<sup>®</sup> programmers all support programming of the PIC12C5XX. Third party programmers also are available; refer to the *Microchip Third Party Guide* for a list of sources.

#### 2.2 <u>One-Time-Programmable (OTP)</u> <u>Devices</u>

The availability of OTP devices is especially useful for customers who need the flexibility for frequent code updates or small volume applications.

The OTP devices, packaged in plastic packages permit the user to program them once. In addition to the program memory, the configuration bits must also be programmed.

#### 2.3 <u>Quick-Turnaround-Production (QTP)</u> <u>Devices</u>

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who choose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices are identical to the OTP devices but with all EPROM locations and fuse options already programmed by the factory. Certain code and prototype verification procedures do apply before production shipments are available. Please contact your local Microchip Technology sales office for more details.

#### 2.4 <u>Serialized Quick-Turnaround</u> <u>Production (SQTP<sup>SM</sup>) Devices</u>

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number which can serve as an entry-code, password or ID number.

#### 2.5 Read Only Memory (ROM) Device

Microchip offers masked ROM to give the customer a low cost option for high volume, mature products.

## PIC12C5XX

### NOTES:

www.DataSheet4U.com

### 3.0 ARCHITECTURAL OVERVIEW

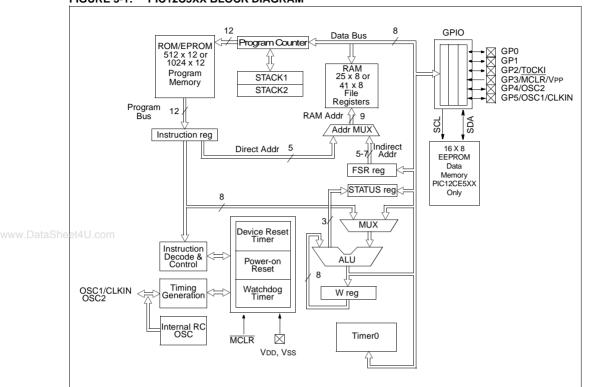

The high performance of the PIC12C5XX family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC12C5XX uses a Harvard architecture in which program and data are accessed on separate buses. This improves bandwidth over traditional von Neumann architecture where program and data are fetched on the same bus. Separating program and data memory further allows instructions to be sized differently than the 8-bit wide data word. Instruction opcodes are 12-bits wide making it possible to have all single word instructions. A 12-bit wide program memory access bus fetches a 12-bit instruction in a single cycle. A two-stage pipeline overlaps fetch and execution of instructions. Consequently, all instructions (33) execute in a single cycle (1µs @ 4MHz) except for program branches.

The table below lists program memory (EPROM), data memory (RAM), ROM memory, and non-volatile (EEPROM) for each device.

|             | Memory           |                |             |                |  |  |  |  |  |  |

|-------------|------------------|----------------|-------------|----------------|--|--|--|--|--|--|

| Device      | EPROM<br>Program | ROM<br>Program | RAM<br>Data | EEPROM<br>Data |  |  |  |  |  |  |

| PIC12C508   | 512 x 12         |                | 25          |                |  |  |  |  |  |  |

| PIC12C509   | 1024 x 12        |                | 41          |                |  |  |  |  |  |  |

| PIC12C508A  | 512 x 12         |                | 25          |                |  |  |  |  |  |  |

| PIC12C509A  | 1024 x 12        |                | 41          |                |  |  |  |  |  |  |

| PIC12CR509A |                  | 1024 x 12      | 41          |                |  |  |  |  |  |  |

| PIC12CE518  | 512 x 12         |                | 25 x 8      | 16 x 8         |  |  |  |  |  |  |

| PIC12CE519  | 1024 x 12        |                | 41 x 8      | 16 x 8         |  |  |  |  |  |  |

The PIC12C5XX can directly or indirectly address its register files and data memory. All special function registers including the program counter are mapped in the data memory. The PIC12C5XX has a highly orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC12C5XX simple yet efficient. In addition, the learning curve is reduced significantly.

The PIC12C5XX device contains an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the W (working) register. The other operand is either a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a borrow and digit borrow out bit, respectively, in subtraction. See the SUBWF and ADDWF instructions for examples.

A simplified block diagram is shown in Figure 3-1, with the corresponding device pins described in Table 3-1.

#### FIGURE 3-1: PIC12C5XX BLOCK DIAGRAM

|      | Name           | DIP<br>Pin # | SOIC<br>Pin # | I/O/P<br>Type | Buffer<br>Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------|----------------|--------------|---------------|---------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | GP0            | 7            | 7             | I/O           | TTL/ST         | Bi-directional I/O port/ serial programming data. Can<br>be software programmed for internal weak pull-up an-<br>wake-up from SLEEP on pin change. This buffer is a<br>Schmitt Trigger input when used in serial programmin<br>mode.                                                                                                                                                                                                             |

|      | GP1            | 6            | 6             | I/O           | TTL/ST         | Bi-directional I/O port/ serial programming clock. Car<br>be software programmed for internal weak pull-up an<br>wake-up from SLEEP on pin change. This buffer is a<br>Schmitt Trigger input when used in serial programmin<br>mode.                                                                                                                                                                                                             |

|      | GP2/T0CKI      | 5            | 5             | I/O           | ST             | Bi-directional I/O port. Can be configured as T0CKI.                                                                                                                                                                                                                                                                                                                                                                                             |

| et4L | GP3/MCLR/VPP   | 4            | 4             | I             | TTL/ST         | Input port/master clear (reset) input/programming vo<br>age input. When configured as MCLR, this pin is an<br>active low reset to the device. Voltage on MCLR/VPP<br>must not exceed VDD during normal device operation<br>or the device will enter programming mode. Can be<br>software programmed for internal weak pull-up and<br>wake-up from SLEEP on pin change. Weak pull-up<br>always on if configured as MCLR. ST when in MCLF<br>mode. |

|      | GP4/OSC2       | 3            | 3             | I/O           | TTL            | Bi-directional I/O port/oscillator crystal output. Con-<br>nections to crystal or resonator in crystal oscillator<br>mode (XT and LP modes only, GPIO in other modes)                                                                                                                                                                                                                                                                            |

|      | GP5/OSC1/CLKIN | 2            | 2             | I/O           | TTL/ST         | Bidirectional IO port/oscillator crystal input/external<br>clock source input (GPIO in Internal RC mode only,<br>OSC1 in all other oscillator modes). TTL input when<br>GPIO, ST input in external RC oscillator mode.                                                                                                                                                                                                                           |

|      | Vdd            | 1            | 1             | Р             | _              | Positive supply for logic and I/O pins                                                                                                                                                                                                                                                                                                                                                                                                           |

|      | Vss            | 8            | 8             | Р             | _              | Ground reference for logic and I/O pins                                                                                                                                                                                                                                                                                                                                                                                                          |

| TABLE 3-1: PIC12C5XX PINOUT DESCRIPTION |

|-----------------------------------------|

|-----------------------------------------|

Legend: I = input, O = output, I/O = input/output, P = power, — = not used, TTL = TTL input, ST = Schmitt Trigger input

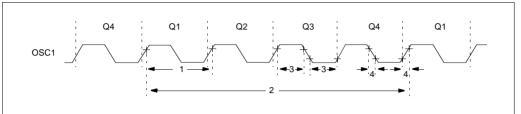

#### 3.1 **Clocking Scheme/Instruction Cycle**

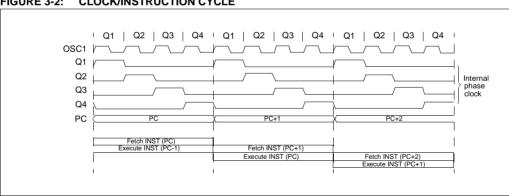

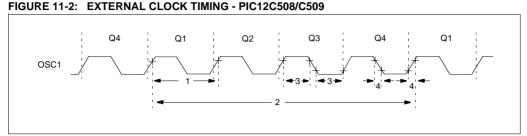

The clock input (OSC1/CLKIN pin) is internally divided by four to generate four non-overlapping quadrature clocks namely Q1, Q2, Q3 and Q4. Internally, the program counter is incremented every Q1, and the instruction is fetched from program memory and latched into instruction register in Q4. It is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 3-2 and Example 3-1.

#### Instruction Flow/Pipelining 3.2

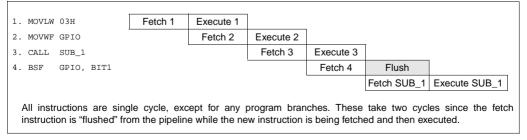

An Instruction Cycle consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g., GOTO) then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the Instruction Register (IR) in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### FIGURE 3-2: CLOCK/INSTRUCTION CYCLE

#### EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW

### 4.0 MEMORY ORGANIZATION

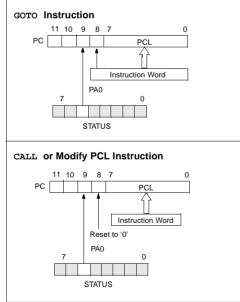

PIC12C5XX memory is organized into program memory and data memory. For devices with more than 512 bytes of program memory, a paging scheme is used. Program memory pages are accessed using one STA-TUS register bit. For the PIC12C509, PIC12C509A, PICCR509A and PIC12CE519 with a data memory register file of more than 32 registers, a banking scheme is used. Data memory banks are accessed using the File Select Register (FSR).

#### 4.1 Program Memory Organization

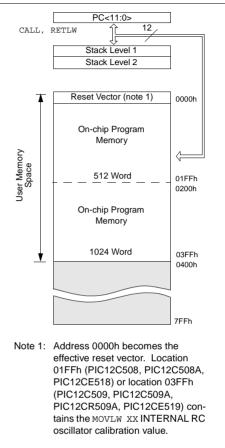

The PIC12C5XX devices have a 12-bit Program Counter (PC) capable of addressing a 2K x 12 program memory space.

Only the first 512 x 12 (0000h-01FFh) for the PIC12C508. PIC12C508A and PIC12CE518 and 1K x 12 (0000h-03FFh) for the PIC12C509, PIC12C509A. www.DataSheet4UPIC12CR509A, and PIC12CE519 are physically implemented. Refer to Figure 4-1. Accessing a location above these boundaries will cause a wraparound within the first 512 x 12 space (PIC12C508, PIC12C508A and PIC12CE518) or 1K x 12 space (PIC12C509, PIC12C509A, PIC12CR509A and PIC12CE519). The effective reset vector is at 000h. (see Figure 4-1). Location 01FFh (PIC12C508, PIC12C508A and PIC12CE518) or location 03FFh (PIC12C509, PIC12C509A, PIC12CR509A and PIC12CE519) contains the internal clock oscillator calibration value. This value should never be overwritten.

#### FIGURE 4-1: PROGRAM MEMORY MAP AND STACK

#### 4.2 Data Memory Organization

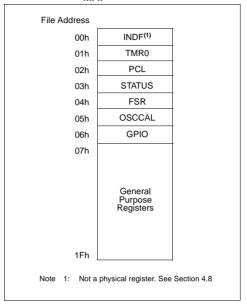

Data memory is composed of registers, or bytes of RAM. Therefore, data memory for a device is specified by its register file. The register file is divided into two functional groups: special function registers and general purpose registers.

The special function registers include the TMR0 register, the Program Counter (PC), the Status Register, the I/O registers (ports), and the File Select Register (FSR). In addition, special purpose registers are used to control the I/O port configuration and prescaler options.

The general purpose registers are used for data and control information under command of the instructions.

For the PIC12C508, PIC12C508A and PIC12CE518, the register file is composed of 7 special function registers and 25 general purpose registers (Figure 4-2).

For the PIC12C509, PIC12C509A, PIC12CR509A, and PIC12CE519 the register file is composed of 7 special function registers, 25 general purpose registers, and 16 general purpose registers that may be addressed using a banking scheme (Figure 4-3).

#### 4.2.1 GENERAL PURPOSE REGISTER FILE

The general purpose register file is accessed either directly or indirectly through the file select register FSR (Section 4.8).

#### FIGURE 4-2: PIC12C508, PIC12C508A AND PIC12CE518 REGISTER FILE MAP

| FSR<6:5    | 5>         | • 00                                  | 01                                     |

|------------|------------|---------------------------------------|----------------------------------------|

| File Addre | ess        |                                       |                                        |

| 0          | 00h        | INDF <sup>(1)</sup>                   | 20h                                    |

| <b>↓</b> 0 | 01h        | TMR0                                  |                                        |

| 0          | )2h        | PCL                                   | _                                      |

| 0          | )3h        | STATUS                                | Addresses map<br>back to               |

| 0          | 04h        | FSR                                   | addresses                              |

| 0          | )5h        | OSCCAL                                | in Bank 0.                             |

| 0          | 06h        | GPIO                                  |                                        |

|            | )7h<br>)Fh | General<br>Purpose<br>Registers       | 2Fh                                    |

|            | 10         | 0h<br>General<br>Purpose<br>Registers | 30h<br>General<br>Purpose<br>Registers |

|            | 11         | Fh                                    | 3Fh                                    |

|            |            | Bank 0                                | Bank 1                                 |

| Note       | 9 1:       | Not a physical regi                   | ster. See Section 4.8                  |

#### FIGURE 4-3: PIC12C509, PIC12C509A, PIC12CR509A AND PIC12CE519 REGISTER FILE MAP

#### 4.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers (SFRs) are registers used by the CPU and peripheral functions to control the operation of the device (Table 4-1). The special registers can be classified into two sets. The special function registers associated with the "core" functions are described in this section. Those related to the operation of the peripheral features are described in the section for each peripheral feature.

#### TABLE 4-1: SPECIAL FUNCTION REGISTER (SFR) SUMMARY

| Address                                                                                  | Name                                                                                | Bit 7                       | Bit 6                                | Bit 5       | Bit 4 | Bit 3     | Bit 2     | Bit 1 | Bit 0 | Value on<br>Power-On<br>Reset | Value on<br>All Other<br>Resets <sup>(2)</sup> |

|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-----------------------------|--------------------------------------|-------------|-------|-----------|-----------|-------|-------|-------------------------------|------------------------------------------------|

| N/A                                                                                      | TRIS                                                                                | —                           | -                                    |             |       |           |           |       |       | 11 1111                       | 11 1111                                        |

| N/A                                                                                      | OPTION                                                                              | Contains co<br>prescaler, v |                                      |             |       | 1111 1111 | 1111 1111 |       |       |                               |                                                |

| 00h                                                                                      | INDF                                                                                | Uses conte                  | nts of FSF                           | R to addres |       | xxxx xxxx | uuuu uuuu |       |       |                               |                                                |

| 01h                                                                                      | TMR0                                                                                | 8-bit real-tir              | me clock/c                           | ounter      |       |           |           |       |       | xxxx xxxx                     | uuuu uuuu                                      |

| 02h <sup>(1)</sup>                                                                       | PCL                                                                                 | Low order 8                 | B bits of PC                         | 0           |       | 1111 1111 | 1111 1111 |       |       |                               |                                                |

| 03h                                                                                      | STATUS                                                                              | GPWUF                       | —                                    | PA0         | TO    | PD        | Z         | DC    | С     | 0001 1xxx                     | q00q quuu <b>(3)</b>                           |

| FSR<br>(PIC12C508/<br>PIC12C508A/<br>04h PIC12C518) Indirect data memory address pointer |                                                                                     |                             |                                      |             |       |           |           |       |       | 111x xxxx                     | 111u uuuu                                      |

| 04h                                                                                      | FSR<br>(PIC12C509/<br>PIC12C509A/<br>PIC12CR509A/<br>PIC12CE519)                    | Indirect dat                | Indirect data memory address pointer |             |       |           |           |       |       |                               | 11uu uuuu                                      |

| 05h                                                                                      | OSCCAL<br>(PIC12C508/<br>PIC12C509)                                                 | CAL3                        | CAL2                                 | CAL1        | CAL0  | _         | _         | _     | _     | 0111                          | uuuu                                           |

| 05h                                                                                      | OSCCAL<br>(PIC12C508A/<br>PIC12C509A/<br>PIC12CE518/<br>PIC12CE519/<br>PIC12CR509A) | CAL5                        | CAL4                                 | CAL3        | CAL2  | CAL1      | CAL0      | _     | _     | 1000 00                       | uuuu uu                                        |

| 06h                                                                                      | GPIO<br>(PIC12C508/<br>PIC12C509/<br>PIC12C508A/<br>PIC12C509A/<br>PIC12CC509A)     | _                           | _                                    | GP5         | GP4   | GP3       | GP2       | GP1   | GP0   | xx xxxx                       | uu uuuu                                        |

| 06h                                                                                      | GPIO<br>(PIC12CE518/<br>PIC12CE519)                                                 | SCL                         | SDA                                  | GP5         | GP4   | GP3       | GP2       | GP1   | GP0   | llxx xxxx                     | 11uu uuuu                                      |

Legend: Shaded boxes = unimplemented or unused, - = unimplemented, read as '0' (if applicable)

x = unknown, u = unchanged, q = see the tables in Section 8.7 for possible values.

Note 1: The upper byte of the Program Counter is not directly accessible. See Section 4.6 for an explanation of how to access these bits.

2: Other (non power-up) resets include external reset through MCLR, watchdog timer and wake-up on pin change reset.

3: If reset was due to wake-up on pin change then bit 7 = 1. All other resets will cause bit 7 = 0.

#### 4.3 STATUS Register

This register contains the arithmetic status of the ALU, the RESET status, and the page preselect bit for program memories larger than 512 words.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as 000u uluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF and MOVWF instructions be used to alter the STATUS register because these instructions do not affect the Z, DC or C bits from the STATUS register. For other instructions, which do affect STATUS bits, see Instruction Set Summary.

#### FIGURE 4-4: STATUS REGISTER (ADDRESS:03h)

| et41R/W-01 | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                  | R/W-0 | R-1 | R-1               | R/W-x                                             | R/W-x | R/W-x                  |                                              |  |  |  |  |  |  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-------------------|---------------------------------------------------|-------|------------------------|----------------------------------------------|--|--|--|--|--|--|

| GPWUF      | —                                                                                                                                                                                                                                                                                                                                                                                                                                      | PA0   | TO  | PD                | Z                                                 | DC    | С                      | R = Readable bit                             |  |  |  |  |  |  |

| bit7       | 6                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5     | 4   | 3                 | 2                                                 | 1     | bit0                   | W = Writable bit<br>- n = Value at POR reset |  |  |  |  |  |  |

| bit 7:     | GPWUF: GPIO reset bit<br>1 = Reset due to wake-up from SLEEP on pin change<br>0 = After power up or other reset                                                                                                                                                                                                                                                                                                                        |       |     |                   |                                                   |       |                        |                                              |  |  |  |  |  |  |

| bit 6:     | Unimplemented                                                                                                                                                                                                                                                                                                                                                                                                                          |       |     |                   |                                                   |       |                        |                                              |  |  |  |  |  |  |

| bit 5:     | <ul> <li>PA0: Program page preselect bits</li> <li>1 = Page 1 (200h - 3FFh) - PIC12C509, PIC12C509A, PIC12CR509A and PIC12CE519</li> <li>0 = Page 0 (000h - 1FFh) - PIC12C5XX</li> <li>Each page is 512 bytes.</li> <li>Using the PA0 bit as a general purpose read/write bit in devices which do not use it for program page preselect is not recommended since this may affect upward compatibility with future products.</li> </ul> |       |     |                   |                                                   |       |                        |                                              |  |  |  |  |  |  |

| bit 4:     |                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |     |                   |                                                   |       |                        |                                              |  |  |  |  |  |  |

| bit 3:     | PD: Power-down bit         1 = After power-up or by the CLRWDT instruction         0 = By execution of the SLEEP instruction                                                                                                                                                                                                                                                                                                           |       |     |                   |                                                   |       |                        |                                              |  |  |  |  |  |  |

| bit 2:     | <b>Z</b> : Zero bit<br>1 = The result of an arithmetic or logic operation is zero<br>0 = The result of an arithmetic or logic operation is not zero                                                                                                                                                                                                                                                                                    |       |     |                   |                                                   |       |                        |                                              |  |  |  |  |  |  |

| bit 1:     | DC: Digit carry/borrow bit (for ADDWF and SUBWF instructions)<br>ADDWF<br>1 = A carry from the 4th low order bit of the result occurred<br>0 = A carry from the 4th low order bit of the result did not occur<br>SUBWF<br>1 = A borrow from the 4th low order bit of the result did not occur<br>0 = A borrow from the 4th low order bit of the result did not occur<br>0 = A borrow from the 4th low order bit of the result occurred |       |     |                   |                                                   |       |                        |                                              |  |  |  |  |  |  |

| bit 0:     | ADDWF<br>1 = A carry                                                                                                                                                                                                                                                                                                                                                                                                                   | ,     | ,   | SUBWF<br>1 = A bo | RRF, RLF instr<br>rrow did not c<br>rrow occurred | occur | RRF or R<br>Load bit v | LF<br>ith LSB or MSB, respectively           |  |  |  |  |  |  |

#### 4.4 OPTION Register

The OPTION register is a 8-bit wide, write-only register which contains various control bits to configure the Timer0/WDT prescaler and Timer0.

By executing the OPTION instruction, the contents of the W register will be transferred to the OPTION register. A RESET sets the OPTION<7:0> bits.

#### FIGURE 4-5: OPTION REGISTER

Note: If TRIS bit is set to '0', the wake-up on change and pull-up functions are disabled for that pin; i.e., note that TRIS overrides OPTION control of GPPU and GPWU.

**Note:** If the TOCS bit is set to '1', GP2 is forced to be an input even if TRIS GP2 = '0'.

| -            | W-1  | W-1                                                                                                                                                                | W-1                                                                         | W-1                   | W-1                                                       | W-1 | W-1 | W-1  |                                                                                               |  |  |  |  |  |

|--------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------|-----------------------------------------------------------|-----|-----|------|-----------------------------------------------------------------------------------------------|--|--|--|--|--|

| G            | SPWU | GPPU                                                                                                                                                               | TOCS                                                                        | T0SE                  | PSA                                                       | PS2 | PS1 | PS0  | W = Writable bit                                                                              |  |  |  |  |  |

| bit7         | 7    | 6                                                                                                                                                                  | 5                                                                           | 4                     | 3                                                         | 2   | 1   | bit0 | U = Unimplemented bit<br>- n = Value at POR reset<br>Reference Table 4-1 for<br>other resets. |  |  |  |  |  |

| bit<br>J.con |      | GPWU: Enable wake-up on pin change (GP0, GP1, GP3)<br>1 = Disabled<br>0 = Enabled                                                                                  |                                                                             |                       |                                                           |     |     |      |                                                                                               |  |  |  |  |  |

| bit          | 6:   | GPPU: Enable weak pull-ups (GP0, GP1, GP3)<br>1 = Disabled<br>0 = Enabled                                                                                          |                                                                             |                       |                                                           |     |     |      |                                                                                               |  |  |  |  |  |

| bit          | 5:   | 5: <b>TOCS</b> : Timer0 clock source select bit<br>1 = Transition on TOCKI pin<br>0 = Transition on internal instruction cycle clock, Fosc/4                       |                                                                             |                       |                                                           |     |     |      |                                                                                               |  |  |  |  |  |

| bit          | 4:   | <b>TOSE:</b> Timer0 source edge select bit<br>1 = Increment on high to low transition on the T0CKI pin<br>0 = Increment on low to high transition on the T0CKI pin |                                                                             |                       |                                                           |     |     |      |                                                                                               |  |  |  |  |  |

| bit          | 3:   | <b>PSA</b> : Prescale<br>1 = Prescale<br>0 = Prescale                                                                                                              | er assigned                                                                 | to the WI             |                                                           |     |     |      |                                                                                               |  |  |  |  |  |

| bit          | 2-0: | PS2:PS0: P                                                                                                                                                         | rescaler rate                                                               | e select b            | oits                                                      |     |     |      |                                                                                               |  |  |  |  |  |

|              |      | Bit Value                                                                                                                                                          | Timer0 Ra                                                                   | ate WD                | T Rate                                                    |     |     |      |                                                                                               |  |  |  |  |  |

|              |      | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111                                                                                                               | 1 : 2<br>1 : 4<br>1 : 8<br>1 : 16<br>1 : 32<br>1 : 64<br>1 : 128<br>1 : 256 | 1<br>1<br>1<br>1<br>1 | : 1<br>: 2<br>: 4<br>: 8<br>: 16<br>: 32<br>: 64<br>: 128 |     |     |      |                                                                                               |  |  |  |  |  |

#### 4.5 <u>OSCCAL Register</u>

The Oscillator Calibration (OSCCAL) register is used to calibrate the internal 4 MHz oscillator. It contains four to six bits for calibration. Increasing the cal value increases the frequency. See Section 7.2.5 for more information on the internal oscillator.

#### FIGURE 4-6: OSCCAL REGISTER (ADDRESS 05h) FOR PIC12C508 AND PIC12C509

| R/     | W-0   | R/W-1    | R/W-1     | R/W-1       | R/W-0 | R/W-0 | U-0 | U-0  |                          |

|--------|-------|----------|-----------|-------------|-------|-------|-----|------|--------------------------|

| C      | AL3   | CAL2     | CAL1      | CAL0        | -     | —     |     | _    | R = Readable bit         |

| bit7   |       |          |           |             |       |       |     | bit0 | W = Writable bit         |

|        |       |          |           |             |       |       |     |      | U = Unimplemented bit,   |

|        |       |          |           |             |       |       |     |      | read as '0'              |

|        |       |          |           |             |       |       |     |      | - n = Value at POR reset |

| bit    | 7-4:  | CAL<3:0: | Calibrat  | ion         |       |       |     |      |                          |

| bit    | 3-0:  | Unimpler | nented: R | Read as '0' |       |       |     |      |                          |

|        |       | •        |           |             |       |       |     |      |                          |

|        |       |          |           |             |       |       |     |      |                          |

| 001011 | 00111 |          |           |             |       |       |     |      |                          |

#### FIGURE 4-7: OSCCAL REGISTER (ADDRESS 05h) FOR PIC12C508A/C509A/CR509A/12CE518/ 12CE519

| R/W-1    | R/W-0    | R/W-0     | R/W-0       | R/W-0 | R/W-0 | U-0 | U-0  |                                                                                                                      |

|----------|----------|-----------|-------------|-------|-------|-----|------|----------------------------------------------------------------------------------------------------------------------|

| CAL5     | CAL4     | CAL3      | CAL2        | CAL1  | CAL0  | _   | _    | R = Readable bit                                                                                                     |

| bit7     |          |           |             |       |       |     | bit0 | <ul> <li>W = Writable bit</li> <li>U = Unimplemented bit,<br/>read as '0'</li> <li>n = Value at POR reset</li> </ul> |

| bit 7-2: | CAL<5:0: | Calibrat  | tion        |       |       |     |      |                                                                                                                      |

| bit 1-0: | Unimpler | nented: F | Read as '0' |       |       |     |      |                                                                                                                      |

|          |          |           |             |       |       |     |      |                                                                                                                      |

#### 4.6 Program Counter

As a program instruction is executed, the Program Counter (PC) will contain the address of the next program instruction to be executed. The PC value is increased by one every instruction cycle, unless an instruction changes the PC.

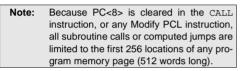

For a GOTO instruction, bits 8:0 of the PC are provided by the GOTO instruction word. The PC Latch (PCL) is mapped to PC<7:0>. Bit 5 of the STATUS register provides page information to bit 9 of the PC (Figure 4-8).

For a CALL instruction, or any instruction where the PCL is the destination, bits 7:0 of the PC again are provided by the instruction word. However, PC<8> does not come from the instruction word, but is always cleared (Figure 4-8).

Instructions where the PCL is the destination, or Modify PCL instructions, include MOVWF PC, ADDWF PC, and BSF PC, 5.

#### FIGURE 4-8: LOADING OF PC BRANCH INSTRUCTIONS -PIC12C5XX

#### 4.6.1 EFFECTS OF RESET

The Program Counter is set upon a RESET, which means that the PC addresses the last location in the last page i.e., the oscillator calibration instruction. After executing MOVLW XX, the PC will roll over to location 00h, and begin executing user code.

The STATUS register page preselect bits are cleared upon a RESET, which means that page 0 is pre-selected.

Therefore, upon a RESET, a GOTO instruction will automatically cause the program to jump to page 0 until the value of the page bits is altered.

#### 4.7 Stack

PIC12C5XX devices have a 12-bit wide L.I.F.O. hardware push/pop stack.

A CALL instruction will *push* the current value of stack 1 into stack 2 and then push the current program counter value, incremented by one, into stack level 1. If more than two sequential CALL's are executed, only the most recent two return addresses are stored.

A RETLW instruction will *pop* the contents of stack level 1 into the program counter and then copy stack level 2 contents into level 1. If more than two sequential RETLW's are executed, the stack will be filled with the address previously stored in level 2. Note that the W register will be loaded with the literal value specified in the instruction. This is particularly useful for the implementation of data look-up tables within the program memory.

Upon any reset, the contents of the stack remain unchanged, however the program counter (PCL) will also be reset to 0.

- Note 1: There are no STATUS bits to indicate stack overflows or stack underflow conditions.

- Note 2: There are no instructions mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL and RETLW instructions.

#### 4.8 Indirect Data Addressing; INDF and FSR Registers

The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a *pointer*). This is indirect addressing.

#### EXAMPLE 4-1: INDIRECT ADDRESSING

- Register file 07 contains the value 10h

- · Register file 08 contains the value 0Ah

- · Load the value 07 into the FSR register

- A read of the INDF register will return the value of 10h

- Increment the value of the FSR register by one (FSR = 08)

- A read of the INDR register now will return the value of 0Ah.

Reading INDF itself indirectly (FSR = 0) will produce www.DataShe00h.Writing to the INDF register indirectly results in a no-operation (although STATUS bits may be affected).

A simple program to clear RAM locations 10h-1Fh using indirect addressing is shown in Example 4-2.

#### EXAMPLE 4-2: HOW TO CLEAR RAM USING INDIRECT ADDRESSING

|          | movlw | 0x10  | ;initialize pointer |

|----------|-------|-------|---------------------|

|          | movwf | FSR   | ; to RAM            |

| NEXT     | clrf  | INDF  | clear INDF register |

|          | incf  | FSR,F | ;inc pointer        |

|          | btfsc | FSR,4 | ;all done?          |

|          | goto  | NEXT  | ;NO, clear next     |

| CONTINUE | 9     |       | -,                  |

|          | :     |       | ;YES, continue      |

The FSR is a 5-bit wide register. It is used in conjunction with the INDF register to indirectly address the data memory area.

The FSR<4:0> bits are used to select data memory addresses 00h to 1Fh.

**PIC12C508/PIC12C508A/PIC12CE518:** Does not use banking. FSR<7:5> are unimplemented and read as '1's.

#### PIC12C509/PIC12C509A/PIC12CR509A/

**PIC12CE519:** Uses FSR<5>. Selects between bank 0 and bank 1. FSR<7:6> is unimplemented, read as '1'.

#### FIGURE 4-9: DIRECT/INDIRECT ADDRESSING

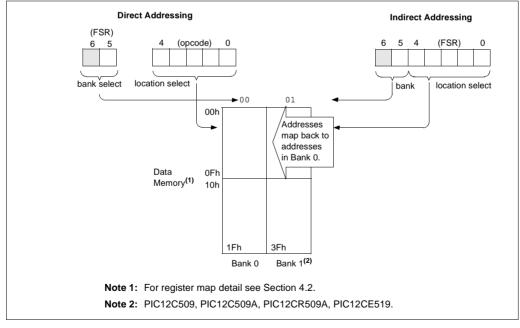

### 5.0 I/O PORT

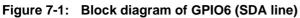

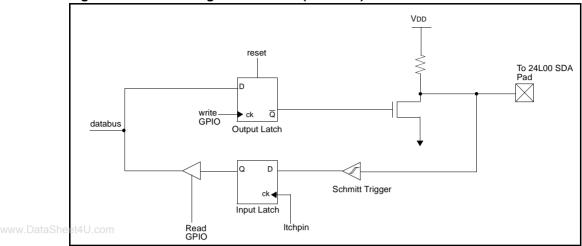

As with any other register, the I/O register can be written and read under program control. However, read instructions (e.g., MOVF GPIO, W) always read the I/O pins independent of the pin's input/output modes. On RESET, all I/O ports are defined as input (inputs are at hi-impedance) since the I/O control registers are all set. See Section 7.0 for SCL and SDA description for PIC12CE5XX.

#### 5.1 <u>GPIO</u>

GPIO is an 8-bit I/O register. Only the low order 6 bits are used (GP5:GP0). Bits 7 and 6 are unimplemented and read as '0's. Please note that GP3 is an input only pin. The configuration word can set several I/O's to alternate functions. When acting as alternate functions the pins will read as '0' during port read. Pins GP0, GP1, and GP3 can be configured with weak pull-ups and also with wake-up on change. The wake-up on change and weak pull-up functions are not pin selectable. If pin 4 is configured as MCLR, weak pullup is always on and wake-up on change for this pin is not enabled.

#### 5.2 TRIS Register

The output driver control register is loaded with the contents of the W register by executing the TRIS f instruction. A '1' from a TRIS register bit puts the corresponding output driver in a hi-impedance mode. A '0' puts the contents of the output data latch on the selected pins, enabling the output buffer. The exceptions are GP3 which is input only and GP2 which may be controlled by the option register, see Figure 4-5.

| Note: | A read of the ports reads the pins, not the    |  |  |  |  |  |  |  |

|-------|------------------------------------------------|--|--|--|--|--|--|--|

|       | output data latches. That is, if an output     |  |  |  |  |  |  |  |

|       | driver on a pin is enabled and driven high,    |  |  |  |  |  |  |  |

|       | but the external system is holding it low, a   |  |  |  |  |  |  |  |

|       | read of the port will indicate that the pin is |  |  |  |  |  |  |  |

|       | low.                                           |  |  |  |  |  |  |  |

The TRIS registers are "write-only" and are set (output drivers disabled) upon RESET.

#### 5.3 I/O Interfacing

The equivalent circuit for an I/O port pin is shown in Figure 5-1. All port pins, except GP3 which is input only, may be used for both input and output operations. For input operations these ports are non-latching. Any input must be present until read by an input instruction (e.g., MOVF GPIO, W). The outputs are latched and remain unchanged until the output latch is rewritten. To use a port pin as output, the corresponding direction control bit in TRIS must be cleared (= 0). For use as an input, the corresponding TRIS bit must be set. Any I/O pin (except GP3) can be programmed individually as input or output.

#### FIGURE 5-1: EQUIVALENT CIRCUIT FOR A SINGLE I/O PIN

| TABLE 5-1: SUMMARY OF PORT REGISTER |

|-------------------------------------|

|-------------------------------------|

| Address | Name                                                                            | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-On<br>Reset | Value on<br>All Other Resets |  |

|---------|---------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------------------------------|------------------------------|--|

| N/A     | TRIS                                                                            | _     |       |       |       |       |       |       |       | 11 1111                       | 11 1111                      |  |

| N/A     | OPTION                                                                          | GPWU  | GPPU  | TOCS  | TOSE  | PSA   | PS2   | PS1   | PS0   | 1111 1111                     | 1111 1111                    |  |

| 03H     | STATUS                                                                          | GPWUF | -     | PAO   | TO    | PD    | Z     | DC    | С     | 0001 1xxx                     | q00q quuu <sup>(1)</sup>     |  |

| 06h     | GPIO<br>(PIC12C508/<br>PIC12C509/<br>PIC12C508A/<br>PIC12C509A/<br>PIC12CC509A) | Ι     |       | GP5   | GP4   | GP3   | GP2   | GP1   | GP0   | xx xxxx                       | uu uuuu                      |  |

| 06h     | GPIO<br>(PIC12CE518/<br>PIC12CE519)                                             | SCL   | SDA   | GP5   | GP4   | GP3   | GP2   | GP1   | GP0   | 11xx xxxx                     | 11uu uuuu                    |  |

Legend: Shaded cells not used by Port Registers, read as '0', — = unimplemented, read as '0', x = unknown, u = unchanged, q = see tables in Section 8.7 for possible values.

Note 1: If reset was due to wake-up on change, then bit 7 = 1. All other resets will cause bit 7 = 0.

#### 5.4 I/O Programming Considerations

#### 5.4.1 BI-DIRECTIONAL I/O PORTS

Some instructions operate internally as read followed by write operations. The BCF and BSF instructions, for example, read the entire port into the CPU, execute the bit operation and re-write the result. Caution must be used when these instructions are applied to a port where one or more pins are used as input/outputs. For example, a BSF operation on bit5 of GPIO will cause all eight bits of GPIO to be read into the CPU, bit5 to be set and the GPIO value to be written to the output latches. If another bit of GPIO is used as a bidirectional I/O pin (say bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and rewritten to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the input mode, no problem occurs. However, if bit0 is switched into output mode later on, the content of the data latch may now be unknown.

Example 5-1 shows the effect of two sequential read-modify-write instructions (e.g.,  ${\tt BCF}$  ,  ${\tt BSF}$ , etc.) on an I/O port.

A pin actively outputting a high or a low should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wiredand"). The resulting high output currents may damage the chip.

#### EXAMPLE 5-1: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

| ; | Initia<br>GPIO<<br>GPIO< | 5:3> Ir | nputs |       |         |       |       |

|---|--------------------------|---------|-------|-------|---------|-------|-------|

|   |                          |         |       | CDIC  | ) latch | CDT   | Dning |

| ; |                          |         |       | GF 10 |         | GF 10 |       |

| ' | BCF                      | GPIO,   | 5     | ;01   | -ppp    | 11    | pppp  |

|   | BCF                      | GPIO,   | 4     | ;10   | -ppp    | 11    | pppp  |

|   | MOVLW                    | 007h    |       | ;     |         |       |       |

|   | TRIS                     | GPIO    |       | ;10   | -ppp    | 11    | pppp  |

|   |                          |         |       |       |         |       |       |

;Note that the user may have expected the pin ;values to be --00 pppp. The 2nd BCF caused ;GP5 to be latched as the pin value (High).

## 5.4.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 5-2). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should allow the pin voltage to stabilize (load dependent) before the next instruction, which causes that file to be read into the CPU, is executed. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

#### FIGURE 5-2: SUCCESSIVE I/O OPERATION

|                        | Q1  Q2  Q3  Q4 | Q1  Q2  Q3  Q4                   | Q1   Q2   Q3   Q4             | Q1  Q2  Q3  Q4 | :                                                                                             |

|------------------------|----------------|----------------------------------|-------------------------------|----------------|-----------------------------------------------------------------------------------------------|

|                        | PC             | X PC + 1                         | X PC + 2                      | V PC + 3       | This example shows a write to GPIO followed                                                   |

| Instruction<br>fetched | MOVWF GPIO     | MOVF GPIO,W                      | NOP                           | NOP            | by a read from GPIO.<br>Data setup time = (0.25 Tcy – TPD)<br>where: Tcy = instruction cycle. |

| GP5:GP0                |                | 1<br>1                           | Χ                             |                | TPD = propagation delay                                                                       |

| Instruction            |                | Port pin<br>written here         | Port pin<br>sampled here      |                | Therefore, at higher clock frequencies, a write followed by a read may be problematic.        |

| executed               |                | MOVWF GPIO<br>(Write to<br>GPIO) | MOVF GPIO,W<br>(Read<br>GPIO) | NOP            |                                                                                               |

|                        |                |                                  |                               |                |                                                                                               |

www.DataSheet4U.com

## PIC12C5XX

NOTES:

www.DataSheet4U.com

#### 6.0 TIMER0 MODULE AND TMR0 REGISTER

The Timer0 module has the following features:

- 8-bit timer/counter register, TMR0

- Readable and writable

- 8-bit software programmable prescaler

- Internal or external clock select

- Edge select for external clock

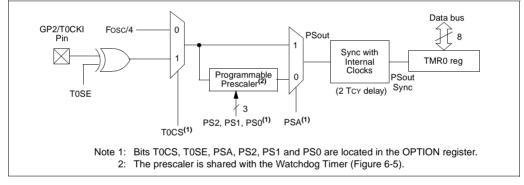

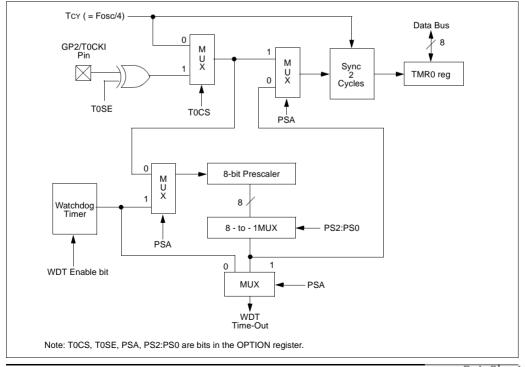

Figure 6-1 is a simplified block diagram of the Timer0 module.

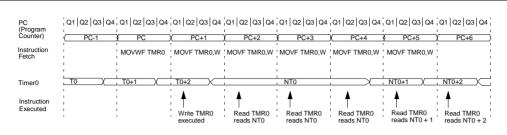

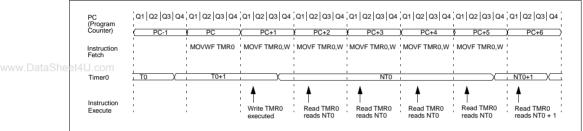

Timer mode is selected by clearing the T0CS bit (OPTION<5>). In timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If TMR0 register is written, the increment is inhibited for the following two instruction cycles (Figure 6-2 and Figure 6-3). The user can work around this by writing an adjusted value to the TMR0 register.

www.DataSheet4U.com

Counter mode is selected by setting the TOCS bit (OPTION<5>). In this mode, Timer0 will increment either on every rising or falling edge of pin TOCKI. The TOSE bit (OPTION<4>) determines the source edge. Clearing the TOSE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 6.1.

The prescaler may be used by either the Timer0 module or the Watchdog Timer, but not both. The prescaler assignment is controlled in software by the control bit PSA (OPTION<3>). Clearing the PSA bit will assign the prescaler to Timer0. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4,..., 1:256 are selectable. Section 6.2 details the operation of the prescaler.

A summary of registers associated with the Timer0 module is found in Table 6-1.

#### FIGURE 6-1: TIMER0 BLOCK DIAGRAM

#### FIGURE 6-2: TIMER0 TIMING: INTERNAL CLOCK/NO PRESCALE

#### FIGURE 6-3: TIMER0 TIMING: INTERNAL CLOCK/PRESCALE 1:2

#### TABLE 6-1: REGISTERS ASSOCIATED WITH TIMER0

| Address | Name   | Bit 7    | Bit 6                                 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-On<br>Reset | Value on<br>All Other<br>Resets |

|---------|--------|----------|---------------------------------------|-------|-------|-------|-------|-------|-------|-------------------------------|---------------------------------|

| 01h     | TMR0   | Timer0 - | ïmer0 - 8-bit real-time clock/counter |       |       |       |       |       |       | xxxx xxxx                     | uuuu uuuu                       |

| N/A     | OPTION | GPWU     | GPPU                                  | T0CS  | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1111                     | 1111 1111                       |

| N/A     | TRIS   | —        | —                                     | GP5   | GP4   | GP3   | GP2   | GP1   | GP0   | 11 1111                       | 11 1111                         |

Legend: Shaded cells not used by Timer0, - = unimplemented, x = unknown, u = unchanged,

#### 6.1 Using Timer0 with an External Clock

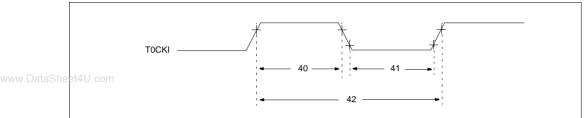

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

#### 6.1.1 EXTERNAL CLOCK SYNCHRONIZATION

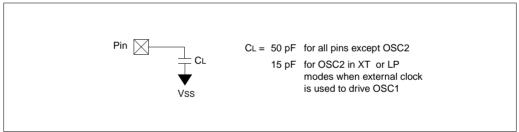

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 6-4). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

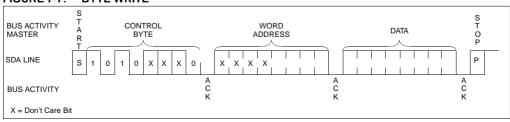

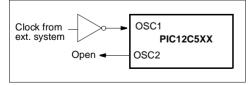

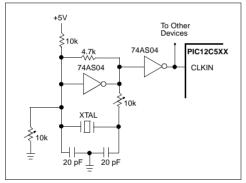

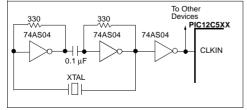

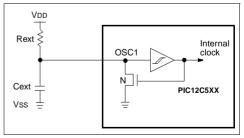

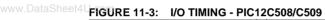

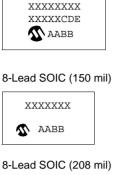

www.DataSheet4U.com