MPS

2316

STATIC READ

ONLY MEMORY

(2048x8)

# 2316 STATIC READ ONLY MEMORY (2048x8)

### DESCRIPTION

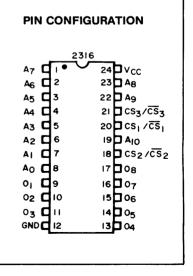

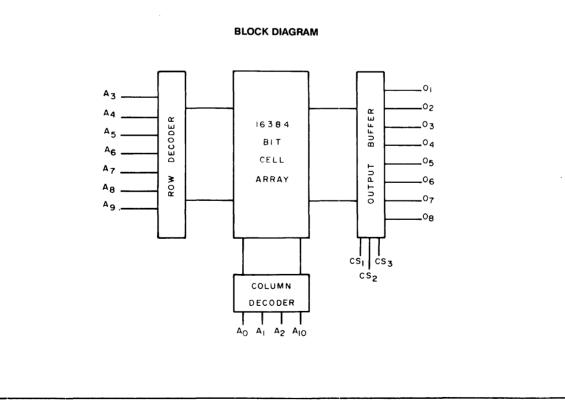

The 2316 high performance read only memory is organized 2048 words by 8 bits with access times of less than 350 ns. This ROM is designed to be compatible with all microprocessor and similar applications where high performance, large bit storage and simple interfacing are important design considerations.

The 2316 operates totally asynchronously. No clock input is required. The three programmable chip select inputs allow eight 16K ROMS to be OR-tied without external decoding.

Designed to replace two 2708 8K EPROMS, the 2316 can eliminate the need to redesign printed circuit boards for volume mask programmed ROMS after prototyping with EPROMS.

- 400mV Noise Immunity on Inputs

- 2048 x 8 Bit Organization

- Single +5 Volt Supply

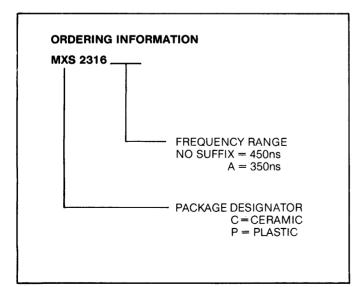

- Access Time 450 ns, 350 ns

- Totally Static Operation

- TTL Compatible

- Three-State Outputs for Wire-OR Expansion

- Three Programmable Chip Selects

- Pin Compatible with 2716 EPROM

- Replacement for two 2708s

- 2708/2716 EPROMS Accepted as Program Data Inputs

#### **ABSOLUTE MAXIMUM RATINGS**

Ambient Temperature under Bias Storage Temperature -65°C to +70°C -65°C to +150°C Supply Voltage to Ground Potential Applied Output Voltage -0.5V to +7.0V Applied Input Voltage -0.5V to +7.0V Power Dissipation 1.0W

### COMMENT

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

# **D. C. CHARACTERISTICS** ( $T_A = 0^{\circ}\text{C}$ to $+70^{\circ}\text{C}$ , $V_{CC} = 5.0\text{V} \pm 5\%$ , unless otherwise specified)

| Symbol | Parameter              | Min. | Max.  | Units | Test Conditions                                  |

|--------|------------------------|------|-------|-------|--------------------------------------------------|

| ICC1   | Power Supply Current   |      | 100   | mA    | $V_{IN} = V_{CC}, V_0 = Open, T_A = 0^{\circ}C$  |

| ICC2   | Power Supply Current   |      | 95    | mΑ    | $V_{IN} = V_{CC}, V_0 = Open, T_A = 25^{\circ}C$ |

| 10     | Output Leakage Current |      | 10    | μΑ    | Chip Deselected, $V_0 = 0$ to $V_{CC}$           |

| 11     | Input Load Current     |      | 10    | μA    | $V_{CC} = Max. V_{IN} = 0 \text{ to } V_{CC}$    |

| VOL    | Output Low Voltage     |      | 0.4   | Volts | $V_{CC} = Min. I_{OL} = 2.1 mA$                  |

| Voн    | Output High Voltage    | 2.4  |       | Volts | $V_{CC}$ = Min. $I_{OH}$ = $-400\mu$ A           |

| VIL    | Input Low Voltage      | -0.5 | 0.8   | Volts | See Note 1                                       |

| ViH    | Input High Voltage     | 2.0  | VCC+1 | Volts |                                                  |

# **A. C. CHARACTERISTICS** (TA = 0°C to $+70^{\circ}$ C, $V_{CC} = 5.0V \pm 5\%$ , unless otherwise specified)

|        | Parameter                                            | 2316 |      | 2316A |      |       |                 |

|--------|------------------------------------------------------|------|------|-------|------|-------|-----------------|

| Symbol |                                                      | Min. | Max. | Min.  | Max. | Units | Test Conditions |

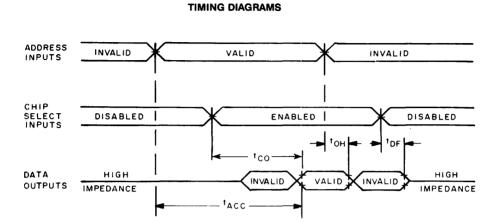

| tACC   | Address Access Time                                  |      | 450  |       | 350  | ns    |                 |

| tco    | Chip Select Delay                                    |      | 200  |       | 200  | ns    |                 |

| tDF    | Chip Deselect Delay                                  |      | 175  |       | 175  | ns    | See Note 2      |

| tОН    | Previous Data Valid<br>After Address Change<br>Delay | 40   |      | 40    |      | ns    |                 |

## **CAPACITANCE** $(T_A = 25^{\circ}C, f = 1.0 \text{MHz}, \text{See Note 3})$

| Symbol | Parameter          | Min. | Max. | Units | Test Conditions           |

|--------|--------------------|------|------|-------|---------------------------|

| CIN    | Input Capacitance  |      | 8    | рF    | All Pins except Pin under |

| COUT   | Output Capacitance |      | 10   | pF    | Test Tied to AC Ground    |

Note 1: Input levels that swing more negative than -0.5V will be clamped and may cause damage to the device.

Note 2: Loading 1 TTL + 100 pF, input transition time: 20 ns

Timing measurement levels: input 1.5V, output 0.8V and 2.0V.

Note 3: This parameter is periodically sampled and is not 100% tested.

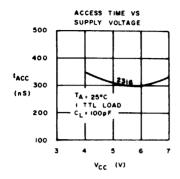

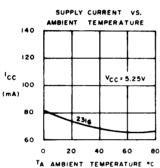

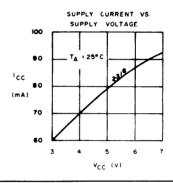

### **TYPICAL CHARACTERISTICS**

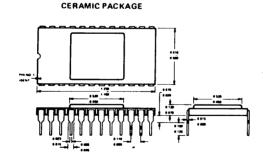

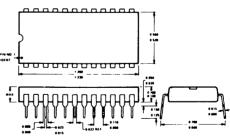

### **PACKAGING DIAGRAM**

MOLDED PACKAGE

Commodore Semiconductor Group reserves the right to make changes to any products herein to improve reliability, function or design. Commodore Semiconductor Group does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others.