# 128×8 bit electrically erasable PROM BR24L01A-W / BR24L01AF-W / BR24L01AFJ-W BR24L01AFV-W / BR24L01AFVM-W

The BR24L01A-W series is 2-wire (I<sup>2</sup>C BUS type) serial EEPROMs which are electrically programmable.

\* I<sup>2</sup>C BUS is a registered trademark of Philips.

#### Applications

General purpose

#### Features

- 1) 128 registers  $\times$  8 bits serial architecture.

- 2) Single power supply (1.8V to 5.5V).

- 3) Two wire serial interface.

- 4) Self-timed write cycle with automatic erase.

- 5) 8 byte page write mode.

- 6) Low power consumption.

- Write (5V): 1.2mA (Typ.) Read (5V) : 0.2mA (Typ.) Standby (5V) : 0.1µA (Typ.)

- 7) DATA security

Write protect feature (WP pin) .

Inhibit to WRITE at low Vcc.

- 8) Small package - DIP8 / SOP8 / SOP-J8 / SSOP-B8 / MSOP-8

- 9) High reliability EEPROM with Double-Cell Structure

- 10) High reliability fine pattern CMOS technology.

- 11) Endurance : 1,000,000 erase / write cycles

- 12) Data retention : 40 years

- 13) Filtered inputs in SCL-SDA for noise suppression.

- 14) Initial data FFh in all address.

#### Absolute maximum ratings (Ta=25°C)

| Parameter             | Symbol | Limits           | Unit |

|-----------------------|--------|------------------|------|

| Supply voltage        | Vcc    | -0.3 to +6.5     | V    |

|                       |        | 800 (DIP8) *1    |      |

|                       |        | 450 (SOP8) *2    |      |

| Power dissipation     | Pd     | 450 (SOP-J8) *3  | mW   |

|                       |        | 300 (SSOP-B8) *4 |      |

|                       |        | 310 (MSOP8) *5   |      |

| Storage temperature   | Tstg   | -65 to +125      | °C   |

| Operating temperature | Topr   | -40 to +85       | °C   |

| Terminal voltage      | -      | -0.3 to Vcc+0.3  | V    |

\*1 Degradation is done at 8.0mW/°C for operation above 25°C \*2, 3 Degradation is done at 4.5mW°C for operation above 25°C \*4 Degradation is done at 3.0mW/°C for operation above 25°C \*5 Degradation is done at 3.1mW/°C for operation above 25°C

## BR24L01A-W / BR24L01AF-W / BR24L01AFJ-W / BR24L01AFV-W / BR24L01AFVM-W

### Memory ICs

### Recommended operating conditions

| Parameter      | Symbol | Limits     | Unit |

|----------------|--------|------------|------|

| Supply voltage | Vcc    | 1.8 to 5.5 | V    |

| Input voltage  | Vin    | 0 to Vcc   | V    |

### ●DC operating characteristics (Unless otherwise specified Ta=-40 to 85°C, VCC=1.8 to 5.5V)

| Parameter              | Symbol | Min.   | Тур. | Max.   | Unit | Conditions                                                             |

|------------------------|--------|--------|------|--------|------|------------------------------------------------------------------------|

| "HIGH" input volatge 1 | VIH1   | 0.7Vcc | _    | -      | V    | 2.5V≤Vcc≤5.5V                                                          |

| "LOW" input volatge 1  | VIL1   | -      | _    | 0.3Vcc | V    | 2.5V≤Vcc≤5.5V                                                          |

| "HIGH" input volatge 2 | VIH2   | 0.8Vcc | _    | -      | V    | 1.8V≤Vcc≤2.5V                                                          |

| "LOW" input volatge 2  | VIL2   | -      | -    | 0.2Vcc | V    | 1.8V≤Vcc≤2.5V                                                          |

| "LOW" output volatge 1 | Vol1   | -      | _    | 0.4    | V    | Io∟=3.0mA, 2.5V≤Vcc≤5.5V, (SDA)                                        |

| "LOW" output volatge 2 | Vol2   | -      | _    | 0.2    | V    | lo∟=0.7mA, 1.8V≤Vcc≤5.5V, (SDA)                                        |

| Input leakage current  | lu     | -1     | -    | 1      | μA   | VIN=0V to Vcc                                                          |

| Output leakage current | Ilo    | -1     | _    | 1      | μA   | Vout=0V to Vcc                                                         |

|                        | Icc1   | -      | _    | 2.0    | mA   | Vcc=5.5V, fscL=400kHz, twR=5ms,<br>Byte Write, Page Write              |

| Operating current      | Icc2   | -      | _    | 0.5    | mA   | Vcc=5.5V, fsc∟=400kHz<br>Random Read, Current Read,<br>Sequential Read |

| Standby current        | Іѕв    | -      | -    | 2.0    | μA   | Vcc=5.5V, SDA·SCL=Vcc,<br>A0, A1, A2=GND, WP=GND                       |

O This product is not designed for protection against radioactive rays.

## BR24L01A-W / BR24L01AF-W / BR24L01AFJ-W / BR24L01AFV-W / BR24L01AFVM-W

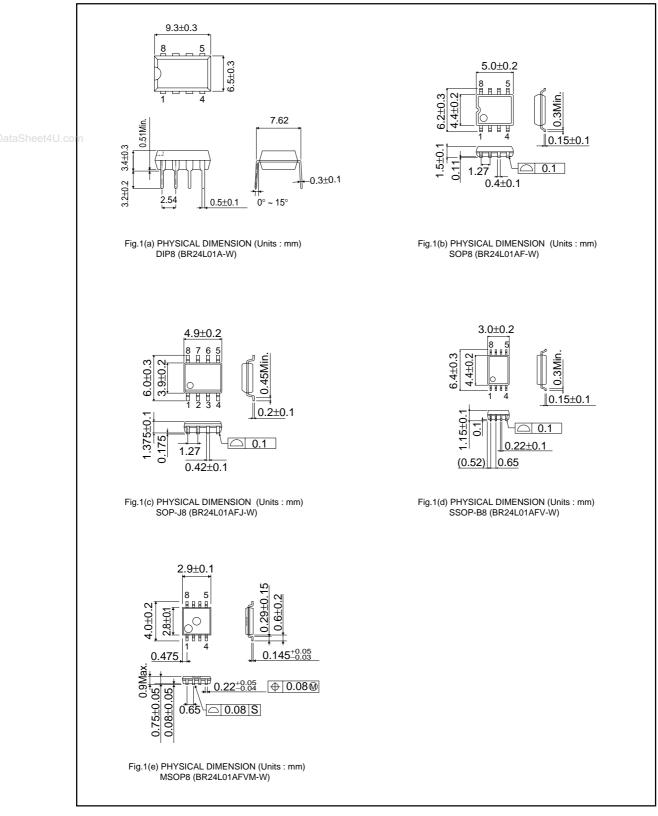

#### Dimension

rohm

3/25

## BR24L01A-W / BR24L01AF-W / BR24L01AFJ-W / BR24L01AFV-W / BR24L01AFVM-W

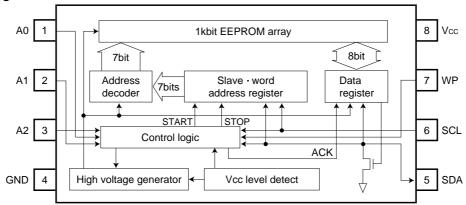

#### Block diagram

Fig.2 BLOCK DIAGRAM

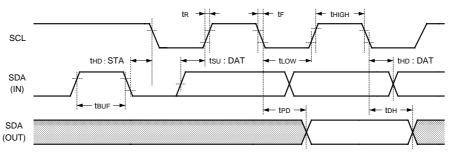

#### Pin configuration

Fig.3 PIN LAYOUT

#### •Pin name

| Pin name   | 1/0      | Function                                                            |

|------------|----------|---------------------------------------------------------------------|

| Vcc        | -        | Power supply                                                        |

| GND        | -        | Ground (0V)                                                         |

| A0, A1, A2 | IN       | Slave address set                                                   |

| SCL        | IN       | Serial clock input                                                  |

| SDA        | IN / OUT | Slave and word address,<br>serial data input, serial data output *1 |

| WP         | IN       | Write protect input                                                 |

\*1 An open drain output requires a pull-up resistor.

## BR24L01A-W / BR24L01AF-W / BR24L01AFJ-W / BR24L01AFV-W / BR24L01AFVM-W

| Parameter                       | Symbol   | Fast-mode $2.5V \le Vcc \le 5.5V$ |      |      | Standard-mode $1.8V \le Vcc \le 5.5V$ |      | Unit |     |

|---------------------------------|----------|-----------------------------------|------|------|---------------------------------------|------|------|-----|

|                                 |          | Min.                              | Тур. | Max. | Min.                                  | Тур. | Max. |     |

| Clock frequency                 | fSCL     | -                                 | -    | 400  | -                                     | -    | 100  | kHz |

| Data clock "HIGH" period        | tHIGH    | 0.6                               | -    | _    | 4.0                                   | -    | -    | μs  |

| Data clock "LOW" period         | tLOW     | 1.2                               | -    | -    | 4.7                                   | -    | -    | μs  |

| SDA and SCL rise time *1        | tR       | -                                 | -    | 0.3  | -                                     | -    | 1.0  | μs  |

| e eSDA and SCL fall time ≉1     | tF       | _                                 | -    | 0.3  | -                                     | -    | 0.3  | μs  |

| Start condition hold time       | tHD:STA  | 0.6                               | -    | -    | 4.0                                   | -    | -    | μs  |

| Start condition setup time      | tSU:STA  | 0.6                               | -    | _    | 4.7                                   | -    | -    | μs  |

| Input data hold time            | tHD:DAT  | 0                                 | -    | -    | 0                                     | -    | -    | ns  |

| Input data setup time           | tSU:DAT  | 100                               | -    | -    | 250                                   | -    | -    | ns  |

| Output data delay time          | tPD      | 0.1                               | -    | 0.9  | 0.2                                   | -    | 3.5  | μs  |

| Output data hold time           | tDH      | 0.1                               | -    | -    | 0.2                                   | -    | -    | μs  |

| Stop condition setup time       | tSU:STO  | 0.6                               | -    | -    | 4.7                                   | -    | -    | μs  |

| Bus free time                   | tBUF     | 1.2                               | -    | -    | 4.7                                   | -    | -    | μs  |

| Write cycle time                | tWR      | _                                 | -    | 5    | -                                     | -    | 5    | ms  |

| Noise spike width (SDA and SCL) | tl       | -                                 | -    | 0.1  | -                                     | -    | 0.1  | μs  |

| WP hold time                    | tHD:WP   | 0                                 | -    | -    | 0                                     | -    | -    | ns  |

| WP setup time                   | tSU:WP   | 0.1                               | -    | -    | 0.1                                   | -    | -    | μs  |

| WP high period                  | tHIGH:WP | 1.0                               | -    | -    | 1.0                                   | -    | -    | μs  |

### ●AC operating characteristics (Unless otherwise specified Ta=-40 to 85°C, VCC=1.8 to 5.5V)

\*1 Not 100% tested.

Rohm

## BR24L01A-W / BR24L01AF-W / BR24L01AFJ-W / BR24L01AFV-W / BR24L01AFVM-W

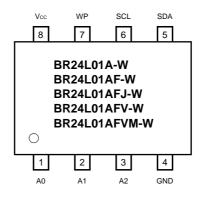

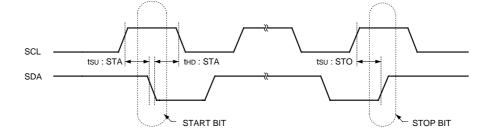

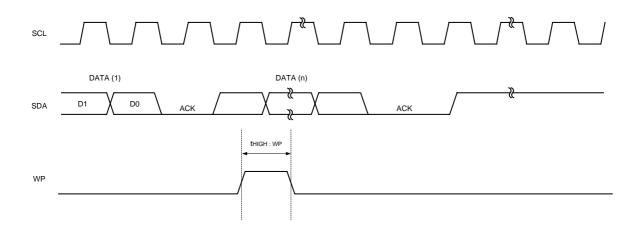

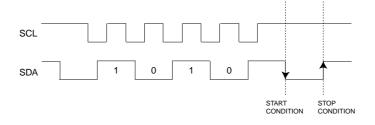

### •Synchronous data timing

ww.DataSheet4U.com

Fig.4 SYNCHRONOUS DATA TIMING

•SDA data is latched into the chip at the rising edge of SCL clock.

•Output data toggles at the falling edge of SCL clock.

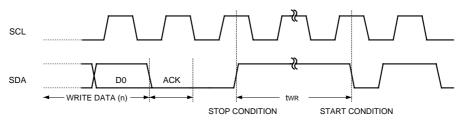

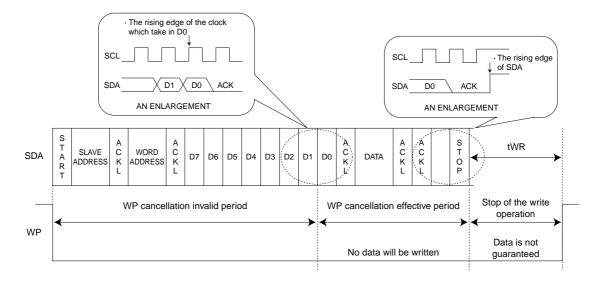

#### Write cycle timing

Fig.5 WRITE CYCLE TIMING

## BR24L01A-W / BR24L01AF-W / BR24L01AFJ-W / BR24L01AFV-W / BR24L01AFVM-W

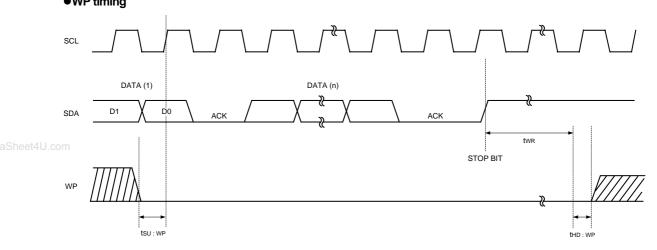

WP timing

Memory ICs

Fig.6(b) WP TIMING OF THE WRITE CANCEL OPERATION

•For the WRITE operation, WP must be "LOW" during the period of time from the rising edge of the clock which takes in D0 of first byte until the end of twR. (See Fig.6 (a))

During this period, WRITE operation is canceled by setting WP "HIGH". (See Fig.6 (b))

•In the case of setting WP "HIGH" during twR, WRITE operation is stopped in the middle and the data of accessing address is not guaranteed. Please write correct data again in the case.

## BR24L01A-W / BR24L01AF-W / BR24L01AFJ-W / BR24L01AFV-W / BR24L01AFVM-W

#### Device operation

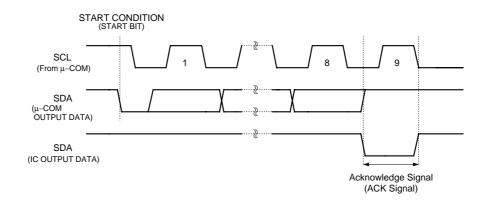

- 1) Start condition (Recognition of start bit)

- All commands are proceeded by the start condition, which is a HIGH to LOW transition of SDA when SCL is HIGH.

- The device continuously monitors the SDA and SCL lines for the start condition and will not respond to any command until this condition has been met. (See Fig.4 SYNCHRONOUS DATA TIMING)

2) Stop condition (Recognition of stop bit)

• All communications must be terminated by a stop condition, which is a LOW to HIGH transition of SDA when SCL is HIGH. (See Fig.4 SYNCHRONOUS DATA TIMING)

ww.DataSheet4U.com

- 3) Notice about write command

- In the case that stop condition is not executed in WRITE mode, transferred data will not be written in a memory.

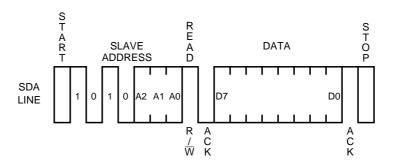

4) Device addressing

- Following a START condition, the master output the slave address to be accessed.

- The most significant four bits of the slave address are the "device type identifier", for this device it is fixed as "1010".

- The next three bit (device address) identify the specified device on the bus.

- The device address is defined by the state of A0, A1 and A2 input pins. This IC works only when the device address inputted from SDA pin correspond to the state of A0, A1 and A2 input pins. Using this address scheme, up to eight device may be connected to the bus. The last bit of the stream (RW - READ / WRITE) determines the operation to the performed.

- The last bit of the stream (R/W - READ / WRITE) determines the operation to be performed. When set to "1", a read operation is selected ; when set to "0", a write operation is selected.

$R\,/\,\overline{W}$  set to "0" - - - - - WRITE (including word address input of Random Read)  $R\,/\,\overline{W}$  set to "1" - - - - - READ

|  | 1010 | A2 | A1 | A0 | R/W |

|--|------|----|----|----|-----|

|--|------|----|----|----|-----|

5) Write protect (WP)

When WP pin set to Vcc (H level), write protect is set for 128 words (all address).

When WP pin set to GND (L level), enable to write 128 words (all address).

Either control this pin or connect to GND (or Vcc). It is inhibited from being left unconnected.

## BR24L01A-W / BR24L01AF-W / BR24L01AFJ-W / BR24L01AFV-W / BR24L01AFVM-W

6) Acknowledge

- Acknowledge is a software convention used to indicate successful data transfers.

- The transmitter device will release the bus after transmitting eight bits.

(When inputting the slave address in the write or read operation, transmitter is µ-COM. When outputting the data in the read operation, it is this device.)

• During the ninth clock cycle, the receiver will pull the SDA line LOW to Acknowledge that the eight bits of data has been received.

(When inputting the slave address in the write or read operation, receiver is this device. When outputting the data in the read operation, it is  $\mu$ -COM.)

- www.DataSheet4U.com. The device will respond with an Acknowledge after recognition of a START condition and its slave address (8bit).

- In the WRITE mode, the device will respond with an Acknowledge, after the receipt of each subsequent 8-bit word (word address and write data).

- In the READ mode, the device will transmit eight bit of data, release the SDA line, and monitor the line for an Acknowledge.

- If an Acknowledge is detected, and no STOP condition is generated by the master, the device will continue to transmit the data. If an Acknowledge is not detected, the device will terminate further data transmissions and await a STOP condition before returning to the standby mode. (See Fig.7 ACKNOWLEDGE RESPONSE FROM RECEIVER)

Fig.7 ACKNOWLEDGE RESPONSE FROM RECEIVER

## BR24L01A-W / BR24L01AF-W / BR24L01AFJ-W / BR24L01AFV-W / BR24L01AFVM-W

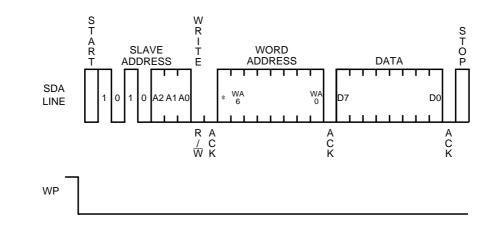

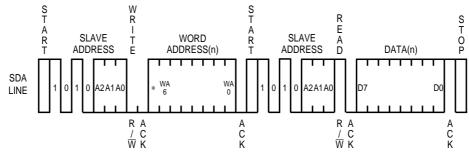

#### Byte write

## Fig.8 BYTE WRITE CYCLE TIMING

- By using this command, the data is programmed into the indicated word address.

- When the master generates a STOP condition, the device begins the internal write cycle to the nonvolatile memory array.

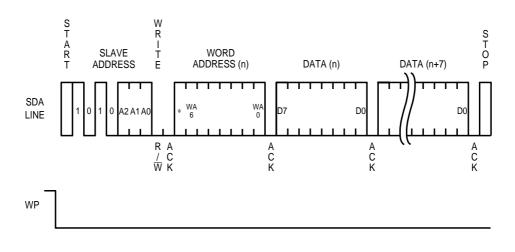

#### Page write

#### Fig.9 PAGE WRITE CYCLE TIMING

- This device is capable of eight byte page write operation.

- When two or more byte data are inputted, the three low order address bits are internally incremented by one after the receipt of each word. The four higher order bits of the address (WA6 to WA3) remain constant.

- If the master transmits more than eight words, prior to generating the STOP condition, the address counter will "roll over", and the previous transmitted data will be overwritten.

## BR24L01A-W / BR24L01AF-W / BR24L01AFJ-W / BR24L01AFV-W / BR24L01AFVM-W

#### Current read

ww.DataSheet4U.com

Fig.10 CURRENT READ CYCLE TIMING

- In case that the previous operation is Random or Current Read (which includes Sequential Read respectively), the internal address counter is increased by one from the last accessed address (n).

Thus Current Read outputs the data of the next word address (n+1).

If the last command is Byte or Page Write, the internal address counter stays at the last address (n).

Thus Current Read outputs the data of the word address (n).

- If an Acknowledge is detected, and no STOP condition is generated by the master (μ-COM), the device will continue to transmit the data. [ It can transmit all data (1kbit 128word) ]

- If an Acknowledge is not detected, the device will terminate further data transmissions and await a STOP condition before returning to the standby mode.

- Note) If an Acknowledge is detected with "Low" level, not "High" level, command will become Sequential Read. So the device transmits the next data, Read is not terminated. In the case of terminating Read, input Acknowledge with "High" always, then input stop condition.

#### Random read

Fig.11 RANDOM READ CYCLE TIMING

- Random read operation allows the master to access any memory location indicated word address.

- If an Acknowledge is detected, and no STOP condition is generated by the master (μ-COM), the device will continue to transmit the data. [ It can transmit all data (1kbit 128word) ]

- If an Acknowledge is not detected, the device will terminate further data transmissions and await a STOP condition before returning to the standby mode.

Note) If an Acknowledge is detected with "Low" level, not "High" level, command will become Sequential Read. So the device transmits the next data, Read is not terminated. In the case of terminating Read, input Acknowledge with "High" always, then input stop condition.

## BR24L01A-W / BR24L01AF-W / BR24L01AFJ-W / BR24L01AFV-W / BR24L01AFVM-W

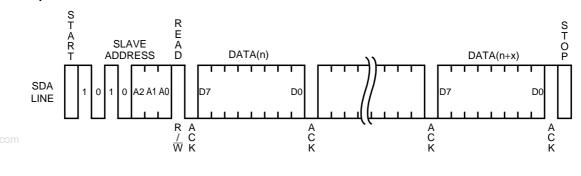

Sequential read

Fig.12 SEQUENTIAL READ CYCLE TIMING (Current Read)

- If an Acknowledge is detected, and no STOP condition is generated by the master (μ-COM), the device will continue to transmit the data. [ It can transmit all data (1kbit 128word) ]

- If an Acknowledge is not detected, the device will terminate further data transmissions and await a STOP condition before returning to the standby mode.

- The Sequential Read operation can be performed with both Current Read and Random Read.

- Note) If an Acknowledge is detected with "Low" level, not "High" level, command will become Sequential Read. So the device transmits the next data, Read is not terminated. In the case of terminating Read, input Acknowledge with "High" always, then input stop condition.

## BR24L01A-W / BR24L01AF-W / BR24L01AFJ-W / BR24L01AFV-W / BR24L01AFVM-W

#### Application

1) WP effective timing

WP is fixed to "H" or "L" usually. But in case of controlling WP to cancel the write command, please pay attention to [WP effective timing] as follows.

During write command input, write command is canceled by controlling WP "H" within the WP cancellation effective period.

The period from the start condition to the rising edge of the clock which take in D0 of the data (the first byte of the data for Page Write) is the cancellation invalid period. WP input is don't care during the period. Setup time for rising edge of the SCL which takes in D0 must be more than 100ns.

www.DataSheet4U.com

<sup>Th</sup> The period from the rising edge of SCL which takes in D0 to the end of internal write cycle (twR) is the cancellation effective period. In case of setting WP to "H" during twR, WRITE operation is stopped in the middle and the data of accessing address is not guaranteed, so that write correct data again please.

It is not necessary waiting twR (5msmax.) after stopping command by WP, because the device is stand by state.

Fig.13 WP EFFECTIVE TIMING

## BR24L01A-W / BR24L01AF-W / BR24L01AFJ-W / BR24L01AFV-W / BR24L01AFVM-W

#### 2) Software reset

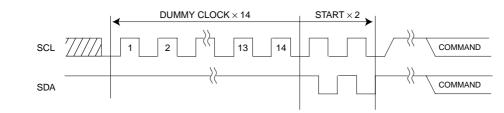

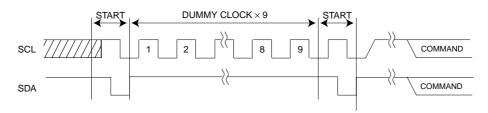

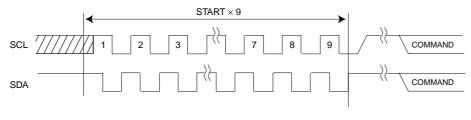

Please execute software reset in case that the device is an unexpected state after power up and / or the command input need to be reset.

There are some kinds of software reset. Here we show three types of example as follows.

During dummy clock, please release SDA bus ( tied to VCC by pull up resistor ).

During that time, the device may pull the SDA line LOW for Acknowledge or outputting or read data.

If the master controls the SDA line HIGH, it will conflict with the device output LOW then it makes a current overload. It may cause instantaneous power down and may damage the device.

Fig.14-(a) DUMMY CLOCK × 14 + START + START

Fig.14-(b) START+ DUMMY CLOCK × 9 + START

Fig.14-(c) START × 9

$\ast$  COMMAND starts with start condition.

## BR24L01A-W / BR24L01AF-W / BR24L01AFJ-W / BR24L01AFV-W / BR24L01AFVM-W

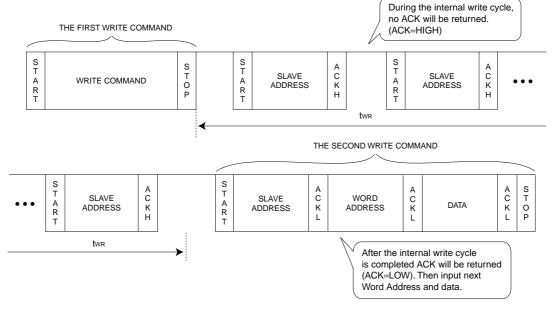

#### 3) Acknowledge polling

Since the device ignore all input commands during the internal write cycle, no ACK will be returned. When the master send the next command after the wire command, if the device returns the ACK, it means that the program is completed. If no ACK id returned, it means that the device is still busy. By using Acknowledge polling, the waiting time is minimized less than twR=5ms.

In case of operating Write or Current Read right after Write, first, send the slave address (R/W is "HIGH" or "LOW" respectively). After the device returns the ACK, continue word address input or data output respectively.

Fig.15 SUCCESSIVE WRITE OPERATION BY ACKNOWLEDGE POLLING

## BR24L01A-W / BR24L01AF-W / BR24L01AFJ-W / BR24L01AFV-W / BR24L01AFVM-W

4) Command cancellation by start and stop condition

During a command input, it is canceled by the successive inputs of start condition and stop condition. (Fig.4) But during ACK or data output, the device may output the SDA line LOW. In such cases, operation of start and stop condition is impossible, so that the reset can't work. Execute the software reset in the cases. (See Page14) Operating the command cancel by start and stop condition during the command of Random Read or Sequential Read or Current Read, internal address counter is not confirmed.

Therefore operation of Current Read after this in not valid. Operate a Random Read in this case.

www.DataSheet4U.com

Fig.16 COMMAND CANCELLATION BY START AND STOP CONDITION DURING THE INPUT OF SLAVE ADDRESS

## BR24L01A-W / BR24L01AF-W / BR24L01AFJ-W / BR24L01AFV-W / BR24L01AFVM-W

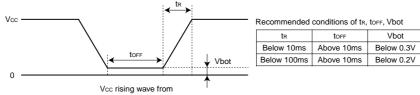

5) Notes for power supply

Vcc rises through the low voltage region in which internal circuit of IC and the controller are unstable, so that device may not work properly due to an incomplete reset of internal circuit.

To prevent this, the device has the feature of P.O.R. and LVcc.

In the case of power up, keep the following conditions to ensure functions of P.O.R and LVCC.

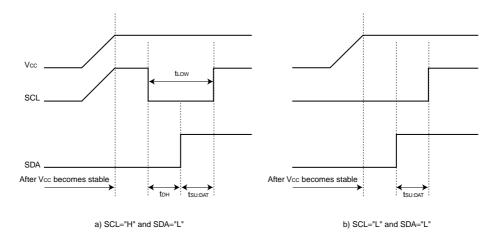

(1) It is necessary to be "SDA=H" and "SCL='L' or 'H' ".

(2) Follow the recommended conditions of tR, tOFF, Vbot for the function of P.O.R. duming power up.

### (3) Prevent SDA and SCL from being "Hi-Z".

In case that condition 1. and / or 2. cannot be met, take following actions. A) Unable to keep condition 1. (SDA is "LOW" during power up.)

$\rightarrow$  Control SDA, SCL to be "HIGH" as figure below.

B) Unable to keep condition 2.

$\rightarrow$ After power becomes stable, execute software reset. (See page14)

C) Unable to keep condition 1 and 2.

$\rightarrow$ Follow the instruction A first, then the instruction B.

## BR24L01A-W / BR24L01AF-W / BR24L01AFJ-W / BR24L01AFV-W / BR24L01AFVM-W

#### • LVcc circuit

LVcc circuit inhibit write operation at low voltage, and prevent an inadvertent write. Below the LVcc voltage (Typ.=1.2V), write operation is inhibited.

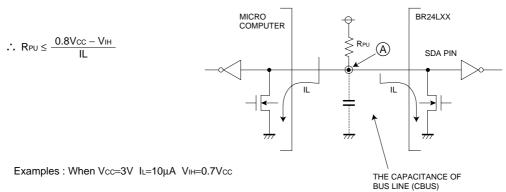

#### 6) I / O circuit

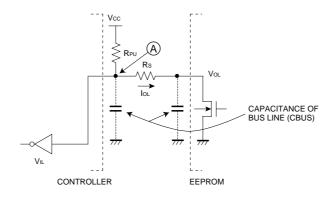

• Pull up resister of SDA pin

The pull up resister is needed because SDA is NMOS open drain. Decide the value of this resister (RPU) properly, by considering VIL, IL characteristics of a controller which control the device and VOH, IOL characteristics of the device. If large RPU is chosen, clock frequency need to be slow. In case of small RPU, the operating current increases.

#### • Maximum of RPU

Maximum of RPU is determined by following factor.

- ① SDA rise time determined by RPU and the capacitance of bus line (CBUS) must be less than TR. And the other timing must keep the conditions of AC spec.

- When SDA bus is HIGH, the voltage A of SDA bus determined by a total input leak (IL) of the all devices connected to the bus and RPU must be enough higher than input HIGH level of a controller and the device, including noise margin 0.2 Vcc.

$V\text{cc} - I\text{L}R\text{PU} - 0.2V\text{cc} \geq V\text{IH}$

According to 2

$$R_{PU} \le \frac{0.8 \times 3 - 0.7 \times 3}{10 \times 10^{-6}} \le 300 \text{ [k}\Omega\text{]}$$

## BR24L01A-W / BR24L01AF-W / BR24L01AFJ-W / BR24L01AFV-W / BR24L01AFVM-W

• The minimum value RPU

The minimum value of RPU is determined by following factors.

0 Meet the condition that Volmax=0.4V, Iolmax=3mA when the device output low on SDA line.

$$\frac{|V_{CC} - V_{OL}|}{|R_{PU}|} \le |OL|$$

$$\therefore R_{PU} \ge \frac{V_{CC} - V_{OL}}{I_{OL}}$$

ww.DataSheet4U.com

② VOLMAX (=0.4V) must be lower than the input LOW level of the controller and the EEPROM including recommended noise margin (0.1 Vcc).

$V_{\text{OLMAX}} \leq V_{\text{IL}} - 0.1 \text{Vcc}$

Examples : Vcc=3V, VoL=0.4V, IoL=3mA, the VIL of the controller and the EEPROM is VIL=0.3Vcc

| According to $\textcircled{1}$ | $R_{PU} \ge \frac{3-0.4}{3 \times 10^{-3}}$ |

|--------------------------------|---------------------------------------------|

|                                | ≥ 867 [Ω]                                   |

| and                            | Vol=0.4[V]<br>Vil=0.3×3<br>=0.9[V]          |

so that condition (2) is met

```

• Pull up resister of SCL pin

```

In the case that SCL is controlled by CMOS output, the pull up resister of SCL is not needed. But in the case that there is a timing at which SCL is Hi-Z, connect SCL to Vcc with pull up resister. Several ~ several dozen  $k\Omega$  is recommended as a pull up resister, which is considered with the driving ability of the output port of the controller.

#### 7) Connections of A0, A1, A2, WP pin

• Connections of device address pin (A0, A1, A2)

The state of device address PIN are compared with the device address send by the master, then one of the devices which are connected to the identical bus is selected. Pull up or down these pins, or connect them to Vcc or GND. Pins which is not used as device address (N.C. PIN) may be either HIGH, LOW, and Hi-Z.

| The type of the device which have N.C. PIN | BR24L16/F/FJ/FV/FVM-W | A0, A1, A2 |

|--------------------------------------------|-----------------------|------------|

|                                            | BR24L08/F/FJ/FV/FVM-W | A0, A1     |

|                                            | BR24L04/F/FJ/FV/FVM-W | A0         |

• Connections of WP pin

The WP input allows or inhibits write operations. When WP is HIGH, only READ is available and WRITE to any address is inhibited. Both Read and Write are available when WP is LOW.

In the case that the device is used as a ROM, it is recommended that WP is pulled up or connected to Vcc. In the case that both READ and WRITE are operated, WP pin must be pulled down or connected to GND or controlled.

19/25

## BR24L01A-W / BR24L01AF-W / BR24L01AFJ-W / BR24L01AFV-W / BR24L01AFVM-W

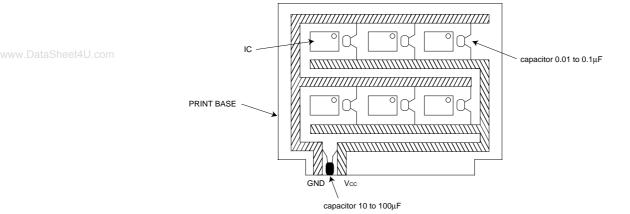

8) Notes for noise on Vcc

About bypass capacitor

Noise and surges on power line may cause the abnormal function. It is recommended that the bypass capacitors  $(0.1\mu F)$  are attached on the Vcc and GND line beside the device.

The attachment of bypass capacitors on the board near by connector is also recommended.

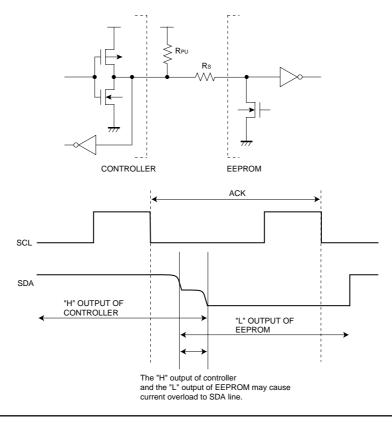

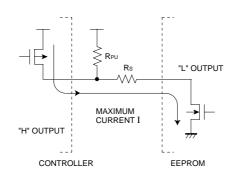

9) The notice about the connection of controller

About Rs

The open drain interface is recommended for SDA port in I<sup>2</sup>CBUS. But, in the case that Tri-state CMOS interface is applied to SDA, insert a series resister Rs between SDA pin of the device and a pull up resister RPU. It limits the current from PMOS of controller to NMOS of EEPROM.

Rs also protects SDA pin from surges. Therefore, Rs is able to be used though SDA port is open drain.

ROHM

## BR24L01A-W / BR24L01AF-W / BR24L01AFJ-W / BR24L01AFV-W / BR24L01AFVM-W

- The maximum value of Rs

- The maximum value of Rs is determined by following factors.

- ① SDA rise time determined by RPU and the capacitance of bus line (CBUS) of SDA must be less than tR. And the other timing must also keep the conditions of the AC timing.

- <sup>(2)</sup> When the device outputs LOW on SDA line, the voltage of the bus determined by RPU and RS must be lower than the inputs LOW level of the controller, including recommended noise margin (0.1Vcc).

$$\frac{(V_{CC}-V_{OL}) \times R_{S}}{R_{PU}+R_{S}} + V_{OL}+0.1V_{CC} \le V_{IL}$$

www.DataSheet4U.com

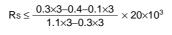

$$\therefore Rs \leq \frac{V_{IL} - V_{OL} - 0.1V_{CC}}{1.1V_{CC} - V_{IL}} \times R_{PU}$$

Examples : when Vcc=3V, VIL=0.3Vcc, VoL=0.4V, RPU=20k\Omega

According to 2

• The minimum value of Rs

The minimum value of Rs is determined by the current overload due to the conflict on the bus.

The current overload may cause noise on the power line and instantaneous power down.

The following conditions must be met, where I is the maximum permissible current.

The maximum permissible current depends on Vcc line impedance and so on. It need to be less than 10mA for EEPROM.

$$\frac{Vcc}{Rs} \le I$$

Examples : When Vcc=3V, I=10mA

$$R_{S} \geq \frac{3}{10 \times 10^{-3}}$$

$$\geq 300 \ [\Omega]$$

## BR24L01A-W / BR24L01AF-W / BR24L01AFJ-W / BR24L01AFV-W / BR24L01AFVM-W

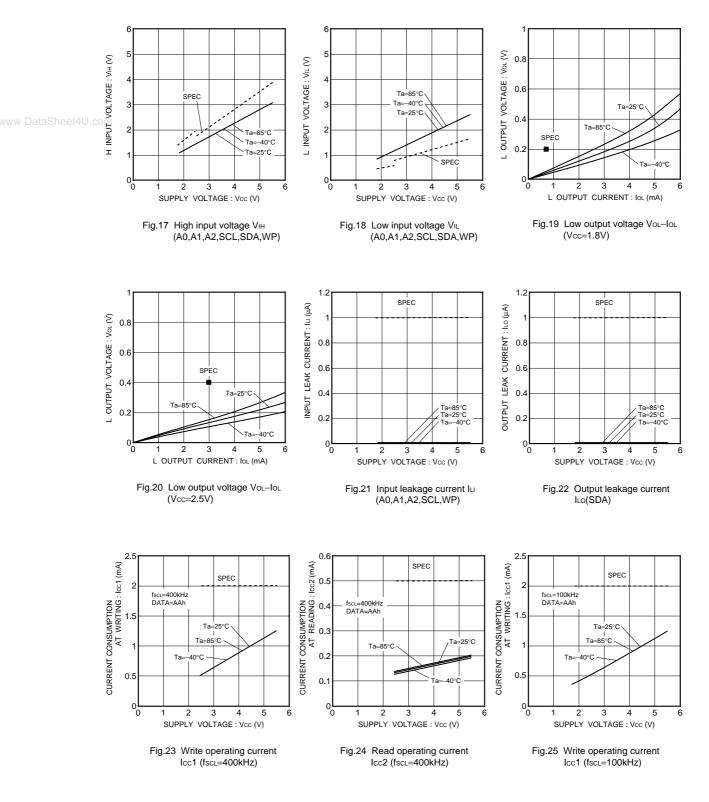

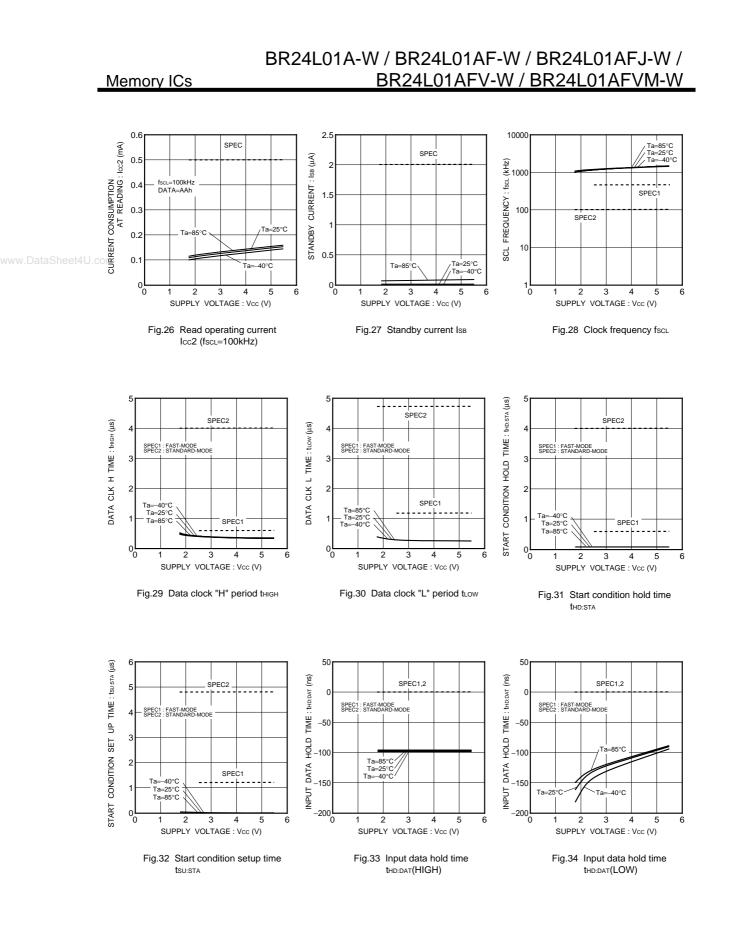

10) The special character DATA

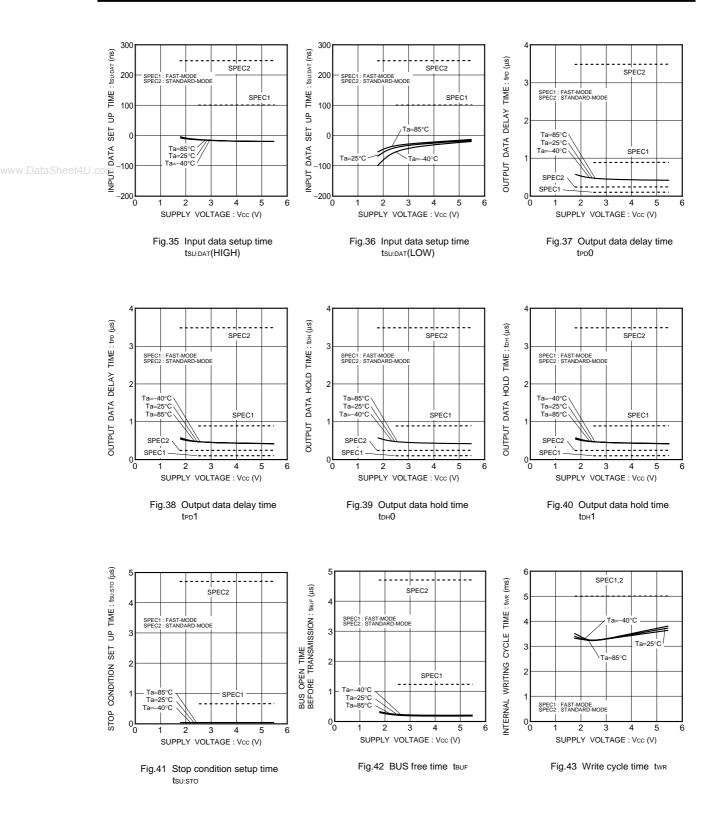

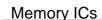

The following characteristic data are typ value.

Rohm

Rohm

23/25

## BR24L01A-W / BR24L01AF-W / BR24L01AFJ-W / BR24L01AFV-W / BR24L01AFVM-W

ROHM

24/25

## BR24L01A-W / BR24L01AF-W / BR24L01AFJ-W / BR24L01AFV-W / BR24L01AFVM-W

### Appendix

reliability and the malfunction of with would directly endanger human life (such as medical instruments, transportation equipment, aerospace machinery, nuclear-reactor controllers, fuel controllers and other safety devices), please be sure to consult with our sales representative in advance.

About Export Control Order in Japan

Products described herein are the objects of controlled goods in Annex 1 (Item 16) of Export Trade Control Order in Japan.

In case of export from Japan, please confirm if it applies to "objective" criteria or an "informed" (by MITI clause) on the basis of "catch all controls for Non-Proliferation of Weapons of Mass Destruction.

rohm