# **NAND Flash Memory**

MT29F32G08CBABA, MT29F64G08C[E/F]ABA, MT29F128G08C[J/K/M]ABA, MT29F256G08CUABA, MT29F32G08CBABB, MT29F32G08CBCBB, MT29F64G08CFABB, MT29F64G08CECBB, MT29F128G08CJABB, MT29F128G08C[K/M]CBB, MT29F256G08CUCBB

## Features

- Open NAND Flash Interface (ONFI) 2.1-compliant<sup>1</sup>

- Multiple-level cell (MLC) technology

- Organization

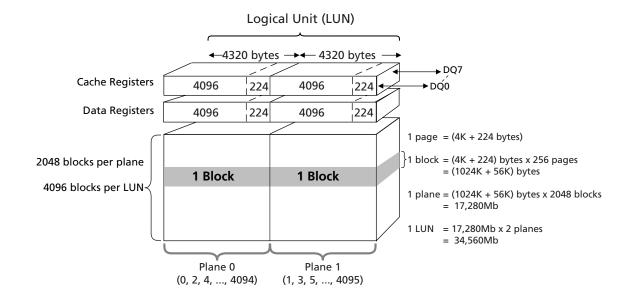

- Page size x8: 4320 bytes (4096 + 224 bytes)

- Block size: 256 pages (1024K + 56K bytes)

- Plane size: 2 planes x 2048 blocks per plane

- Device size: 32Gb: 4096 blocks;

64Gb: 8192 blocks;

128Gb: 16,384 blocks;

256Cb: 32,768 blocks;

- 256Gb: 32,768 blocks • Synchronous I/O performance

- Up to synchronous timing mode 4

- Clock rate: 12ns (DDR)

- Read/write throughput per pin: 166 MT/s

- Asynchronous I/O performance

- Up to asynchronous timing mode 4

- <sup>t</sup>RC/<sup>t</sup>WC: 25ns (MIN)

- Array performance

- Read page: 50µs (MAX)

- Program page: 900µs (TYP)

- Erase block: 3ms (TYP)

- Operating Voltage Range

- V<sub>CC</sub>: 2.7–3.6V

- V<sub>CCQ</sub>: 1.7–1.95V, 2.7–3.6V

- Command set: ONFI NAND Flash Protocol

- Advanced Command Set

- Program cache

- Read cache sequential

- Read cache random

- One-time programmable (OTP) mode

- Multi-plane commands

- Multi-LUN operations

- Read unique ID

- Copyback

- First block (block address 00h) is valid when shipped from factory. For minimum required ECC, see Error Management (page 108).

- RESET (FFh) required as first command after poweron

- Operation status byte provides software method for detecting

- Operation completion

- Pass/fail condition

- Write-protect status

- Data strobe (DQS) signals provide a hardware method for synchronizing data DQ in the synchronous interface

- Copyback operations supported within the plane from which data is read

- Quality and reliability

- Data retention: 10 years

- Endurance: 5000 PROGRAM/ERASE cycles

- Operating temperature:

- Commercial: 0°C to +70°C

- Industrial (IT): –40°C to +85°C

- Package

- 52-pad LGA

- 48-pin TSOP

- 100-ball BGA

- Note: 1. The ONFI 2.1 specification is available at www.onfi.org.

PDF: 09005aef836c9ded Rev. F 12/09 EN 1

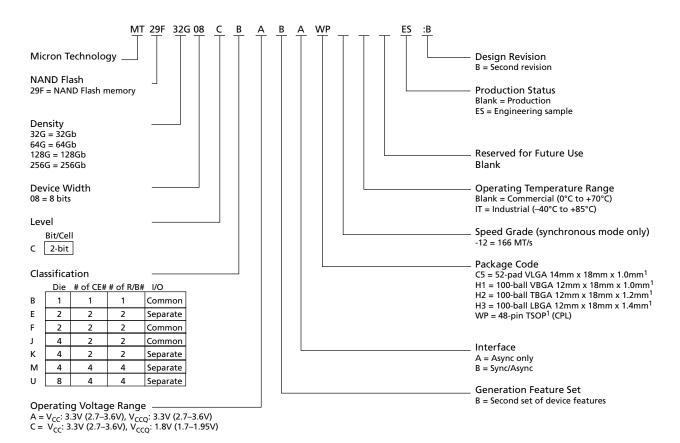

## **Part Numbering Information**

Micron NAND Flash devices are available in different configurations and densities. Verify valid part numbers by using Micron's part catalog search at www.micron.com. To compare features and specifications by device type, visit www.micron.com/products. Contact the factory for devices not found.

#### Figure 1: Part Numbering

Note: 1. Pb-free package.

## Contents

| General Description                              |    |

|--------------------------------------------------|----|

| Asynchronous and Synchronous Signal Descriptions |    |

| Signal Assignments                               | 11 |

| Package Dimensions                               | 14 |

| Architecture                                     |    |

| Device and Array Organization                    | 20 |

| Bus Operation – Asynchronous Interface           | 27 |

| Asynchronous Enable/Standby                      |    |

| Asynchronous Bus Idle                            | 27 |

| Asynchronous Commands                            | 28 |

| Asynchronous Addresses                           | 29 |

| Asynchronous Data Input                          | 30 |

| Asynchronous Data Output                         | 31 |

| Write Protect                                    | 32 |

| Ready/Busy#                                      | 32 |

| Bus Operation – Synchronous Interface            | 37 |

| Synchronous Enable/Standby                       | 38 |

| Synchronous Bus Idle/Driving                     | 38 |

| Synchronous Commands                             | 39 |

| Synchronous Addresses                            | 40 |

| Synchronous DDR Data Input                       | 41 |

| Synchronous DDR Data Output                      | 42 |

| Write Protect                                    | 44 |

| Ready/Busy#                                      | 44 |

| Device Initialization                            | 45 |

| Activating Interfaces                            | 46 |

| Activating the Asynchronous Interface            |    |

| Activating the Synchronous Interface             | 46 |

| Command Definitions                              | 48 |

| Reset Operations                                 |    |

| RESET (FFh)                                      | 50 |

| SYNCHRONOUS RESET (FCh)                          |    |

| Identification Operations                        |    |

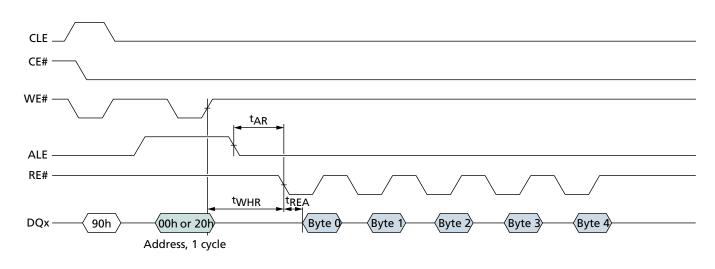

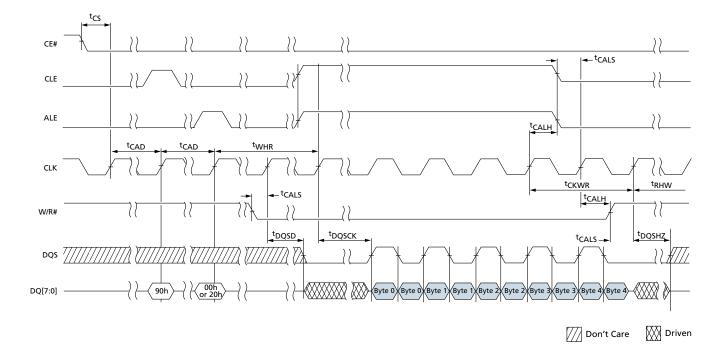

| READ ID (90h)                                    |    |

| READ ID Parameter Tables                         |    |

| Configuration Operations                         |    |

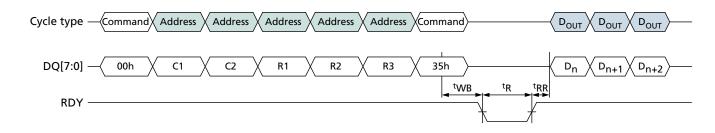

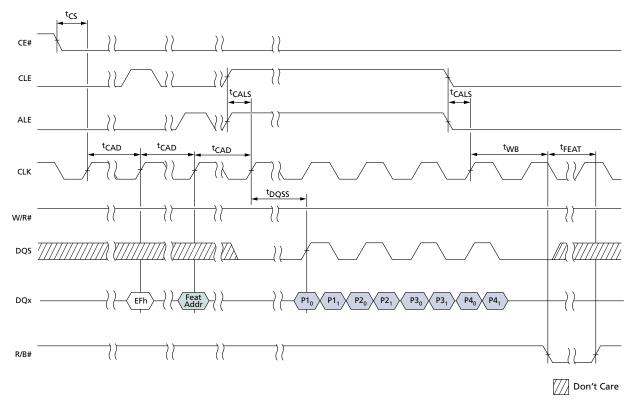

| SET FEATURES (EFh)                               |    |

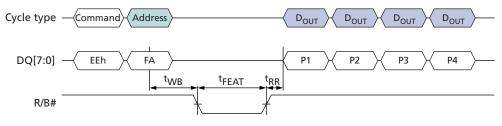

| GET FEATURES (EEh)                               |    |

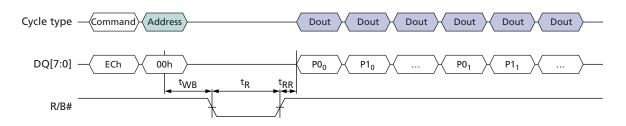

| READ PARAMETER PAGE (ECh)                        |    |

| Parameter Page Data Structure Tables             |    |

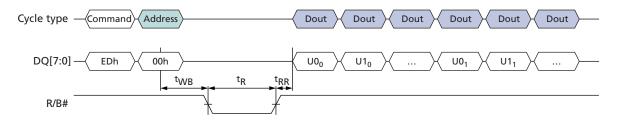

| READ UNIQUE ID (EDh)                             |    |

| Status Operations                                |    |

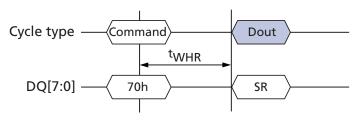

| READ STATUS (70h)                                |    |

| READ STATUS ENHANCED (78h)                       |    |

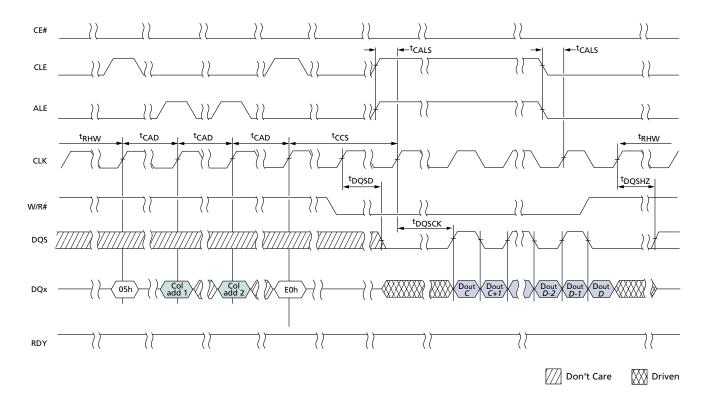

| Column Address Operations                        | 75 |

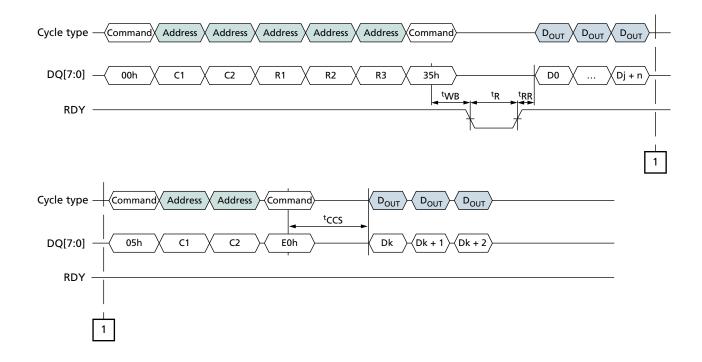

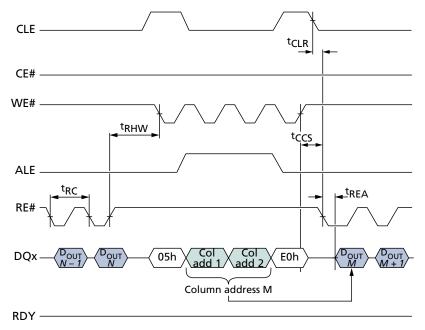

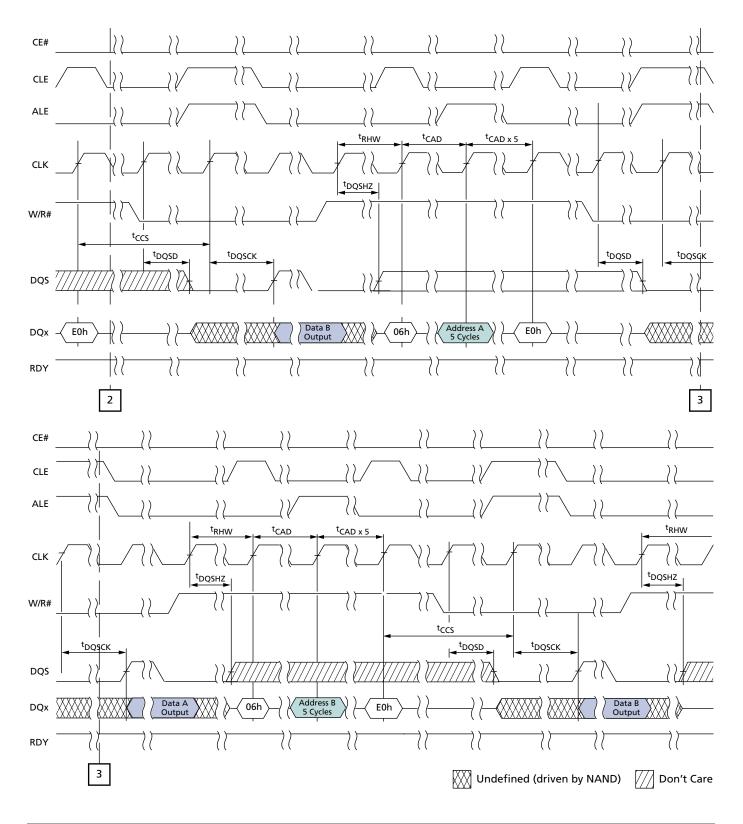

| CHANGE READ COLUMN (05h-E0h)                     | 75 |

| CHANGE READ COLUMN ENHANCED (06h-E0h)            |    |

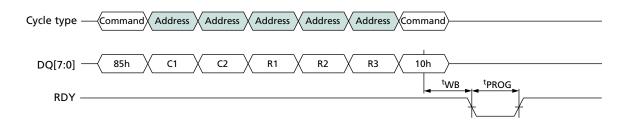

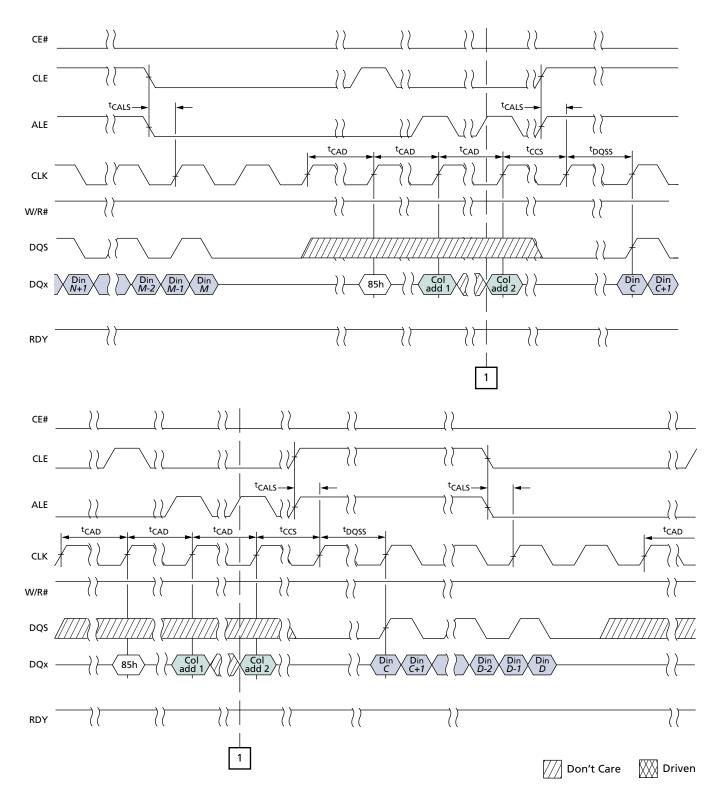

| CHANGE WRITE COLUMN (85h)                        |    |

| CHANGE ROW ADDRESS (85h)                         |    |

| Read Operations                                  | 80 |

| READ MODE (00h)                                                                             | . 82 |

|---------------------------------------------------------------------------------------------|------|

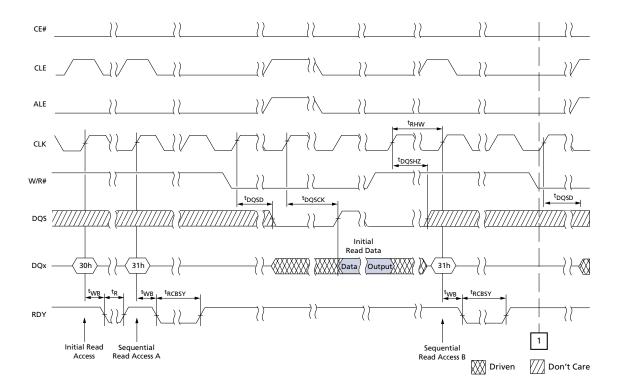

| READ PAGE (00h-30h)                                                                         | . 83 |

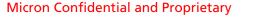

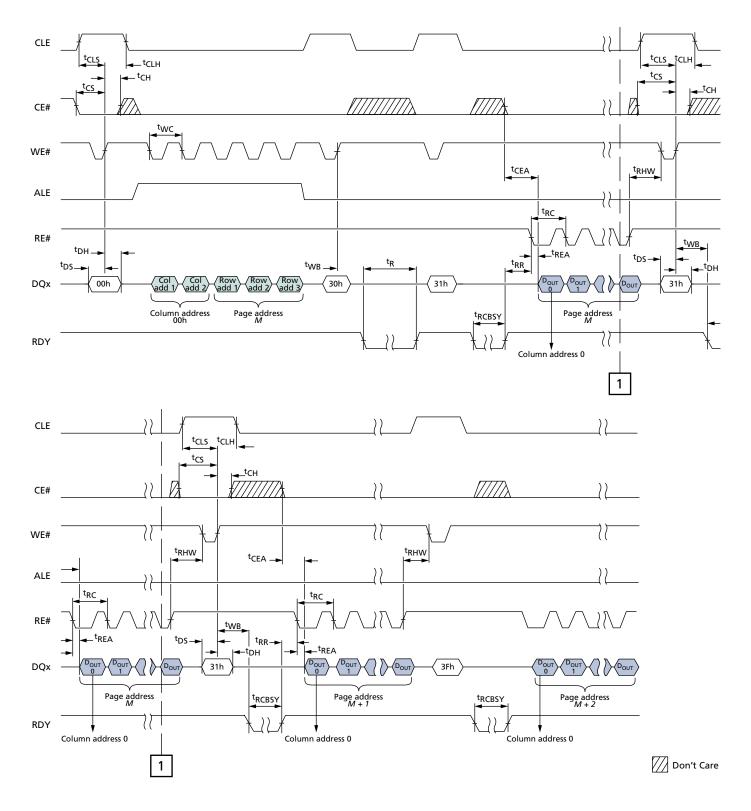

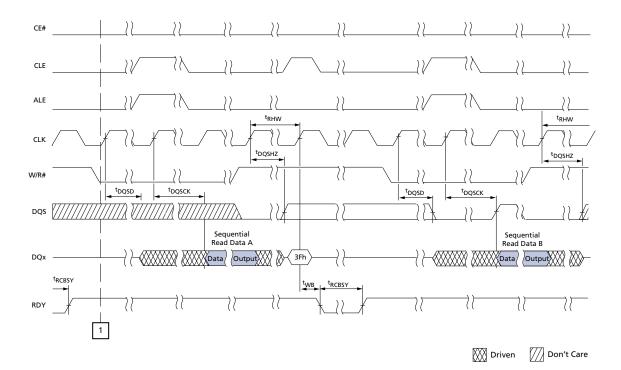

| READ PAGE CACHE SEQUENTIAL (31h)                                                            | . 84 |

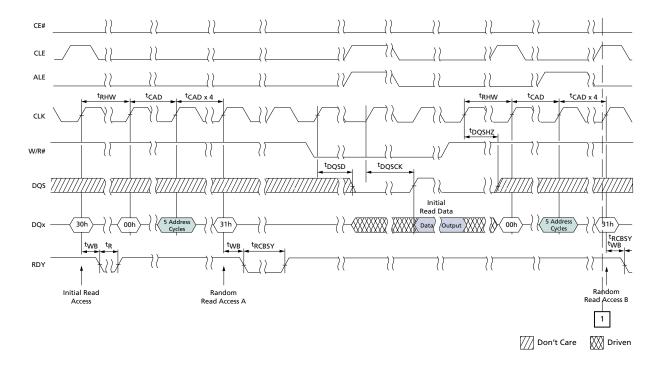

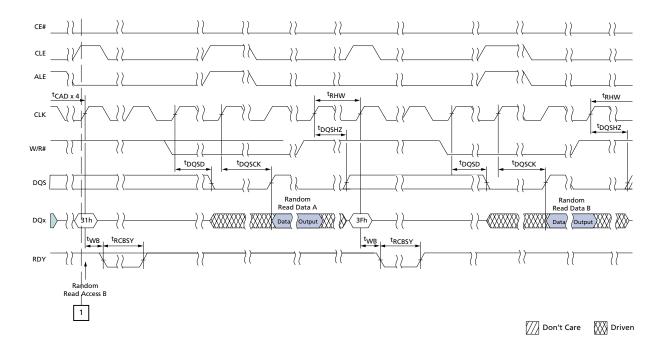

| READ PAGE CACHE RANDOM (00h-31h)                                                            | . 85 |

| READ PAGE CACHE LAST (3Fh)                                                                  | . 87 |

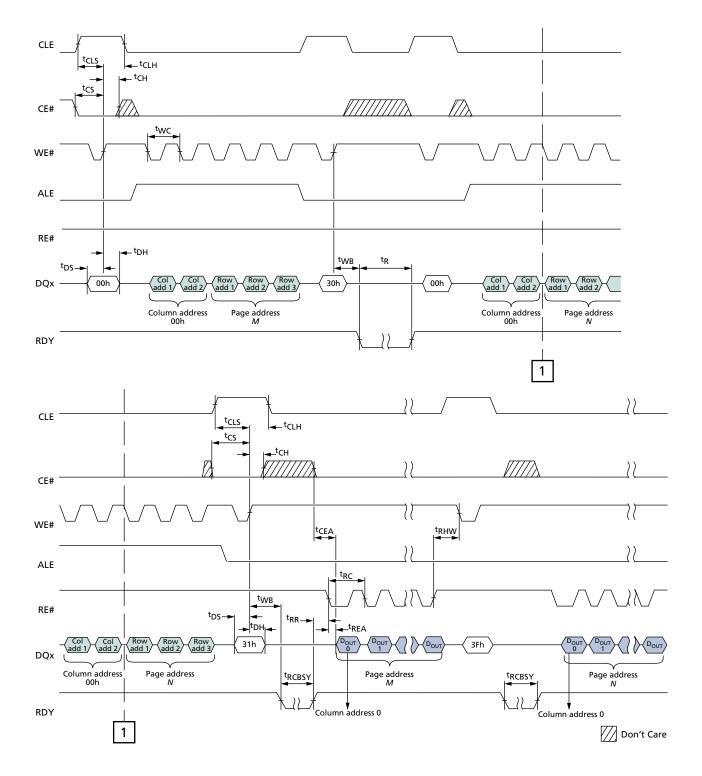

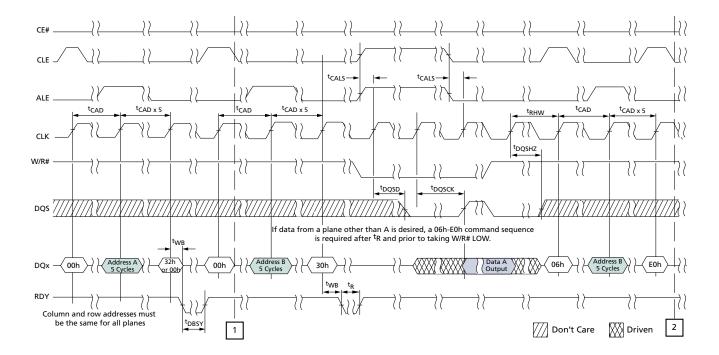

| READ PAGE MULTI-PLANE (00h-32h)                                                             | . 88 |

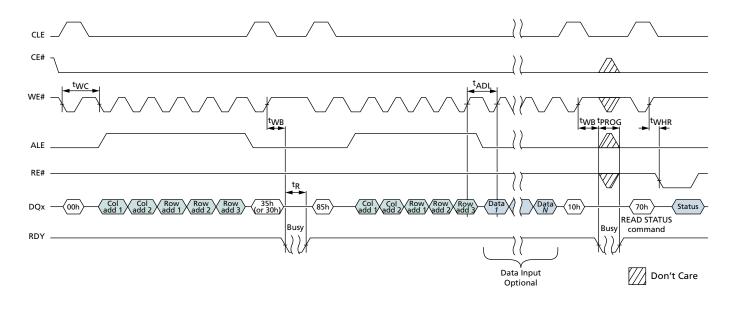

| Program Operations                                                                          | . 90 |

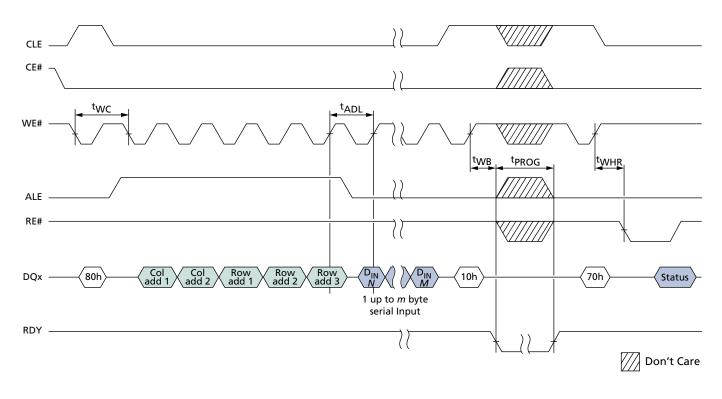

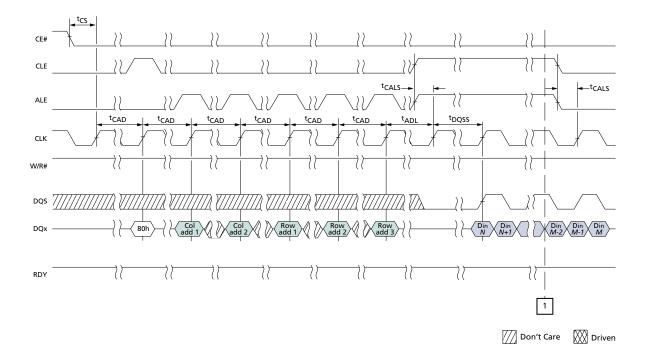

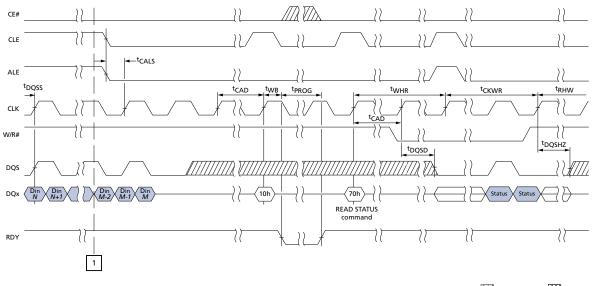

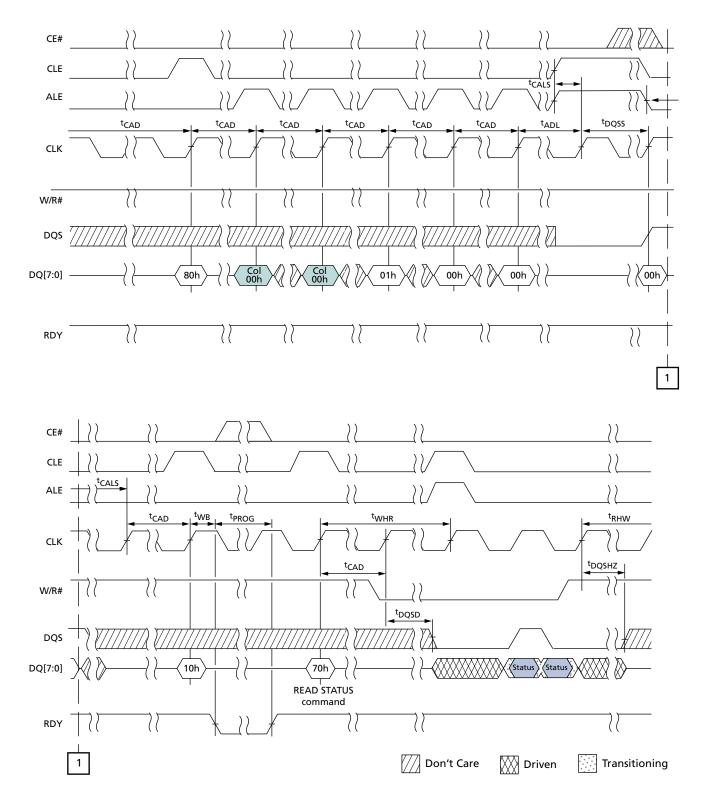

| PROGRAM PAGE (80h-10h)                                                                      | . 90 |

| PROGRAM PAGE CACHE (80h-15h)                                                                | . 92 |

| PROGRAM PAGE MULTI-PLANE 80h-11h                                                            | . 94 |

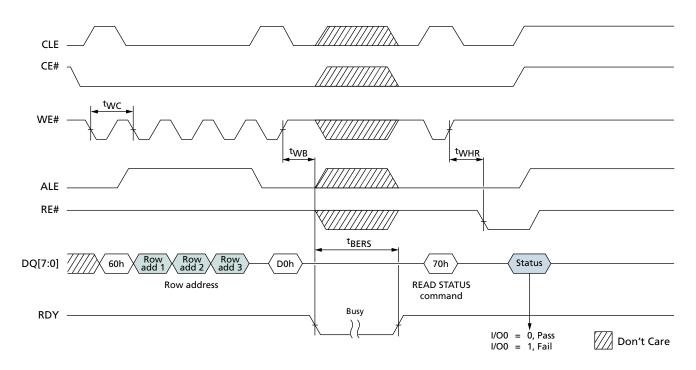

| Erase Operations                                                                            | . 96 |

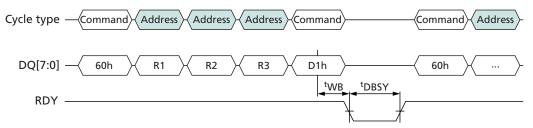

| ERASE BLOCK (60h-D0h)                                                                       | . 96 |

| ERASE BLOCK MULTI-PLANE (60h-D1h)                                                           | . 97 |

| Copyback Operations                                                                         | . 98 |

| COPYBACK READ (00h-35h)                                                                     | . 99 |

| COPYBACK PROGRAM (85h–10h)                                                                  | 100  |

| COPYBACK READ MULTI-PLANE (00h-32h)                                                         |      |

| COPYBACK PROGRAM MULTI-PLANE (85h-11h)                                                      | 101  |

| One-Time Programmable (OTP) Operations                                                      |      |

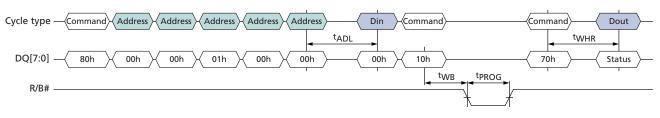

| PROGRAM OTP PAGE (80h-10h)                                                                  | 103  |

| PROTECT OTP AREA (80h-10h)                                                                  |      |

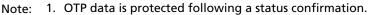

| READ OTP PAGE (00h-30h)                                                                     | 105  |

| Multi-Plane Operations                                                                      | 106  |

| Multi-Plane Addressing                                                                      |      |

| Interleaved Die (Multi-LUN) Operations                                                      | 107  |

| Error Management                                                                            |      |

| Output Drive Impedance                                                                      |      |

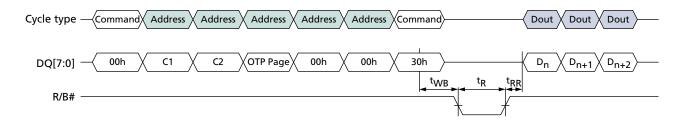

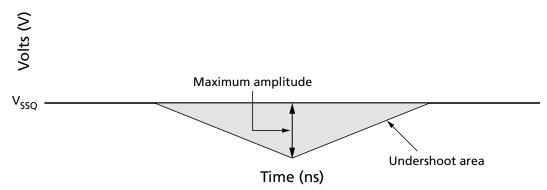

| AC Overshoot/Undershoot Specifications                                                      |      |

| Synchronous Input Slew Rate                                                                 |      |

| Output Slew Rate                                                                            |      |

| Electrical Specifications                                                                   |      |

| Electrical Specifications – DC Characteristics and Operating Conditions (Asynchronous)      | 117  |

| Electrical Specifications - DC Characteristics and Operating Conditions (Synchronous)       |      |

| Electrical Specifications – DC Characteristics and Operating Conditions (V <sub>CCQ</sub> ) |      |

| Electrical Specifications - AC Characteristics and Operating Conditions (Asynchronous)      |      |

| Electrical Specifications - AC Characteristics and Operating Conditions (Synchronous)       |      |

| Electrical Specifications – Array Characteristics                                           |      |

| Asynchronous Interface Timing Diagrams                                                      |      |

| Synchronous Interface Timing Diagrams                                                       |      |

| Revision History                                                                            |      |

| Rev. F, Production – 12/09                                                                  |      |

| Rev. E – 8/09                                                                               |      |

| Rev. D – 2/09                                                                               |      |

| Rev. C – 1/09                                                                               |      |

| Rev. B – 12/08                                                                              |      |

| Rev. A – 11/08                                                                              | 160  |

## **List of Tables**

|           | Asynchronous and Synchronous Signal Definitions                       |     |

|-----------|-----------------------------------------------------------------------|-----|

| Table 2:  | Array Addressing for Logical Unit (LUN)                               | 26  |

|           | Asynchronous Interface Mode Selection                                 |     |

| Table 4:  | Synchronous Interface Mode Selection                                  | 37  |

|           | Command Set                                                           |     |

| Table 6:  | Read ID Parameters for Address 00h                                    | 53  |

|           | Read ID Parameters for Address 20h                                    |     |

|           | Feature Address Definitions                                           |     |

|           | Feature Address 01h: Timing Mode                                      |     |

|           | Feature Addresses 10h and 80h: Programmable Output Drive Strength     |     |

| Table 11: | Feature Addresses 81h: Programmable R/B# Pull-Down Strength           | 57  |

| Table 12: | Feature Addresses 90h: Array Operation Mode                           | 57  |

| Table 13: | Parameter Page Data Structure                                         | 60  |

|           | Status Register Definition                                            |     |

|           | OTP Area Details                                                      |     |

|           | Error Management Details                                              |     |

|           | Output Drive Strength Test Conditions (V <sub>CCQ</sub> = 1.7–1.95V)  |     |

| Table 18: | Output Drive Strength Impedance Values (V <sub>CCQ</sub> = 1.7–1.95V) | 109 |

| Table 19: | Output Drive Strength Conditions ( $V_{CCQ} = 2.7 - 3.6V$ )           | 110 |

| Table 20: | Output Drive Strength Impedance Values ( $V_{CCQ} = 2.7 - 3.6V$ )     | 110 |

| Table 21: | Pull-Up and Pull-Down Output Impedance Mismatch                       | 111 |

| Table 22: | Overshoot/Undershoot Parameters                                       | 112 |

|           | Test Conditions for Input Slew Rate                                   |     |

| Table 24: | Input Slew Rate (V <sub>CCQ</sub> = 1.7–1.95V)                        | 113 |

| Table 25: | Input Slew Rate $(V_{CCQ} = 2.7 - 3.6V)$                              | 113 |

| Table 26: | Test Conditions for Output Slew Rate                                  | 114 |

| Table 27: | Output Slew Rate ( $V_{CCQ} = 1.7 - 1.95V$ )                          | 114 |

| Table 28: | Output Slew Rate ( $V_{CCQ} = 2.7 - 3.6V$ )                           | 114 |

| Table 29: | Absolute Maximum Ratings by Device                                    | 115 |

|           | Recommended Operating Conditions                                      |     |

| Table 31: | Valid Blocks per LUN                                                  | 115 |

|           | Capacitance: 100-Ball BGA Package                                     |     |

| Table 33: | Capacitance: 48-Pin TSOP Package                                      | 116 |

|           | Capacitance: 52-Pad LGA Package                                       |     |

|           | Test Conditions                                                       |     |

|           | DC Characteristics and Operating Conditions (Asynchronous Interface)  |     |

|           | DC Characteristics and Operating Conditions (Synchronous Interface)   |     |

|           | DC Characteristics and Operating Conditions (3.3V V <sub>CCQ</sub> )  |     |

| Table 39: | DC Characteristics and Operating Conditions (1.8V V <sub>CCQ</sub> )  | 119 |

|           | AC Characteristics: Asynchronous Command, Address, and Data           |     |

|           | AC Characteristics: Synchronous Command, Address, and Data            |     |

| Table 42: | Array Characteristics                                                 | 124 |

## **List of Figures**

| Figure 1:  | Part Numbering                                                                    | . 2 |

|------------|-----------------------------------------------------------------------------------|-----|

| Figure 2:  | 48-Pin TSOP Type 1 (Top View)                                                     | 11  |

| Figure 3:  | 52-Pad LGA (Top View)                                                             | 12  |

| Figure 4:  | 100-Ball BGA (Ball-Down, Top View)                                                | 13  |

| Figure 5:  | 48-Pin TSOP – Type 1 CPL (Package Code: WP)                                       | 14  |

| Figure 6:  | 52-Pad VLGA                                                                       | 15  |

| Figure 7:  | 100-Ball VBGA – 12mm x 18mm (Package Code: H1)                                    | 16  |

| Figure 8:  | 100-Ball TBGA – 12mm x 18mm (Package Code: H2)                                    | 17  |

| Figure 9:  | 100-Ball LBGA – 12mm x 18mm (Package Code: H3)                                    | 18  |

| Figure 10: | NAND Flash Die (LUN) Functional Block Diagram                                     | 19  |

|            | Device Organization for Single-Die Package (TSOP/BGA)                             |     |

| Figure 12: | Device Organization for Two-Die Package (TSOP)                                    | 20  |

|            | Device Organization for Two-Die Package (BGA/LGA)                                 |     |

| Figure 14: | Device Organization for Four-Die Package (TSOP)                                   | 22  |

| Figure 15: | Device Organization for Four-Die Package with CE# and CE2# (BGA/LGA)              | 23  |

| Figure 16: | Device Organization for Four-Die Package with CE#, CE2#, CE3#, and CE4# (BGA/LGA) | 24  |

| Figure 17: | Device Organization for Eight-Die Package (BGA/LGA)                               | 25  |

|            | Array Organization per Logical Unit (LUN)                                         |     |

| Figure 19: | Asynchronous Command Latch Cycle                                                  | 28  |

| Figure 20: | Asynchronous Address Latch Cycle                                                  | 29  |

|            | Asynchronous Data Input Cycles                                                    |     |

| Figure 22: | Asynchronous Data Output Cycles                                                   | 31  |

| Figure 23: | Asynchronous Data Output Cycles (EDO Mode)                                        | 32  |

|            | READ/BUSY# Open Drain                                                             |     |

| Figure 25: | <sup>t</sup> Fall and <sup>t</sup> Rise ( $\dot{V}_{CCO} = 2.7-3.6V$ )            | 34  |

|            | <sup>t</sup> Fall and <sup>t</sup> Rise ( $V_{CCO} = 1.7-1.95V$ )                 |     |

| Figure 27: | IOL vs Rp ( $V_{CCO} = 2.7-3.6V$ )                                                | 35  |

|            | IOL vs Rp ( $V_{CCO} = 1.7-1.95V$ )                                               |     |

| Figure 29: | TC vs Rp                                                                          | 36  |

| Figure 30: | Synchronous Bus Idle/Driving Behavior                                             | 39  |

| Figure 31: | Synchronous Command Cycle                                                         | 40  |

| Figure 32: | Synchronous Address Cycle                                                         | 41  |

| Figure 33: | Synchronous DDR Data Input Cycles                                                 | 42  |

| Figure 34: | Synchronous DDR Data Output Cycles                                                | 44  |

|            | R/B# Power-On Behavior                                                            |     |

| Figure 36: | Activating the Synchronous Interface                                              | 47  |

| Figure 37: | RESET (FFh) Operation                                                             | 50  |

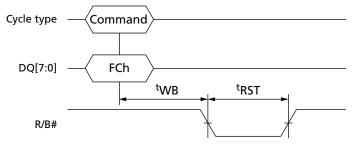

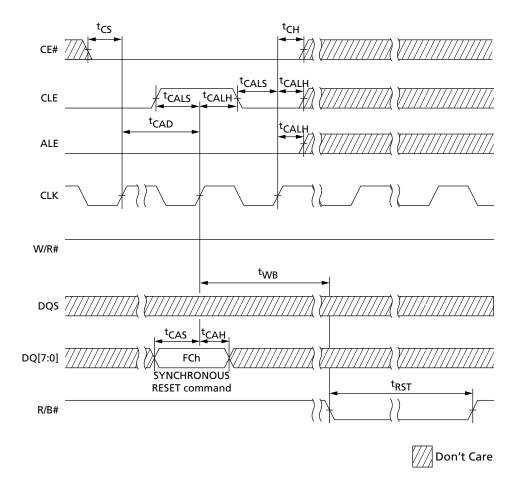

| Figure 38: | SYNCHRONOUS RESET (FCh) Operation                                                 | 51  |

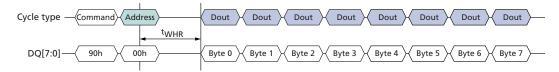

| Figure 39: | READ ID (90h) with 00h Address Operation                                          | 52  |

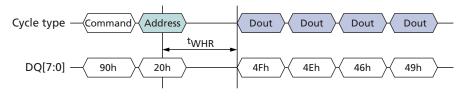

| Figure 40: | READ ID (90h) with 20h Address Operation                                          | 52  |

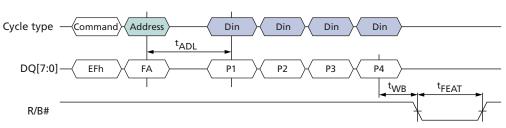

| Figure 41: | SET FEATURES (EFh) Operation                                                      | 55  |

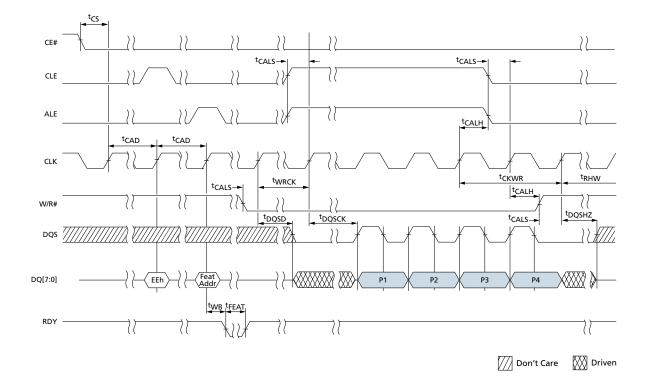

| Figure 42: | GET FEATURES (EEh) Operation                                                      | 55  |

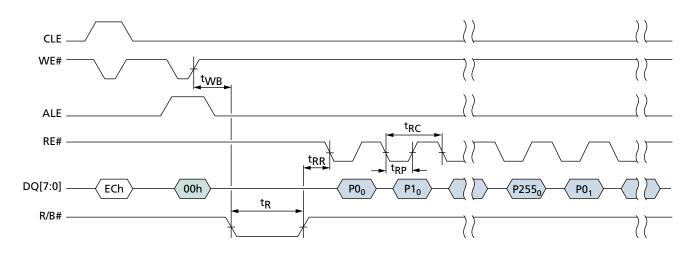

| Figure 43: | READ PARAMETER (ECh) Operation                                                    | 59  |

| Figure 44: | READ UNIQUE ID (EDh) Operation                                                    | 71  |

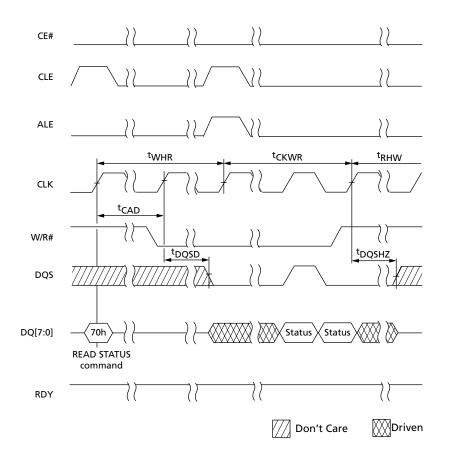

| Figure 45: | READ STATUS (70h) Operation                                                       | 74  |

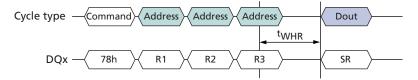

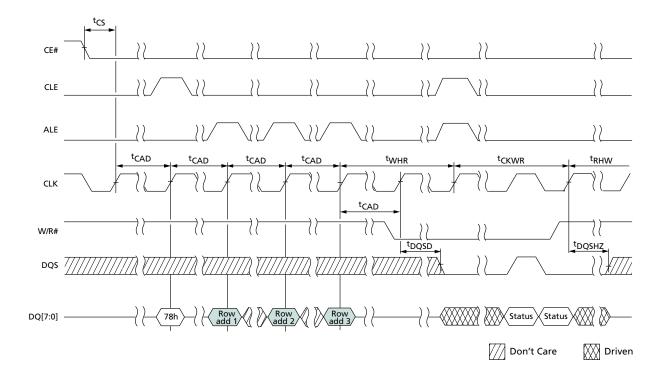

| Figure 46: | READ STATUS ENHANCED (78h) Operation                                              | 74  |

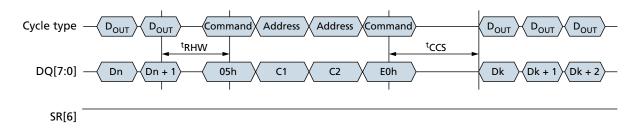

|            | CHANGE READ COLUMN (05h-E0h) Operation                                            |     |

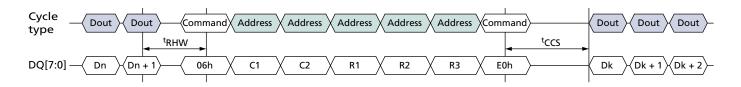

|            | CHANGE READ COLUMN ENHANCED (06h-E0h) Operation                                   |     |

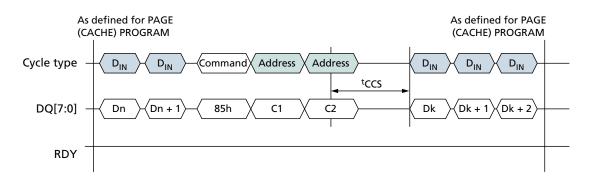

| Figure 49: | CHANGE WRITE COLUMN (85h) Operation                                               | 77  |

| Figure 50: | CHANGE ROW ADDRESS (85h) Operation                                                | 79  |

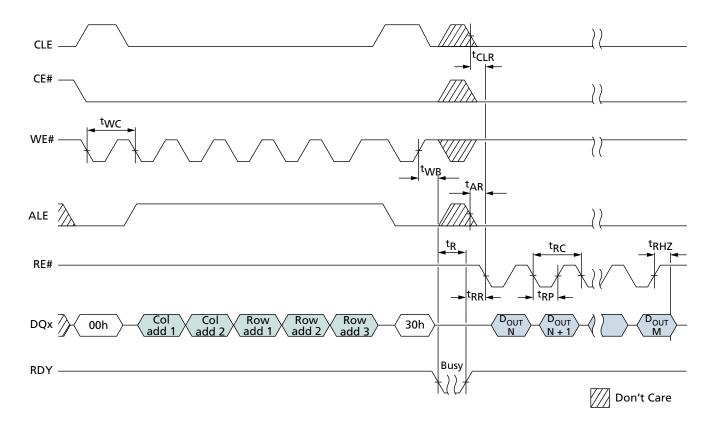

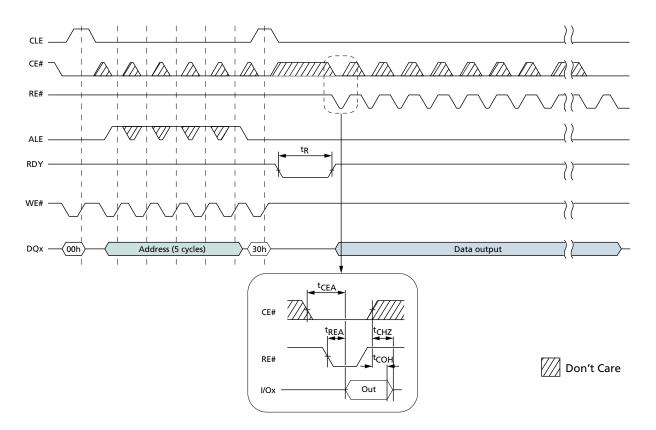

| Figure 51: | READ PAGE (00h-30h) Operation                                       | 83         |

|------------|---------------------------------------------------------------------|------------|

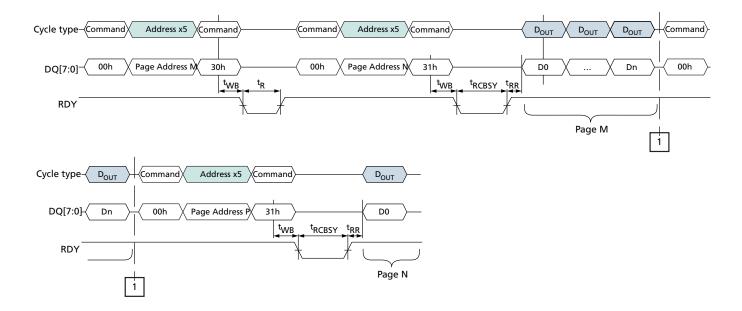

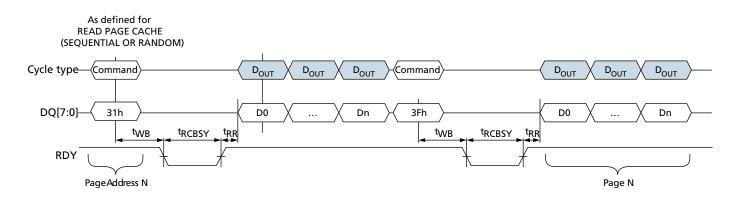

|            | READ PAGE CACHE SEQUENTIAL (31h) Operation                          |            |

|            | READ PAGE CACHE RANDOM (00h-31h) Operation                          |            |

|            | READ PAGE CACHE LAST (3Fh) Operation                                |            |

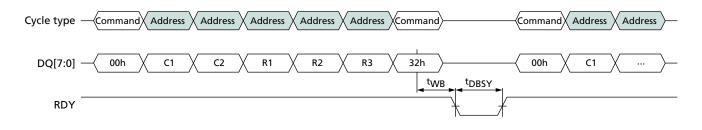

|            | READ PAGE MULTI-PLANE (00h-32h) Operation                           |            |

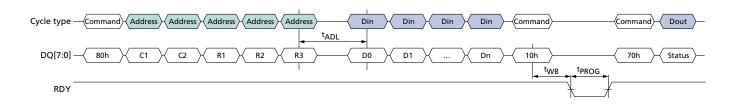

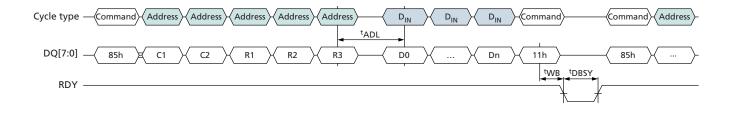

|            | PROGRAM PAGE (80h-10h) Operation                                    |            |

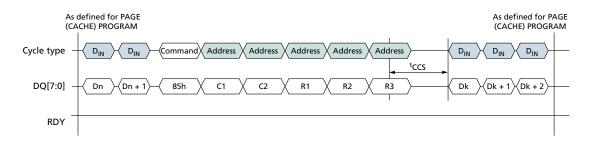

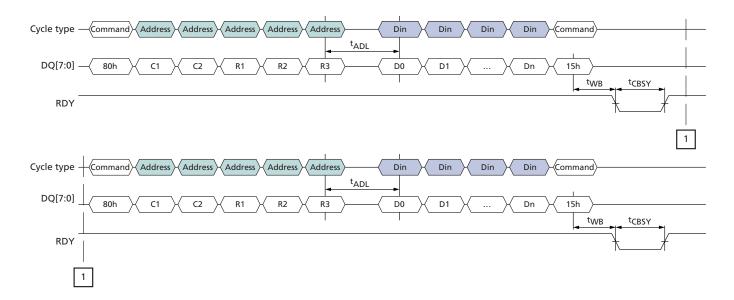

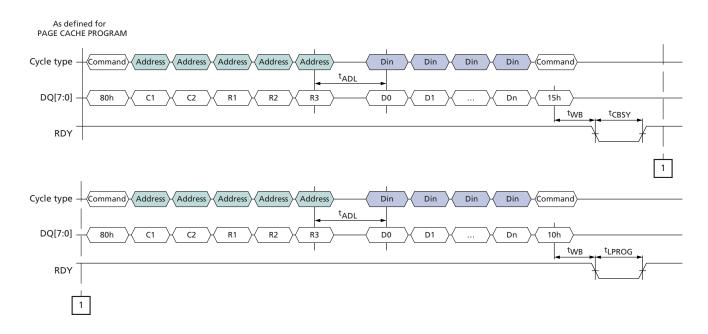

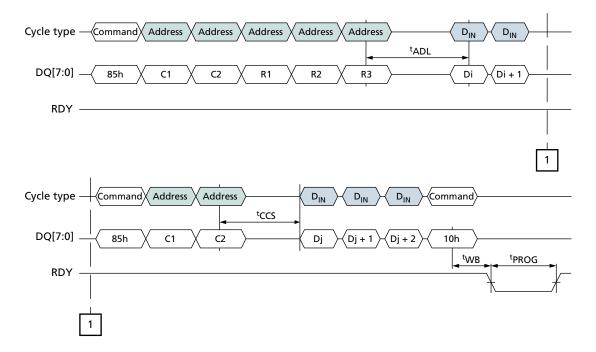

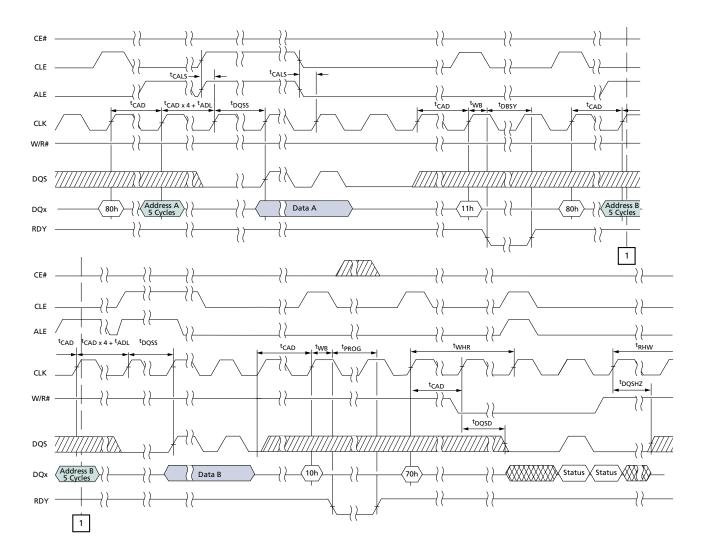

|            | PROGRAM PAGE CACHE (80h–15h) Operation (Start)                      |            |

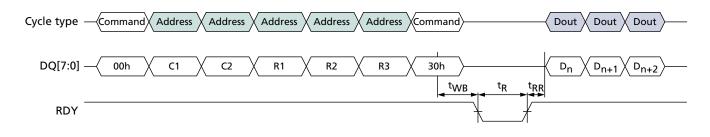

|            | PROGRAM PAGE CACHE (80h–15h) Operation (End)                        |            |

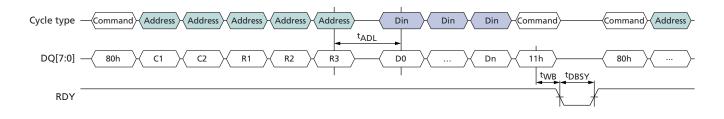

|            | PROGRAM PAGE MULTI-PLANE (80h–11h) Operation                        |            |

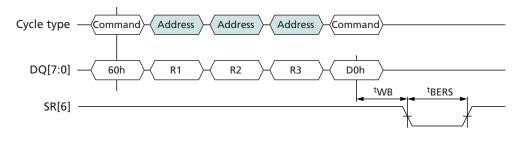

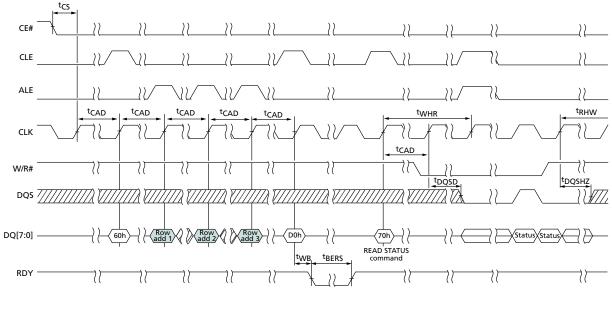

|            | ERASE BLOCK (60h-D0h) Operation                                     |            |

|            | ERASE BLOCK MULTI-PLANE (60h–D1h) Operation                         |            |

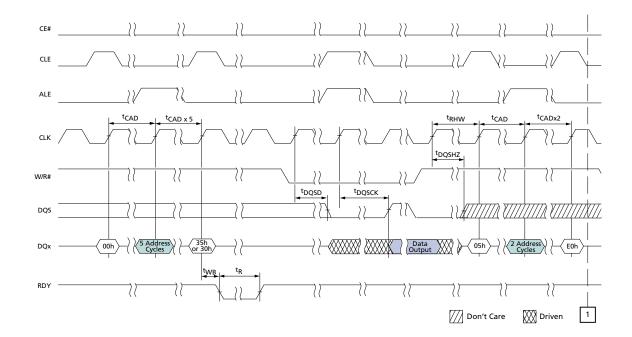

|            | COPYBACK READ (00h-35h) Operation                                   |            |

| Figure 63: | COPYBACK READ (00h–35h) with CHANGE READ COLUMN (05h–E0h) Operation | 99         |

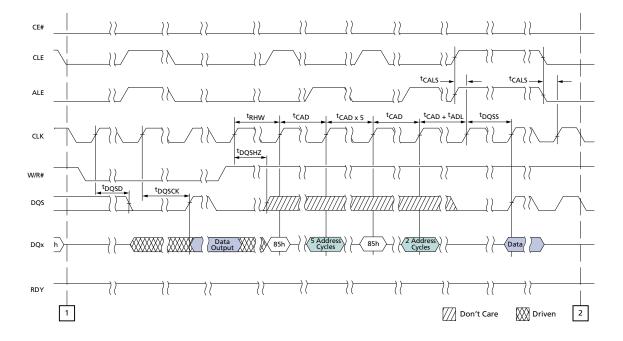

|            | COPYBACK PROGRAM (85h–10h) Operation                                |            |

| Figure 65: | COPYBACK PROGRAM (85h-10h) with CHANGE WRITE COLUMN (85h) Operation | 100        |

|            | COPYBACK PROGRAM MULTI-PLANE (85h-11h) Operation                    |            |

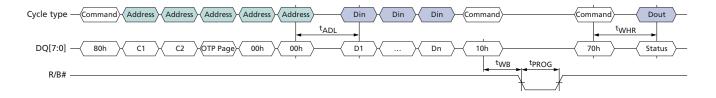

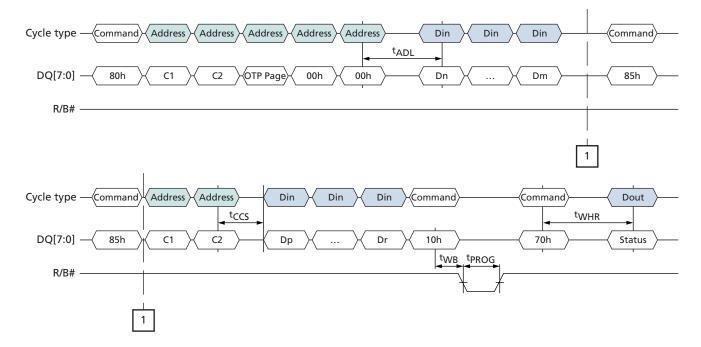

|            | PROGRAM OTP PAGE (80h-10h) Operation                                |            |

|            | PROGRAM OTP PAGE (80h-10h) with CHANGE WRITE COLUMN (85h) Operation |            |

|            | PROTECT OTP AREA (80h-10h) Operation                                |            |

|            | READ OTP PAGE (00h-30h) Operation                                   |            |

|            | Overshoot                                                           |            |

|            | Undershoot                                                          |            |

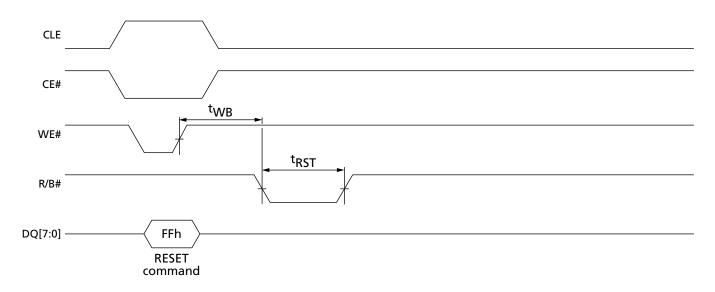

| 0          | RESET Operation                                                     |            |

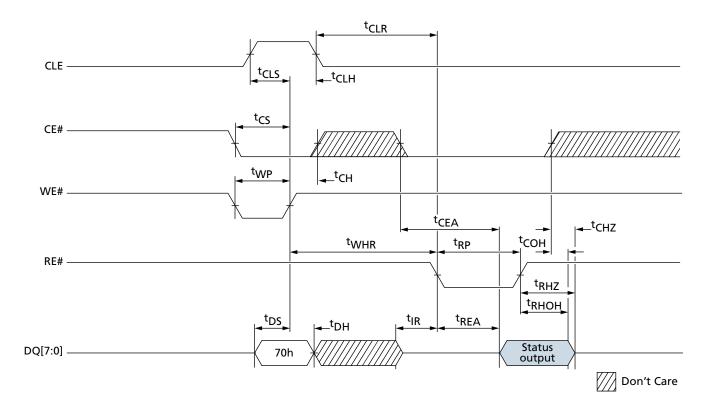

|            | READ STATUS Cycle                                                   |            |

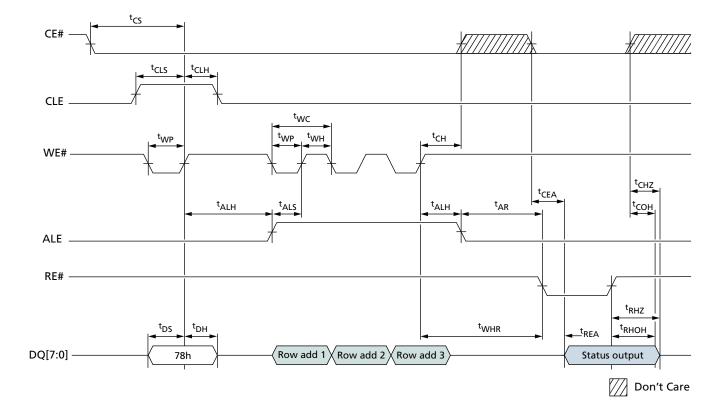

|            | READ STATUS ENHANCED Cycle                                          |            |

|            | READ PARAMETER PAGE                                                 |            |

|            | READ PAGE                                                           |            |

|            | READ PAGE Operation with CE# "Don't Care"                           |            |

|            | CHANGE READ COLUMN                                                  |            |

| Figure 80  | READ PAGE CACHE SEQUENTIAL                                          | 130        |

| Figure 81: | READ PAGE CACHE SEQUENTIAL                                          | 121        |

|            | READ ID Operation                                                   |            |

|            | PROGRAM PAGE Operation                                              |            |

|            | PROGRAM PAGE Operation with CE# "Don't Care"                        |            |

|            | PROGRAM PAGE Operation with CHANGE WRITE COLUMN                     |            |

|            | PROGRAM PAGE CACHE                                                  |            |

|            | PROGRAM PAGE CACHE Ending on 15h                                    |            |

|            | COPYBACK                                                            |            |

|            | ERASE BLOCK Operation                                               |            |

|            |                                                                     |            |

|            | SET FEATURES Operation<br>READ ID Operation                         |            |

| Figure 91: | GET FEATURES Operation                                              | 137<br>120 |

|            | RESET (FCh) Operation                                               |            |

|            |                                                                     |            |

| Figure 94. | READ STATUS Cycle                                                   | 140        |

|            | READ STATUS ENHANCED Operation                                      |            |

|            | READ PARAMETER PAGE Operation                                       |            |

|            | READ PAGE Operation                                                 |            |

| Figure 98: | CHANGE READ COLUMN                                                  | 144        |

|            | READ PAGE CACHE SEQUENTIAL (1 of 2)                                 |            |

|            | : READ PAGE CACHE SEQUENTIAL (2 of 2)                               |            |

|            | : READ PAGE CACHE RANDOM (1 of 2)                                   |            |

| Figure 102 | : READ PAGE CACHE RANDOM (2 of 2)                                   | 147        |

| Figure 103: Multi-Plane Read Page (1 of 2)  |  |

|---------------------------------------------|--|

| Figure 104: Multi-Plane Read Page (2 of 2)  |  |

| Figure 105: PROGRAM PAGE Operation (1 of 2) |  |

| Figure 106: PROGRAM PAGE Operation (2 of 2) |  |

| Figure 107: CHANGE WRITE COLUMN             |  |

| Figure 108: Multi-Plane Program Page        |  |

| Figure 109: ERASE BLOCK                     |  |

| Figure 110: COPYBACK (1 of 3)               |  |

| Figure 111: COPYBACK (2 of 3)               |  |

| Figure 112: COPYBACK (3 of 3)               |  |

| Figure 113: READ OTP PAGE                   |  |

| Figure 114: PROGRAM OTP PAGE (1 of 2)       |  |

| Figure 115: PROGRAM OTP PAGE (2 of 2)       |  |

| Figure 116: PROTECT OTP AREA                |  |

| ·                                           |  |

## 32Gb, 64Gb, 128Gb, 256Gb Asynchronous/Synchronous NAND General Description

## **General Description**

Micron NAND Flash devices include an asynchronous data interface for high-performance I/O operations. These devices use a highly multiplexed 8-bit bus (DQx) to transfer commands,address, and data. There are five control signals used to implement the asynchronous data interface: CE#, CLE, ALE, WE#, and RE#. Additional signals control hardware write protection (WP#) and monitor device status (R/B#).

This Micron NAND Flash device additionally includes a synchronous data interface for high-performance I/O operations. When the synchronous interface is active, WE# becomes CLK and RE# becomes W/R#. Data transfers include a bidirectional data strobe (DQS).

This hardware interface creates a low pin-count device with a standard pinout that remains the same from one density to another, enabling future upgrades to higher densities with no board redesign.

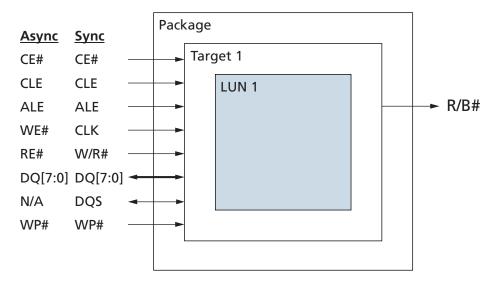

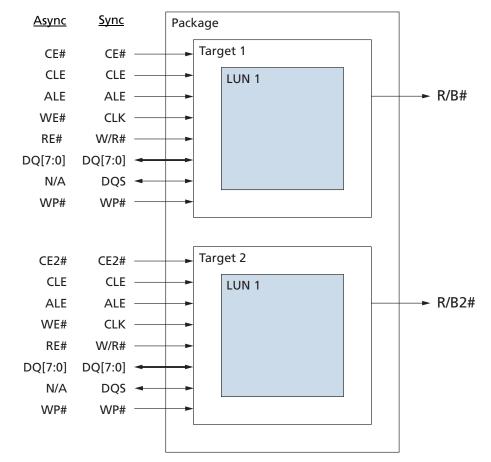

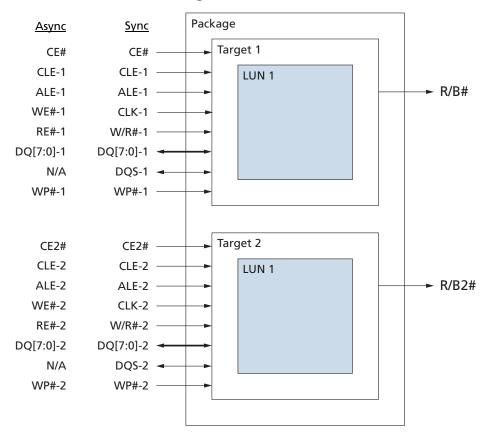

A target is the unit of memory accessed by a chip enable signal. A target contains one or more NAND Flash die. A NAND Flash die is the minimum unit that can independently execute commands and report status. A NAND Flash die, in the ONFI specification, is referred to as a logical unit (LUN). For further details, see Device and Array Organization.

## **Asynchronous and Synchronous Signal Descriptions**

| Asynchronous<br>Signal <sup>1</sup> | Synchronous<br>Signal <sup>1</sup> | Туре   | Description <sup>2</sup>                                                                                                                                                                                                                                  |

|-------------------------------------|------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ALE                                 | ALE                                | Input  | Address latch enable: Loads an address from DQx into the address register.                                                                                                                                                                                |

| CE#                                 | CE#                                | Input  | Chip enable: Enables or disables one or more die (LUNs) in a target <sup>1</sup> .                                                                                                                                                                        |

| CLE                                 | CLE                                | Input  | <b>Command latch enable:</b> Loads a command from DQx into the command register.                                                                                                                                                                          |

| DQx                                 | DQx                                | I/O    | <b>Data inputs/outputs:</b> The bidirectional I/Os transfer address, data, and command information.                                                                                                                                                       |

| -                                   | DQS                                | I/O    | <b>Data strobe:</b> Provides a synchronous reference for data input and output.                                                                                                                                                                           |

| RE#                                 | W/R#                               | Input  | <b>Read enable and write/read:</b> RE# transfers serial data from the NAND Flash to the host system when the asynchronous interface is active. When the synchronous interface is active, W/R# controls the direction of DQx and DQS.                      |

| WE#                                 | CLK                                | Input  | Write enable and clock: WE# transfers commands, addresses, and seri-<br>al data from the host system to the NAND Flash when the asynchronous<br>interface is active. When the synchronous interface is active, CLK latches<br>command and address cycles. |

| WP#                                 | WP#                                | Input  | Write protect: Enables or disables array PROGRAM and ERASE opera-<br>tions.                                                                                                                                                                               |

| R/B#                                | R/B#                               | Output | <b>Ready/busy:</b> An open-drain, active-low output that requires an exter-<br>nal pull-up resistor. This signal indicates target array activity.                                                                                                         |

| V <sub>CC</sub>                     | V <sub>CC</sub>                    | Supply | V <sub>CC</sub> : Core power supply                                                                                                                                                                                                                       |

Table 1: Asynchronous and Synchronous Signal Definitions

## 32Gb, 64Gb, 128Gb, 256Gb Asynchronous/Synchronous NAND Asynchronous and Synchronous Signal Descriptions

#### Table 1: Asynchronous and Synchronous Signal Definitions (Continued)

| Asynchronous<br>Signal <sup>1</sup> | Synchronous<br>Signal <sup>1</sup> | Туре   | Description <sup>2</sup>                                                                     |

|-------------------------------------|------------------------------------|--------|----------------------------------------------------------------------------------------------|

| V <sub>CCQ</sub>                    | V <sub>CCQ</sub>                   | Supply | V <sub>ccq</sub> : I/O power supply                                                          |

| V <sub>SS</sub>                     | V <sub>SS</sub>                    | Supply | <b>V<sub>ss</sub>:</b> Core ground connection                                                |

| V <sub>SSQ</sub>                    | V <sub>SSQ</sub>                   | Supply | <b>V<sub>ssq</sub>:</b> I/O ground connection                                                |

| NC                                  | NC                                 | -      | <b>No connect:</b> NCs are not internally connected. They can be driven or left unconnected. |

| DNU                                 | DNU                                | _      | Do not use: DNUs must be left unconnected.                                                   |

| RFU                                 | RFU                                | _      | Reserved for future use: RFUs must be left unconnected.                                      |

Notes: 1. See Device and Array Organization for detailed signal connections.

2. See Bus Operation – Asynchronous Interface (page 27) and Bus Operation – Synchronous Interface (page 37) for detailed asynchronous and synchronous interface signal descriptions.

## 32Gb, 64Gb, 128Gb, 256Gb Asynchronous/Synchronous NAND Signal Assignments

## **Signal Assignments**

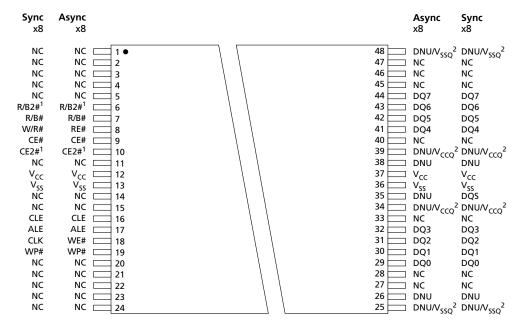

#### Figure 2: 48-Pin TSOP Type 1 (Top View)

- Notes: 1. CE2# and R/B2# are available on dual die and quad die packages. They are NC for other configurations.

- 2. These  $V_{CCQ}$  and  $V_{SSQ}$  pins are for compatibility with ONFI 2.1. If not supplying  $V_{CCQ}$  or  $V_{SSQ}$  to these pins, do not use them.

## 32Gb, 64Gb, 128Gb, 256Gb Asynchronous/Synchronous NAND Signal Assignments

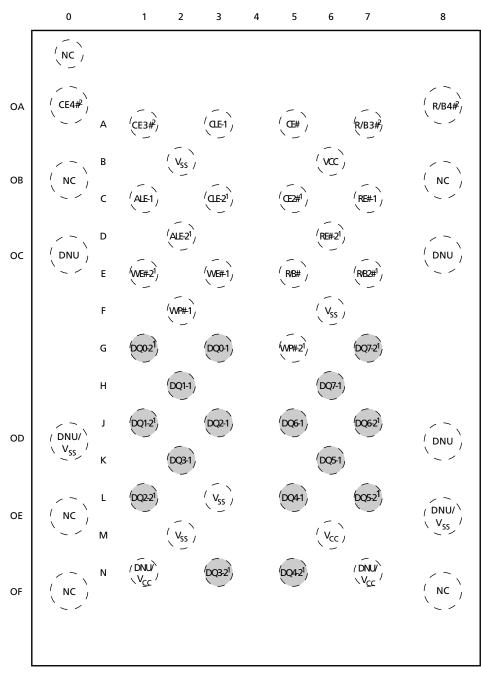

#### Figure 3: 52-Pad LGA (Top View)

Top View, Pads Down

- Notes: 1. These signals are available on dual, quad, and octal die packages. They are NC for other configurations.

- 2. These signals are available on quad die four CE# or octal die packages. They are NC for other configurations.

## 32Gb, 64Gb, 128Gb, 256Gb Asynchronous/Synchronous NAND **Signal Assignments**

#### Figure 4: 100-Ball BGA (Ball-Down, Top View)

| 1    | 2                     | 3                     | 4       | 5                              | 6                               | 7                             | 8                     | 9               | 10            |

|------|-----------------------|-----------------------|---------|--------------------------------|---------------------------------|-------------------------------|-----------------------|-----------------|---------------|

| ( NC | ) ( NC )              |                       |         |                                |                                 |                               |                       | ()              | ( NC )        |

| ( NC | N<br>J                |                       |         |                                |                                 |                               |                       |                 | ( NC )        |

|      | ( <b>RFU</b> )        | ( DNU )               | ( NC )  | (WP#- <b>2</b> )               | ( NC )                          | { NC }                        | ( <b>DNU</b> )        | ( <b>R</b> FU ) |               |

|      | ( RFU )               | ( DNU )               | ( NC )  | (WP#-1)                        | ( NC )                          | ( NC )                        | ( DNU )               | ( RFU )         |               |

|      | ( Vcc )               | ( Vcc )               | ( Vcc ) | ( Vcc )                        | ( Vcc )                         | ( Vcc )                       | ( Vcc )               | ( Vcc )         |               |

|      | ( Vss )               | ( Vss )               | ( Vss ) | ( Vss )                        | ( Vss )                         | ( Vss )                       | ( Vss )               | ( Vss )         |               |

|      | ( <b>Vssq</b> )       | ( Vccq )              | ( RFU ) | ( RFU )                        | ( <b>R/B2</b> # <sup>3</sup> ), | ( <b>R/B4#</b> <sup>4</sup> ) | ( Vccq )              | ( Vssq )        |               |

|      | (DQ0-2 <sup>2</sup> ) | (DQ2-2 <sup>2</sup> ) | (ALE-2) | ( <b>CE4#</b> <sup>4</sup> )   | ( <b>R/B#</b> )                 | ( <b>R/B3#</b> 4)             | (DQ5-2 <sup>2</sup> ) | (DQ7-2)         |               |

|      | (DQ0-1)               | (DQ2-1)               | (ALE-1) | (CE3# <sup>4</sup> )           | (CE2# <sup>₿</sup> )            | ( CE# )                       | (DQ5-1)               | (DQ7-1)         |               |

|      | (Vccq)                | (Vssq)                | (Vccq)  | (CLE-2 <sup>3</sup> )          | (W/R#-2)<br>(W/R#-2)            | (Vccq)                        | (Vssq)                | (Vccq)          |               |

|      | (DQ1-2)               | (DQ3-2 <sup>2</sup> ) | (Vssq)  | (CLE-1)                        | (W/R#-1)<br>(W/R#-1)            | (Vssq)                        | (DQ4-2)               | (DQ6-2)         |               |

|      | (DQ1-1)               | (DQ3-1)               |         | (DQS-2 <sup>3</sup> )          | (RFU)                           | WE#-2                         | (DQ4-1)               | (DQ6-1)         |               |

|      | (Vssq)                | (Vccq)                | (RFU)   | (N/A <sup>1</sup> )<br>(DQS-1) | (RFU)                           | (WE#-1)<br>(CLK-1)            | (Vccq)                | (Vssq)          |               |

| /-~  | ١                     |                       |         |                                |                                 |                               |                       |                 | / - ``        |

| ( NC |                       |                       |         |                                |                                 |                               |                       | /~``            | ( NC )        |

| ( NC | ) ( <mark>NC</mark> ) |                       |         |                                |                                 |                               |                       | ( NC )          | ( <b>NC</b> ) |

- Notes: 1. N/A: This signal is tri-stated when the asynchronous interface is active.

- 2. Signal names in parentheses are the signal names when the synchronous interface is active.

- 3. These signals are available on dual, quad, and octal die packages. They are NC for other configurations.

- 4. These signals are available on quad die four CE# or octal die packages. They are NC for other configurations.

## **Package Dimensions**

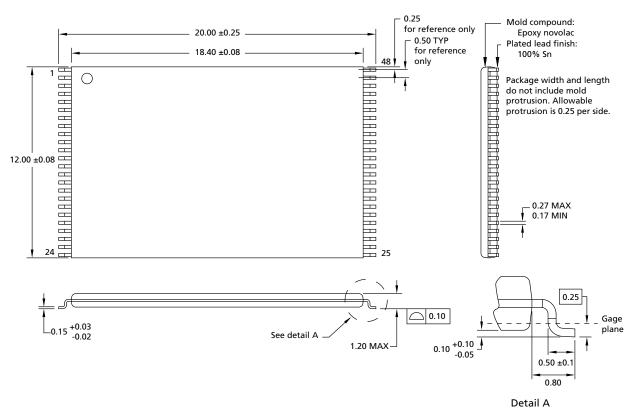

Figure 5: 48-Pin TSOP – Type 1 CPL (Package Code: WP)

Note: 1. All dimensions are in millimeters.

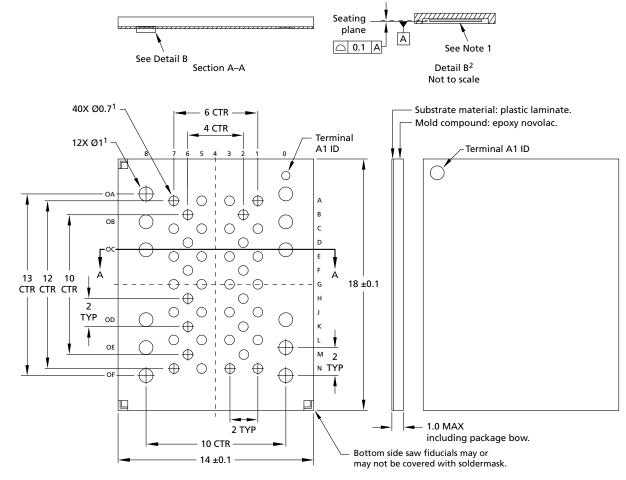

#### Figure 6: 52-Pad VLGA

Notes: 1. Pads are nonsolder mask defined (NSMD) and are plated with 3–15 microns of nickel followed by a minimum of 0.1 microns of soft wire bondable gold (99.99% pure).

2. Primary datum A (seating plane) is defined by the bottom terminal surface. Terminals need not extend below the package bottom surface.

Note: 1. All dimensions are in millimeters.

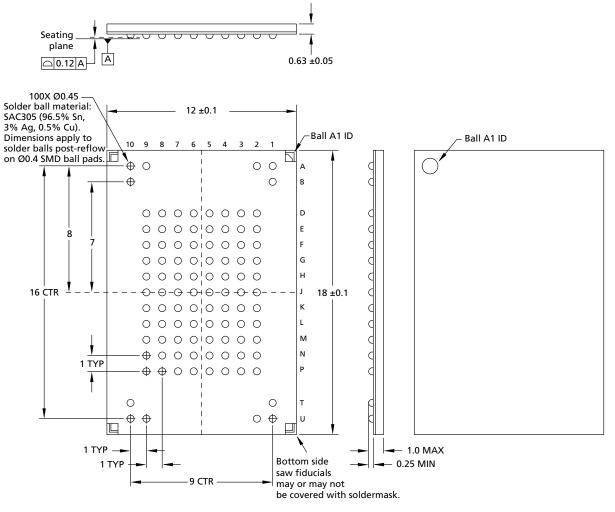

#### Figure 7: 100-Ball VBGA - 12mm x 18mm (Package Code: H1)

Note: 1. All dimensions are in millimeters.

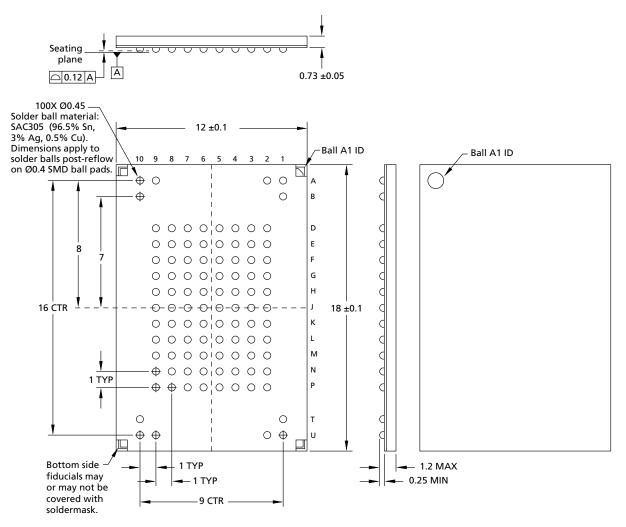

#### Figure 8: 100-Ball TBGA – 12mm x 18mm (Package Code: H2)

Note: 1. All dimensions are in millimeters.

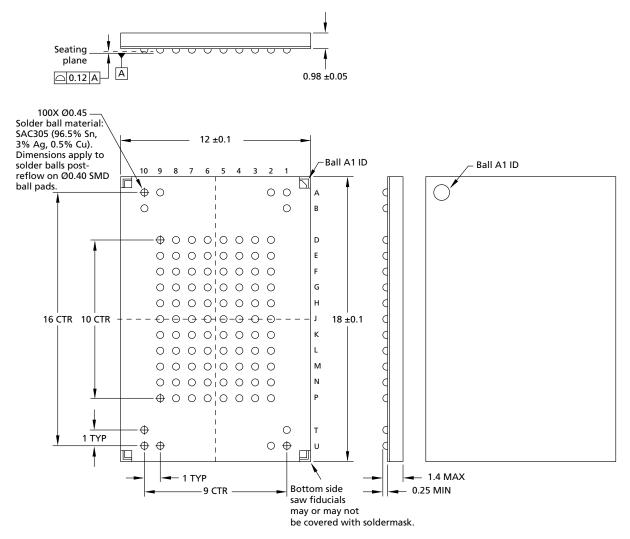

#### Figure 9: 100-Ball LBGA – 12mm x 18mm (Package Code: H3)

Note: 1. All dimensions are in millimeters.

## **CON°** 32Gb, 64Gb, 128Gb, 256Gb Asynchronous/Synchronous NAND Architecture

## Architecture

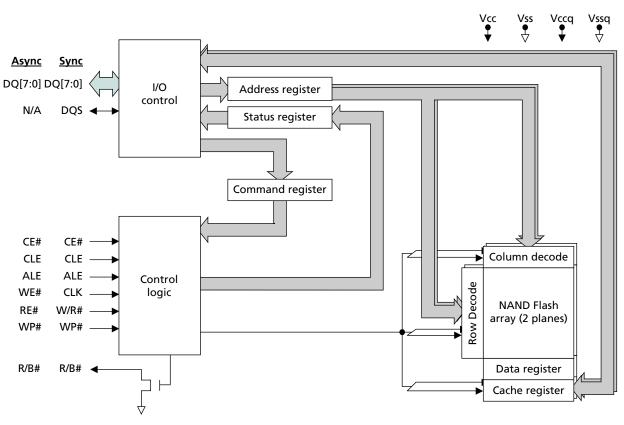

These devices use NAND Flash electrical and command interfaces. Data, commands, and addresses are multiplexed onto the same pins and received by I/O control circuits. The commands received at the I/O control circuits are latched by a command register and are transferred to control logic circuits for generating internal signals to control device operations. The addresses are latched by an address register and sent to a row decoder to select a row address, or to a column decoder to select a column address.

Data is transferred to or from the NAND Flash memory array, byte by byte, through a data register and a cache register.

The NAND Flash memory array is programmed and read using page-based operations and is erased using block-based operations. During normal page operations, the data and cache registers act as a single register. During cache operations, the data and cache registers operate independently to increase data throughput.

The status register reports the status of die (LUN) operations.

#### Figure 10: NAND Flash Die (LUN) Functional Block Diagram

Notes: 1. N/A: This signal is tri-stated when the asynchronous interface is active.2. Some devices do not include the synchronous interface.

## **Device and Array Organization**

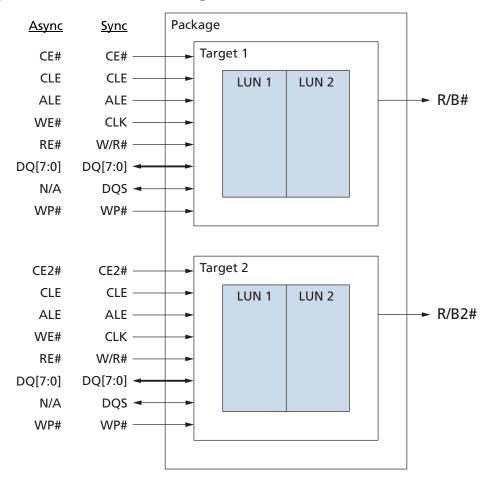

#### Figure 11: Device Organization for Single-Die Package (TSOP/BGA)

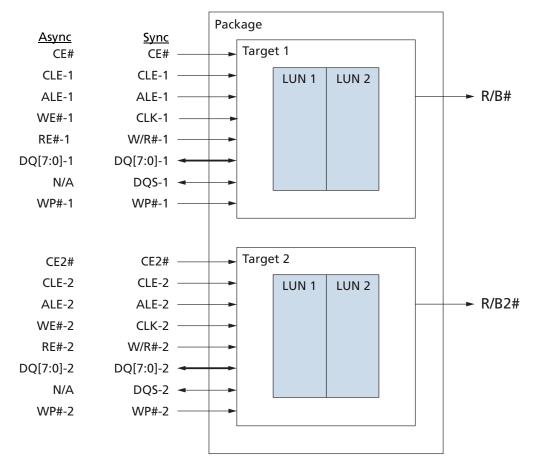

#### Figure 12: Device Organization for Two-Die Package (TSOP)

#### Figure 13: Device Organization for Two-Die Package (BGA/LGA)

Note: 1. LGA devices do not support the synchronous interface.

PDF: 09005aef836c9ded Rev. F 12/09 EN

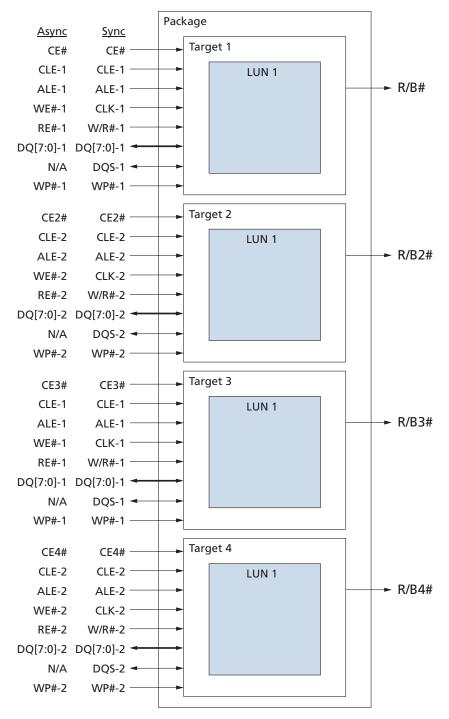

#### Figure 14: Device Organization for Four-Die Package (TSOP)

#### Figure 15: Device Organization for Four-Die Package with CE# and CE2# (BGA/LGA)

Note: 1. LGA devices do not support the synchronous interface.

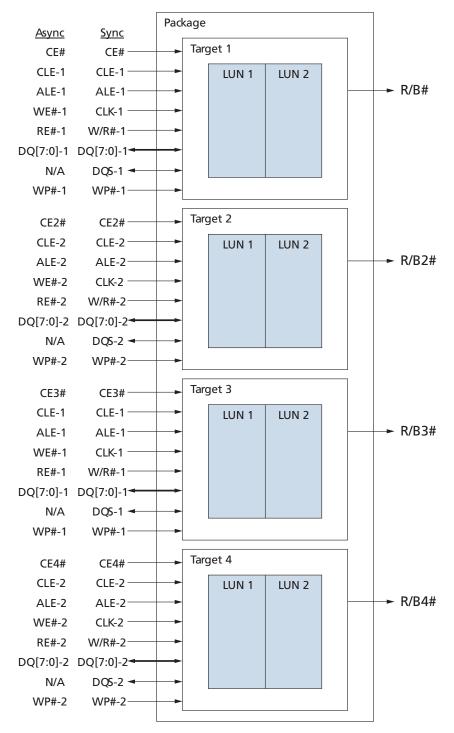

#### Figure 16: Device Organization for Four-Die Package with CE#, CE2#, CE3#, and CE4# (BGA/LGA)

Note: 1. LGA devices do not support the synchronous interface.

#### Figure 17: Device Organization for Eight-Die Package (BGA/LGA)

Note: 1. LGA devices do not support the synchronous interface.

#### Figure 18: Array Organization per Logical Unit (LUN)

#### Table 2: Array Addressing for Logical Unit (LUN)

| Cycle  | DQ7  | DQ6  | DQ5  | DQ4               | DQ3  | DQ2  | DQ1  | DQ0              |

|--------|------|------|------|-------------------|------|------|------|------------------|

| First  | CA7  | CA6  | CA5  | CA4               | CA3  | CA2  | CA1  | CA0 <sup>2</sup> |

| Second | LOW  | LOW  | LOW  | CA12 <sup>3</sup> | CA11 | CA10 | CA9  | CA8              |

| Third  | PA7  | PA6  | PA5  | PA4               | PA3  | PA2  | PA1  | PA0              |

| Fourth | BA15 | BA14 | BA13 | BA12              | BA11 | BA10 | BA9  | BA8 <sup>4</sup> |

| Fifth  | LOW  | LOW  | LOW  | LA0 <sup>5</sup>  | BA19 | BA18 | BA17 | BA16             |

Notes: 1. CAx = column address, PAx = page address, BAx = block address, LAx = LUN address; the page address, block address, and LUN address are collectively called the row address.

2. When using the synchronous interface, CA0 is forced to 0 internally; one data cycle always returns one even byte and one odd byte.

3. Column addresses 4320 (10E0h) through 8191 (1FFFh) are invalid, out of bounds, do not exist in the device, and cannot be addressed.

4. BA[8] is the plane-select bit:

Plane 0: BA[8] = 0

Plane 1: BA[8] = 1

5. LA0 is the LUN-select bit. It is present only when two LUNs are shared on the target; otherwise, it should be held LOW.

LUN 0: LA0 = 0

LUN 1: LA0 = 1

## **Bus Operation – Asynchronous Interface**

The asynchronous interface is active when the NAND Flash device powers on. The I/O bus, DQ[7:0], is multiplexed sharing data I/O, addresses, and commands. The DQS signal, if present, is tri-stated when the asynchronous interface is active.

Asynchronous interface bus modes are summarized below.

| Mode          | CE# | CLE | ALE | WE# | RE# | DQS | DQx    | WP#                              | Notes |

|---------------|-----|-----|-----|-----|-----|-----|--------|----------------------------------|-------|

| Standby       | н   | Х   | X   | X   | Х   | х   | Х      | 0V/V <sub>CCQ</sub> <sup>2</sup> | 2     |

| Bus idle      | L   | Х   | X   | Н   | н   | X   | Х      | Х                                |       |

| Command input | L   | Н   | L   |     | Н   | х   | input  | Н                                |       |

| Address input | L   | L   | н   |     | Н   | х   | input  | н                                |       |

| Data input    | L   | L   | L   |     | Н   | x   | input  | н                                |       |

| Data output   | L   | L   | L   | н   | ₹   | x   | output | Х                                |       |

| Write protect | Х   | Х   | X   | Х   | х   | x   | Х      | L                                |       |

#### Table 3: Asynchronous Interface Mode Selection

Notes: 1. DQS is tri-stated when the asynchronous interface is active.

- 2. WP# should be biased to CMOS LOW or HIGH for standby.

- 3. Mode selection settings for this table: H = Logic level HIGH; L = Logic level LOW; X =  $V_{IH}$  or  $V_{IL}$ .

## **Asynchronous Enable/Standby**

A chip enable (CE#) signal is used to enable or disable a target. When CE# is driven LOW, all of the signals for that target are enabled. With CE# LOW, the target can accept commands, addresses, and data I/O. There may be more than one target in a NAND Flash package. Each target is controlled by its own chip enable; the first target (Target 0) is controlled by CE#; the second target (if present) is controlled by CE2#, etc.

A target is disabled when CE# is driven HIGH, even when the target is busy. When disabled, all of the target's signals are disabled except CE#, WP#, and R/B#. This functionality is also known as CE# "Don't Care". While the target is disabled, other devices can utilize the disabled NAND signals that are shared with the NAND Flash.

A target enters low-power standby when it is disabled and is not busy. If the target is busy when it is disabled, the target enters standby after all of the die (LUNs) complete their operations. Standby helps reduce power consumption.

#### **Asynchronous Bus Idle**

A target's bus is idle when CE# is LOW, WE# is HIGH, and RE# is HIGH.

During bus idle, all of the signals are enabled except DQS, which is not used when the asynchronous interface is active. No commands, addresses, and data are latched into the target; no data is output.

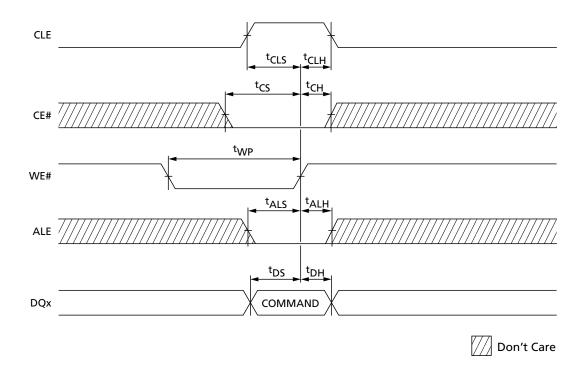

#### **Asynchronous Commands**

An asynchronous command is written from DQ[7:0] to the command register on the rising edge of WE# when CE# is LOW, ALE is LOW, CLE is HIGH, and RE# is HIGH.

Commands are typically ignored by die (LUNs) that are busy (RDY = 0); however, some commands, including READ STATUS (70h) and READ STATUS ENHANCED (78h), are accepted by die (LUNs) even when they are busy.

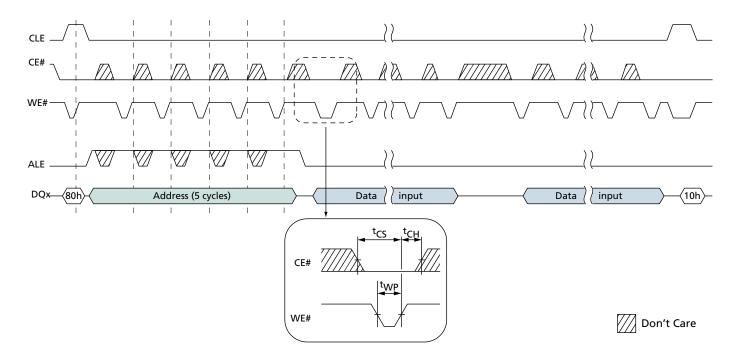

#### Figure 19: Asynchronous Command Latch Cycle

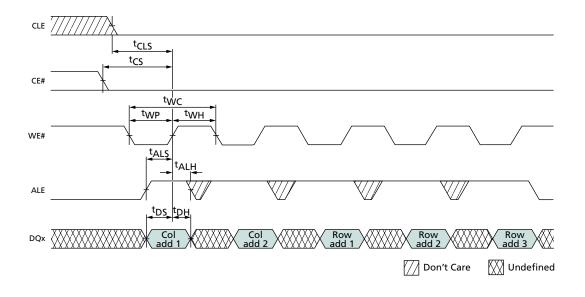

### **Asynchronous Addresses**

An asynchronous address is written from DQ[7:0] to the address register on the rising edge of WE# when CE# is LOW, ALE is HIGH, CLE is LOW, and RE# is HIGH.

Bits that are not part of the address space must be LOW (see Device and Array Organization). The number of cycles required for each command varies. Refer to the command descriptions to determine addressing requirements (see Command Definitions).

Addresses are typically ignored by die (LUNs) that are busy (RDY = 0); however, some addresses are accepted by die (LUNs) even when they are busy; for example, address cycles that follow the READ STATUS ENHANCED (78h) command.

#### Figure 20: Asynchronous Address Latch Cycle

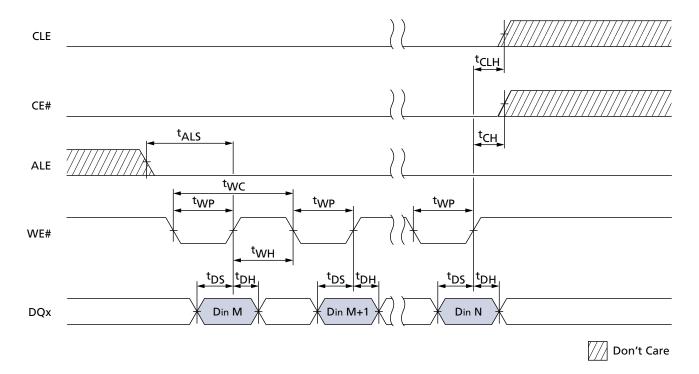

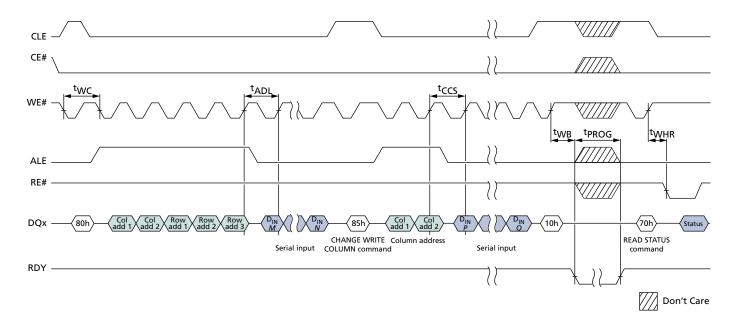

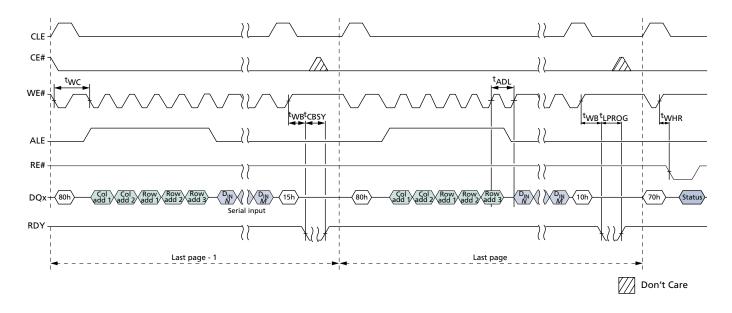

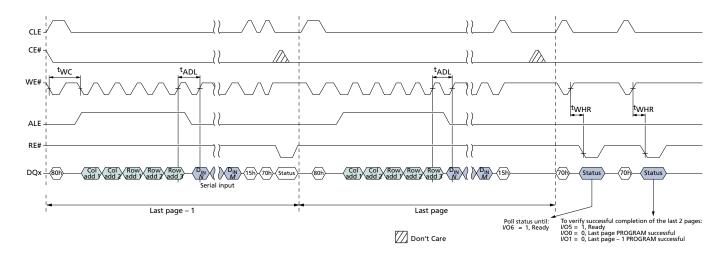

#### **Asynchronous Data Input**

Data is written from DQ[7:0] to the cache register of the selected die (LUN) on the rising edge of WE# when CE# is LOW, ALE is LOW, CLE is LOW, and RE# is HIGH.

Data input is ignored by die (LUNs) that are not selected or are busy (RDY = 0).

#### **Asynchronous Data Output**

Data can be output from a die (LUN) if it is in a READY state. Data output is supported following a READ operation from the NAND Flash array. Data is output from the cache register of the selected die (LUN) to DQ[7:0] on the falling edge of RE# when CE# is LOW, ALE is LOW, CLE is LOW, and WE# is HIGH.

If the host controller is using a <sup>t</sup>RC of 30ns or greater, the host can latch the data on the rising edge of RE# (see Figure 22 for proper timing). If the host controller is using a <sup>t</sup>RC of less than 30ns, the host can latch the data on the next falling edge of RE# (see Figure 23 (page 32) for extended data output (EDO) timing).

Using the READ STATUS ENHANCED (78h) command prevents data contention following an interleaved die (multi-LUN) operation. After issuing the READ STATUS EN-HANCED (78h) command, to enable data output, issue the READ MODE (00h) command.

Data output requests are typically ignored by a die (LUN) that is busy (RDY = 0); however, it is possible to output data from the status register even when a die (LUN) is busy by first issuing the READ STATUS (70h) or READ STATUS ENHANCED (78h) command.

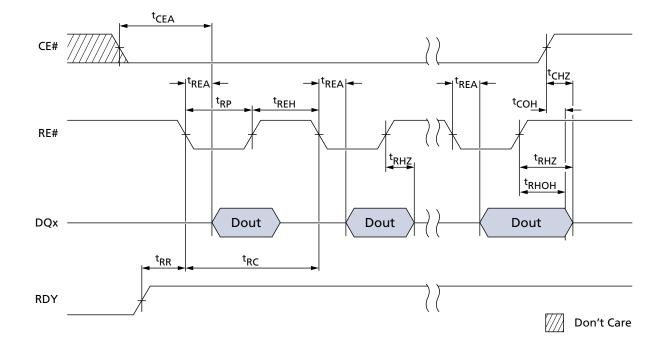

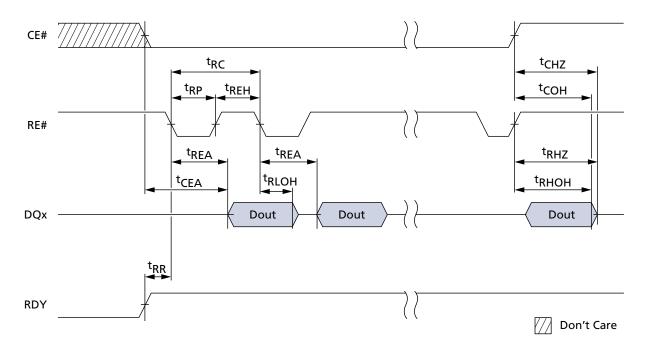

#### Figure 22: Asynchronous Data Output Cycles

#### Figure 23: Asynchronous Data Output Cycles (EDO Mode)

#### Write Protect

The write protect# (WP#) signal enables or disables PROGRAM and ERASE operations to a target. When WP# is LOW, PROGRAM and ERASE operations are disabled. When WP# is HIGH, PROGRAM and ERASE operations are enabled.

It is recommended that the host drive WP# LOW during power-on until Vcc and Vccq are stable to prevent inadvertent PROGRAM and ERASE operations (see Device Initialization (page 45) for additional details).

WP# must be transitioned only when the target is not busy and prior to beginning a command sequence. After a command sequence is complete and the target is ready, WP# can be transitioned. After WP# is transitioned, the host must wait <sup>t</sup>WW before issuing a new command.

The WP# signal is always an active input, even when CE# is HIGH. This signal should not be multiplexed with other signals.

#### Ready/Busy#

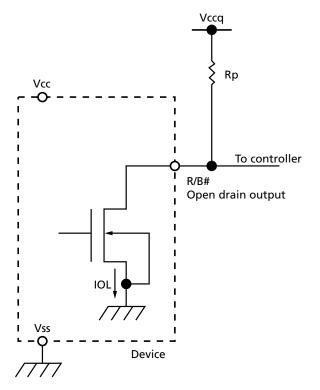

The ready/busy# (R/B#) signal provides a hardware method of indicating whether a target is ready or busy. A target is busy when one or more of its die (LUNs) are busy (RDY = 0). A target is ready when all of its die (LUNs) are ready (RDY = 1). Because each die (LUN) contains a status register, it is possible to determine the independent status of each die (LUN) by polling its status register instead of using the R/B# signal (see Status Operations (page 72) for details regarding die (LUN) status).

This signal requires a pull-up resistor, Rp, for proper operation. R/B# is HIGH when the target is ready, and transitions LOW when the target is busy. The signal's open-drain

driver enables multiple R/B# outputs to be OR-tied. Typically, R/B# is connected to an interrupt pin on the system controller (see Figure 24 (page 33)).

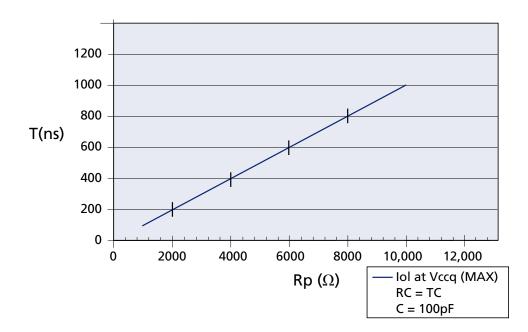

The combination of Rp and capacitive loading of the R/B# circuit determines the rise time of the R/B# signal. The actual value used for Rp depends on the system timing requirements. Large values of Rp cause R/B# to be delayed significantly. Between the 10-to 90-percent points on the R/B# waveform, the rise time is approximately two time constants (TC).

$$TC = R \times C$$

Where R = Rp (resistance of pull-up resistor), and C = total capacitive load.

The fall time of the R/B# signal is determined mainly by the output impedance of the R/B# signal and the total load capacitance. Approximate Rp values using a circuit load of 100pF are provided in Figure 29 (page 36).

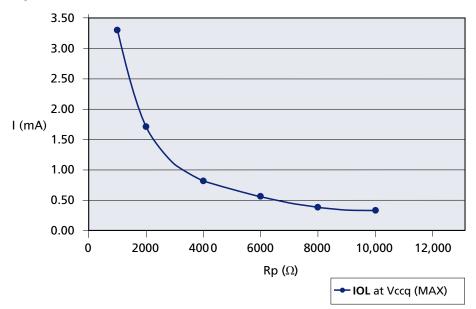

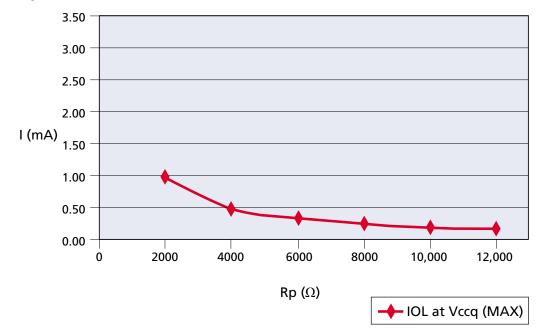

The minimum value for Rp is determined by the output drive capability of the R/B# signal, the output voltage swing, and Vccq.

$$Rp = \frac{Vcc (MAX) - Vol (MAX)}{IOL + \Sigma i I}$$

Where  $\Sigma$  is the sum of the input currents of all devices tied to the R/B# pin.

#### Figure 24: READ/BUSY# Open Drain

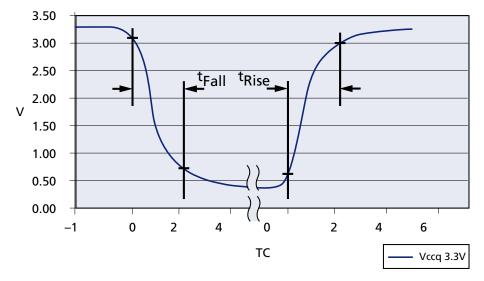

#### Figure 25: <sup>t</sup>Fall and <sup>t</sup>Rise (V<sub>CCQ</sub> = 2.7-3.6V)

- Notes: 1. <sup>t</sup>FALL is  $V_{OH(DC)}$  to  $V_{OL(AC)}$  and <sup>t</sup>RISE is  $V_{OL(DC)}$  to  $V_{OH(AC)}$ .

- 2. <sup>t</sup>Rise dependent on external capacitance and resistive loading and output transistor impedance.

- 3. <sup>t</sup>Rise primarily dependent on external pull-up resistor and external capacitive loading.

- 4. <sup>t</sup>Fall = 10ns at 3.3V

- 5. See TC values in Figure 29 (page 36) for approximate Rp value and TC.

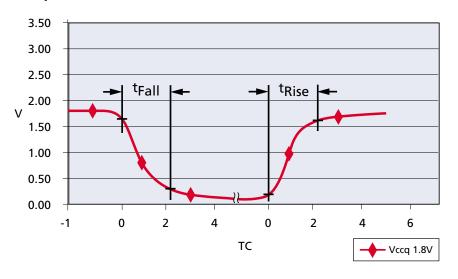

#### Figure 26: <sup>t</sup>Fall and <sup>t</sup>Rise (V<sub>CCQ</sub> = 1.7-1.95V)

Notes: 1. <sup>t</sup>FALL is V<sub>OH(DC)</sub> to V<sub>OL(AC)</sub> and <sup>t</sup>RISE is V<sub>OL(DC)</sub> to V<sub>OH(AC)</sub>.

- 2. <sup>t</sup>Rise is primarily dependent on external pull-up resistor and external capacitive loading.

- 3. <sup>t</sup>Fall  $\approx$  7ns at 1.8V.

- 4. See TC values in Figure 29 (page 36) for TC and approximate Rp value.

#### Figure 27: IOL vs Rp (V<sub>CCQ</sub> = 2.7-3.6V)

Figure 28: IOL vs Rp (V<sub>CCQ</sub> = 1.7-1.95V)

Figure 29: TC vs Rp

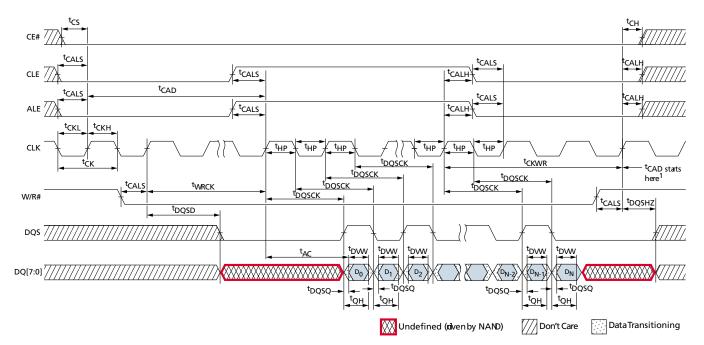

# **Bus Operation – Synchronous Interface**

These NAND Flash devices have two interfaces—a synchronous interface for fast data I/O transfer and an asynchronous interface that is backward compatible with existing NAND Flash devices.

The NAND Flash command protocol for both the asynchronous and synchronous interfaces is identical. However, there are some differences betweeen the asynchronous and synchronous interfaces when issuing command, address, and data I/O cycles using the NAND Flash signals.

When the synchronous interface is activated on a target (see Activating Interfaces (page 46)), the target is capable of high-speed DDR data transfers. Existing signals are redefined for high-speed DDR I/O. The WE# signal becomes CLK. DQS is enabled. The RE# signal becomes W/R#. CLK provides a clock reference to the NAND Flash device.

DQS is a bidirectional data strobe. During data output, DQS is driven by the NAND Flash device. During data input, DQS is controlled by the host controller while input-ting data on DQ[7:0].

The direction of DQS and DQ[7:0] is controlled by the W/R# signal. When the W/R# signal is latched HIGH, the controller is driving the DQ bus and DQS. When the W/R# is latched LOW, the NAND Flash is driving the DQ bus and DQS.

The synchronous interface bus modes are summarized below.

| Mode               | CE# | CLE | ALE | CLK          | W/R# | DQS        | DQ[7:0] | WP#                 | Notes |

|--------------------|-----|-----|-----|--------------|------|------------|---------|---------------------|-------|

| Standby            | Н   | Х   | Х   | Х            | Х    | Х          | Х       | 0V/V <sub>CCQ</sub> | 1, 2  |

| Bus idle           | L   | L   | L   |              | н    | X          | х       | х                   |       |

| Bus driv-<br>ing   | L   | L   | L   | ₹            | L    | output     | output  | Х                   |       |

| Command<br>input   | L   | Н   | L   | ٦Æ           | Н    | X          | input   | Н                   | 3     |

| Address<br>input   | L   | L   | Н   | ٦Æ           | Н    | X          | input   | Н                   | 3     |

| Data input         | L   | н   | Н   | <b>_▲</b> ₹  | н    | <b>₽</b>   | input   | Н                   | 4     |

| Data out-<br>put   | L   | Н   | Н   | _ <b>▲</b> ₹ | L    | See Note 5 | output  | Х                   | 5     |

| Write pro-<br>tect | Х   | X   | X   | Х            | Х    | X          | Х       | L                   |       |

| Undefined          | L   | L   | Н   |              | L    | output     | output  | х                   |       |

| Undefined          | L   | н   | L   |              | L    | output     | output  | х                   |       |

### **Table 4: Synchronous Interface Mode Selection**

Notes: 1. CLK can be stopped when the target is disabled, even when R/B# is LOW.

2. WP# should be biased to CMOS LOW or HIGH for standby.

- 3. Commands and addresses are latched on the rising edge of CLK.

- 4. During data input to the device, DQS is the "clock" that latches the data in the cache register.

- 5. During data output from the NAND Flash device, DQS is an output generated from CLK after <sup>t</sup>DQSCK delay.

- 6. Mode selection settings for this table: H = Logic level HIGH; L = Logic level LOW; X =  $V_{IH}$  or  $V_{IL}$ .

### Synchronous Enable/Standby

In addition to the description in the section Asynchronous Enable/Standby (page 27), the following requirements also apply when the synchronous interface is active.

Before enabling a target, CLK must be running and ALE and CLE must be LOW. When CE# is driven LOW, all of the signals for the selected target are enabled. The target is not enabled until <sup>t</sup>CS completes; the target's bus is then idle.

Prior to disabling a target, the target's bus must be idle. A target is disabled when CE# is driven HIGH, even when it is busy. All of the target's signals are disabled except CE#, WP#, and R/B#. After the target is disabled, CLK can be stopped.

A target enters low-power standby when it is disabled and is not busy. If the target is busy when it is disabled, the target enters standby after all of the die (LUNs) complete their operations.

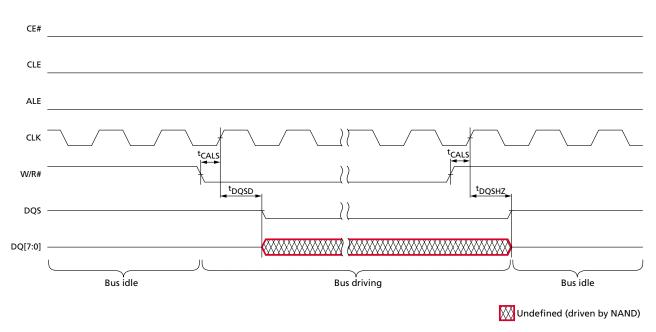

### **Synchronous Bus Idle/Driving**

A target's bus is idle or driving when CLK is running, CE# is LOW, ALE is LOW, and CLE is LOW.

The bus is idle when W/R# transitions HIGH and is latched by CLK. During the bus idle mode, all signals are enabled; DQS and DQ[7:0] are inputs. No commands, addresses, or data are latched into the target; no data is output. When entering the bus idle mode, the host must wait a minimum of <sup>t</sup>CAD before changing the bus mode. In the bus idle mode, the only valid bus modes supported are: bus driving, command, address, and DDR data input.

The bus is driving when W/R# transitions LOW and is latched by CLK. During the bus driving mode, all signals are enabled; DQS is LOW and DQ[7:0] is driven LOW or HIGH, but no valid data is output. Following the bus driving mode, the only valid bus modes supported are bus idle and DDR data output.

### Figure 30: Synchronous Bus Idle/Driving Behavior

Note: 1. Only the selected die (LUN) drives DQS and DQ[7:0]. During an interleaved die (multi-LUN) operation, the host must use the READ STATUS ENHANCED (78h) to prevent data output contention.

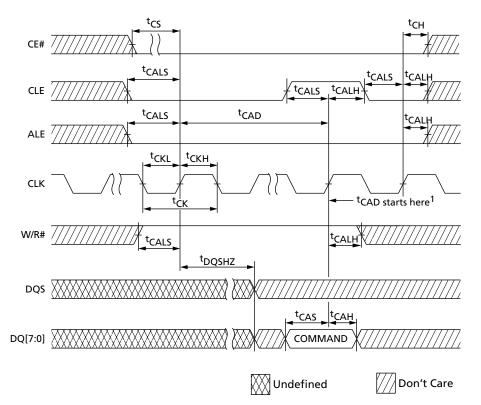

### **Synchronous Commands**

A command is written from DQ[7:0] to the command register on the rising edge of CLK when CE# is LOW, ALE is LOW, CLE is HIGH, and W/R# is HIGH.

After a command is latched—and prior to issuing the next command, address, or data I/O—the bus must go to bus idle mode on the next rising edge of CLK, except when the clock period, <sup>t</sup>CK, is greater than <sup>t</sup>CAD.

Commands are typically ignored by die (LUNs) that are busy (RDY = 0); however, some commands, such as READ STATUS (70h) and READ STATUS ENHANCED (78h), are accepted by die (LUNs), even when they are busy.

### Figure 31: Synchronous Command Cycle

Note: 1. When CE# remains LOW, <sup>t</sup>CAD begins at the rising edge of the clock from which the command cycle is latched for subsequent command, address, data input, or data output cycle(s).

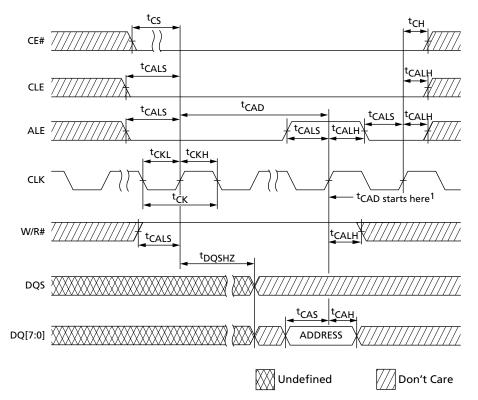

### **Synchronous Addresses**

A synchronous address is written from DQ[7:0] to the address register on the rising edge of CLK when CE# is LOW, ALE is HIGH, CLE is LOW, and W/R# is HIGH.

After an address is latched—and prior to issuing the next command, address, or data I/O —the bus must go to bus idle mode on the next rising edge of CLK, except when the clock period, <sup>t</sup>CK, is greater than <sup>t</sup>CAD.

Bits not part of the address space must be LOW (see Device and Array Organization). The number of address cycles required for each command varies. Refer to the command descriptions to determine addressing requirements.

Addresses are typically ignored by die (LUNs) that are busy (RDY = 0); however, some addresses such as address cycles that follow the READ STATUS ENHANCED (78h) command, are accepted by die (LUNs), even when they are busy.

### Figure 32: Synchronous Address Cycle

Note: 1. When CE# remains LOW, <sup>t</sup>CAD begins at the rising edge of the clock from which the command cycle is latched for subsequent command, address, data input, or data output cycle(s).

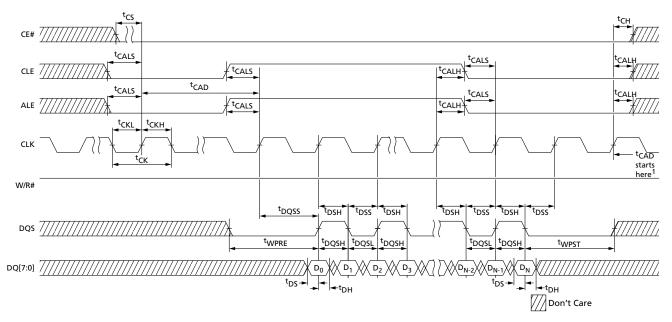

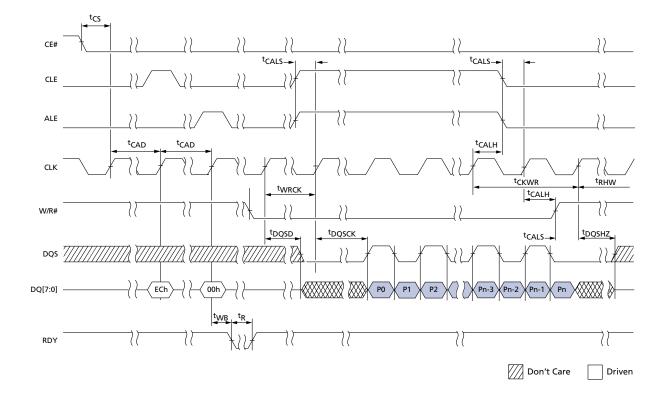

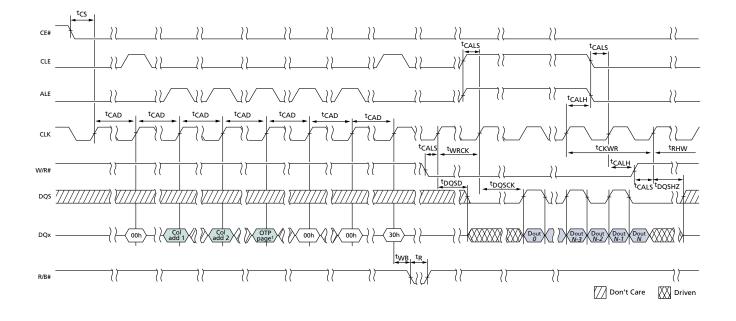

### Synchronous DDR Data Input

To enter the DDR data input mode, the following conditions must be met:

- CLK is running

- CE# is LOW

- W/R# is HIGH

- <sup>t</sup>CAD is met

- DQS is LOW

- ALE and CLE are HIGH on the rising edge of CLK

Upon entering the DDR data input mode after <sup>t</sup>DQSS, data is written from DQ[7:0] to the cache register on each and every rising and falling edge of DQS (center-aligned) when CLK is running and the DQS to CLK skew meets <sup>t</sup>DSH and <sup>t</sup>DSS, CE# is LOW, W/R# is HIGH, and ALE and CLE are HIGH on the rising edge of CLK.

To exit DDR data input mode, the following conditions must be met:

- CLK is running and the DQS to CLK skew meets <sup>t</sup>DSH and <sup>t</sup>DSS

- CE# is LOW

- W/R# is HIGH

- ALE and CLE are latched LOW on the rising edge of CLK

- The final two data bytes of the data input sequence are written to DQ[7:0] to the cache register on the rising and falling edges of DQS after the last cycle in the data input sequence in which ALE and CLE are latched HIGH.

- DQS is held LOW for  ${}^t\!WPST$  (after the final falling edge of DQS)

Following <sup>t</sup>WPST, the bus enters bus idle mode and <sup>t</sup>CAD begins on the next rising edge of CLK. After <sup>t</sup>CAD starts, the host can disable the target if desired.

Data input is ignored by die (LUNs) that are not selected or are busy.

### Figure 33: Synchronous DDR Data Input Cycles

- Notes: 1. When CE# remains LOW, <sup>t</sup>CAD begins at the first rising edge of the clock after <sup>t</sup>WPST completes.

- 2. <sup>t</sup>DSH (MIN) generally occurs during <sup>t</sup>DQSS (MIN).

- 3. <sup>t</sup>DSS (MIN) generally occurs during <sup>t</sup>DQSS (MAX).

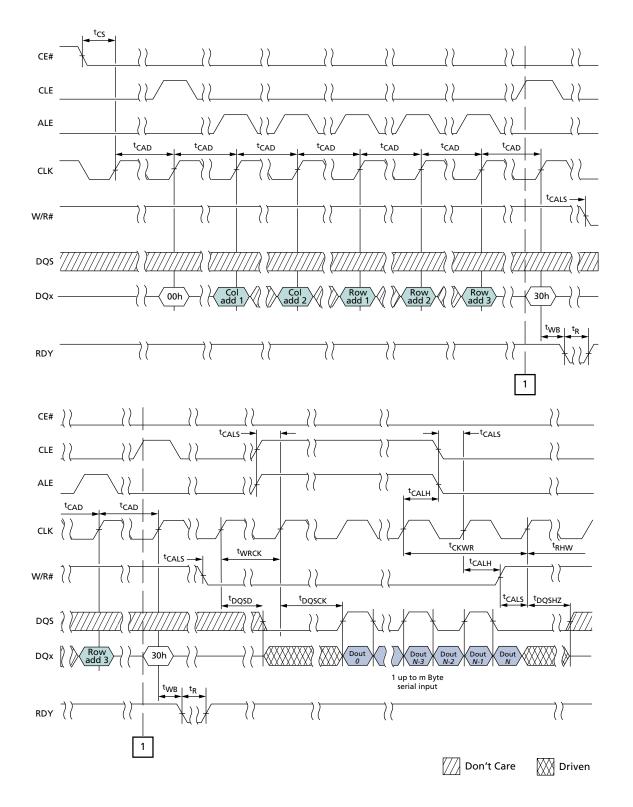

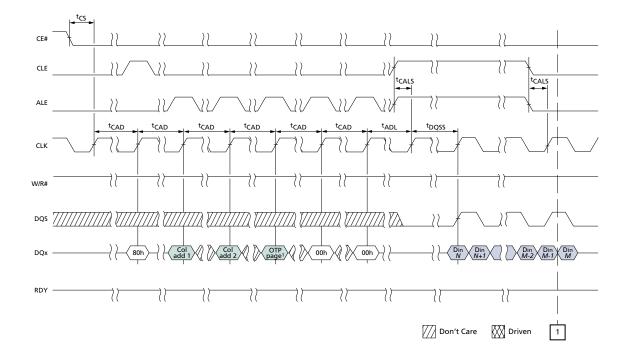

### Synchronous DDR Data Output

Data can be output from a die (LUN) if it is ready. Data output is supported following a READ operation from the NAND Flash array.

To enter the DDR data output mode, the following conditions must be met:

- CLK is running

- CE# is LOW

- The host has released the DQ[7:0] bus and DQS

- W/R# is latched LOW on the rising edge of CLK to enable the selected die (LUN) to take ownership of the DQ[7:0] bus and DQS within <sup>t</sup>WRCK

- <sup>t</sup>CAD is met

- ALE and CLE are HIGH on the rising edge of CLK

Upon entering the DDR data output mode, DQS will toggle HIGH and LOW with a delay of <sup>t</sup>DQSCK from the respective rising and falling edges of CLK. DQ[7:0] will output data edge-aligned to the rising and falling edges of DQS, with the first transition delayed by no more than <sup>t</sup>AC.

DDR data output mode continues as long as CLK is running, CE# is LOW, W/R# is LOW, and ALE and CLE are HIGH on the rising edge of CLK.

To exit DDR data output mode, the following conditions must be met:

- CLK is running

- CE# is LOW

- W/R# is LOW

- ALE and CLE are latched LOW on the rising edge of CLK

The final two data bytes are output on DQ[7:0] on the final rising and falling edges of DQS. The final rising and falling edges of DQS occur <sup>t</sup>DQSCK after the last cycle in the data output sequence in which ALE and CLE are latched HIGH. After <sup>t</sup>CKWR, the bus enters bus idle mode and <sup>t</sup>CAD begins on the next rising edge of CLK. Once <sup>t</sup>CAD starts the host can disable the target if desired.

Data output requests are typically ignored by a die (LUN) that is busy (RDY = 0); however, it is possible to output data from the status register even when a die (LUN) is busy by issuing the READ STATUS (70h) or READ STATUS ENHANCED (78h) command.

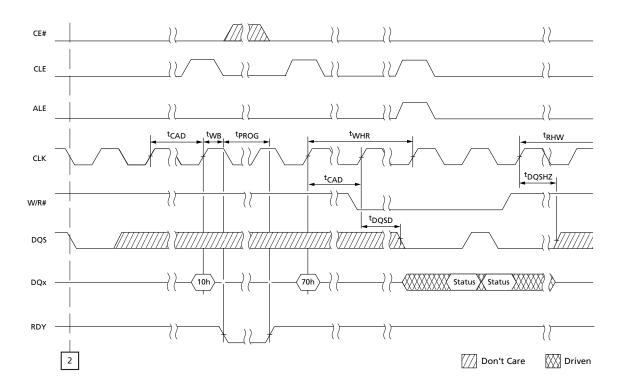

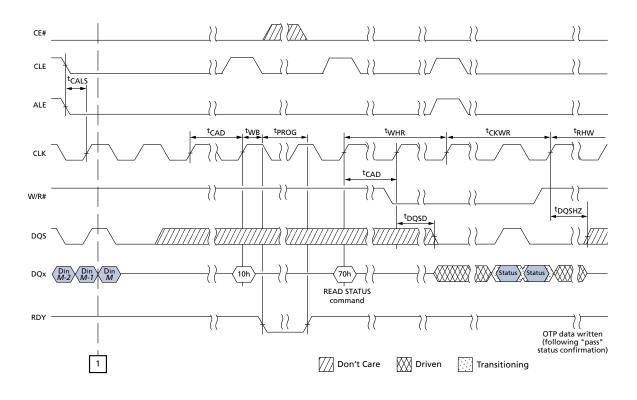

### Figure 34: Synchronous DDR Data Output Cycles

- Notes: 1. When CE# remains LOW, <sup>t</sup>CAD begins at the rising edge of the clock after <sup>t</sup>CKWR for subsequent command or data output cycle(s).

- 2. See Figure 31 (page 40) for details of W/R# behavior.

- 3. <sup>t</sup>AC is the DQ output window relative to CLK and is the long-term component of DQ skew.

- 4. For W/R# transitioning HIGH, DQ[7:0] and DQS go to tri-state.

- 5. For W/R# transitioning LOW, DQ[7:0] drives current state and DQS goes LOW.

- 6. After final data output, DQ[7:0] is driven until W/R# goes HIGH, but is not valid.

## **Write Protect**

See Write Protect (page 32).

### Ready/Busy#

See Ready/Busy# (page 32).

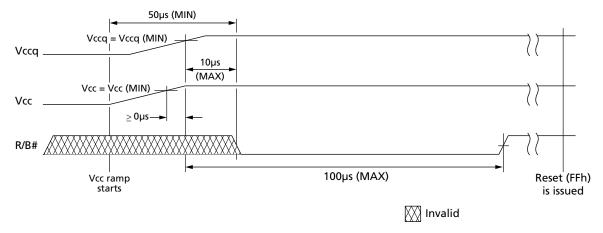

# **Device Initialization**

Some NAND Flash devices do not support  $V_{CCQ}$ . For these devices all references to  $V_{CCQ}$  are replaced with  $V_{CC}$ .

Micron NAND Flash devices are designed to prevent data corruption during power transitions.  $V_{CC}$  is internally monitored. (The WP# signal supports additional hardware protection during power transitions.) When ramping  $V_{CC}$  and  $V_{CCQ}$ , use the following procedure to initialize the device:

- 1. Ramp V<sub>CC</sub>.

- 2. Ramp  $V_{CCQ}$ .  $V_{CCQ}$  must not exceed  $V_{CC}$ .

- 3. The host must wait for R/B# to be valid and HIGH before issuing RESET (FFh) to any target (see Figure 35). The R/B# signal becomes valid when 50µs has elapsed since the beginning the  $V_{CC}$  ramp, and 10µs has elapsed since  $V_{CCQ}$  reaches  $V_{CCQ}$  (MIN) and  $V_{CC}$  reaches  $V_{CC}$  (MIN).

- 4. If not monitoring R/B#, the host must wait at least 100 $\mu$ s after V<sub>CCQ</sub> reaches V<sub>CCQ</sub> (MIN) and V<sub>CC</sub> reaches V<sub>CC</sub> (MIN). If monitoring R/B#, the host must wait until R/B# is HIGH.

- 5. The asynchronous interface is active by default for each target. Each LUN draws less than an average of  $10mA (I_{ST})$  measured over intervals of 1ms until the RESET (FFh) command is issued.

- 6. The RESET (FFh) command must be the first command issued to all targets (CE#s) after the NAND Flash device is powered on. Each target will be busy for <sup>t</sup>POR after a RESET command is issued. The RESET busy time can be monitored by polling R/B# or issuing the READ STATUS (70h) command to poll the status register.

- 7. The device is now initialized and ready for normal operation.

At power-down,  $V_{CCQ}$  must go LOW, either before, or simultaneously with,  $V_{CC}$  going LOW.

### Figure 35: R/B# Power-On Behavior

Note: 1. Disregard  $V_{CCQ}$  for devices that use only  $V_{CC}$ .

# **Activating Interfaces**

After performing the steps under Device Initialization (page 45), the asynchronous interface is active for all targets on the device.

Each target's interface is independent of other targets, so the host is responsible for changing the interface for each target.

If the host and NAND Flash device, through error, are no longer using the same interface, then steps under Activating the Asynchronous Interface are performed to resynchronize the interfaces.

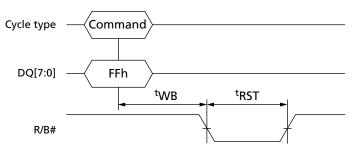

## **Activating the Asynchronous Interface**

To activate the asynchronous NAND interface, once the synchronous interface is active, the following steps are repeated for each target:

- 1. The host pulls CE# HIGH, disables its input to CLK, and enables its asynchronous interface.

- 2. The host pulls CE# LOW and issues the RESET (FFh) command, using an asynchronous command cycle.

- 3. R/B# goes LOW for <sup>t</sup>RST.

- 4. After <sup>T</sup>ITC, and during <sup>t</sup>RST, the device enters the asynchronous NAND interface. READ STATUS (70h) and READ STATUS ENHANCED (78h) are the only commands that can be issued.

- 5. After <sup>t</sup>RST, R/B# goes HIGH. Timing mode feature address (01h), subfeature parameter P1 is set to 00h, indicating that the asynchronous NAND interface is active and that the device is set to timing mode 0.

For further details, see Reset Operations.

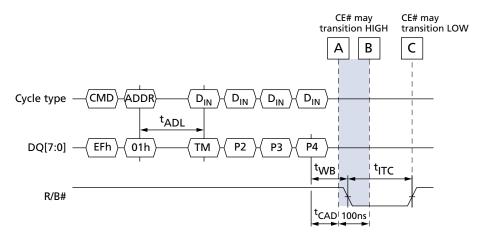

## **Activating the Synchronous Interface**

To activate the synchronous NAND Flash interface, the following steps are repeated for each target:

- 1. Issue the SET FEATURES (EFh) command.

- 2. Write address 01h, which selects the timing mode.

- 3. Write P1 with 1Xh, where "X" is the timing mode used in the synchronous interface (see Configuration Operations).

- 4. Write P2–P4 as 00h-00h-00h.

- 5. R/B# goes LOW for <sup>t</sup>ITC. The host should pull CE# HIGH. During <sup>t</sup>ITC, the host should not issue any type of command, including status commands, to the NAND Flash device.

- 6. After <sup>t</sup>ITC, R/B# goes HIGH and the synchronous interface is enabled. Before pulling CE# LOW, the host should enable the clock.

# 32Gb, 64Gb, 128Gb, 256Gb Asynchronous/Synchronous NAND Activating Interfaces

### Figure 36: Activating the Synchronous Interface

Note: 1. TM = Timing mode.

# 32Gb, 64Gb, 128Gb, 256Gb Asynchronous/Synchronous NAND Command Definitions

# **Command Definitions**

### Table 5: Command Set

| Command                        | Command<br>Cycle #1 | Number of<br>Valid<br>Address<br>Cycles | Data<br>Input<br>Cycles | Command<br>Cycle #2 | Valid While<br>Selected LUN<br>is Busy <sup>1</sup> | Valid While<br>Other LUNs<br>are Busy <sup>2</sup> | Notes |

|--------------------------------|---------------------|-----------------------------------------|-------------------------|---------------------|-----------------------------------------------------|----------------------------------------------------|-------|

| Reset Operations               |                     |                                         |                         | -                   | ·                                                   |                                                    |       |

| RESET                          | FFh                 | 0                                       | -                       | -                   | Yes                                                 | Yes                                                |       |

| SYNCHRONOUS RESET              | FCh                 | 0                                       | -                       | -                   | Yes                                                 | Yes                                                |       |

| <b>Identification Operatio</b> | ns                  |                                         |                         |                     |                                                     |                                                    |       |

| READ ID                        | 90h                 | 1                                       | -                       | -                   |                                                     |                                                    | 3     |

| READ PARAMETER PAGE            | ECh                 | 1                                       | _                       | -                   |                                                     |                                                    |       |

| READ UNIQUE ID                 | EDh                 | 1                                       | _                       | _                   |                                                     |                                                    |       |

| <b>Configuration Operatio</b>  | ons                 |                                         |                         |                     |                                                     |                                                    | 1     |

| GET FEATURES                   | EEh                 | 1                                       | _                       | -                   |                                                     |                                                    | 3     |

| SET FEATURES                   | EFh                 | 1                                       | 4                       | -                   |                                                     |                                                    | 4     |

| Status Operations              |                     |                                         |                         |                     | I I                                                 |                                                    | •     |

| READ STATUS                    | 70h                 | 0                                       | _                       | -                   | Yes                                                 |                                                    |       |

| READ STATUS ENHANCED           | 78h                 | 3                                       | _                       | -                   | Yes                                                 | Yes                                                |       |

| Column Address Opera           | tions               |                                         |                         |                     | <u> </u>                                            |                                                    | •     |

| CHANGE READ COLUMN             | 05h                 | 2                                       | -                       | E0h                 |                                                     | Yes                                                |       |

| CHANGE READ COLUMN<br>ENHANCED | 06h                 | 5                                       | -                       | E0h                 |                                                     | Yes                                                |       |

| CHANGE WRITE COLUMN            | 85h                 | 2                                       | Optional                | -                   |                                                     | Yes                                                |       |

| CHANGE ROW ADDRESS             | 85h                 | 5                                       | Optional                | -                   |                                                     | Yes                                                | 5     |

| Read Operations                |                     |                                         |                         | -1                  |                                                     |                                                    |       |

| READ MODE                      | 00h                 | 0                                       | -                       | -                   |                                                     | Yes                                                |       |

| READ PAGE                      | 00h                 | 5                                       | -                       | 30h                 |                                                     | Yes                                                | 6     |

| READ PAGE MULTI-<br>PLANE      | 00h                 | 5                                       | _                       | 32h                 |                                                     | Yes                                                |       |

| READ PAGE CACHE<br>SEQUENTIAL  | 31h                 | 0                                       | _                       | -                   |                                                     | Yes                                                | 7     |

| READ PAGE CACHE<br>RANDOM      | 00h                 | 5                                       | -                       | 31h                 |                                                     | Yes                                                | 6,7   |

| READ PAGE CACHE LAST           | 3Fh                 | 0                                       | _                       | -                   |                                                     | Yes                                                | 7     |

| Program Operations             |                     |                                         |                         |                     |                                                     |                                                    |       |

| PROGRAM PAGE                   | 80h                 | 5                                       | Yes                     | 10h                 |                                                     | Yes                                                |       |

| PROGRAM PAGE<br>MULTI-PLANE    | 80h                 | 5                                       | Yes                     | 11h                 |                                                     | Yes                                                |       |