# Dual-channel low-side 5 A gate driver ICs with low output resistance and excellent timing accuracy in TSNP leadless package

## **Description**

The EiceDRIVER™ 2EDN7534U is offered in a small and versatile 6-pin TSNP package. High output current capability together with active output voltage clamping, tight timing specifications, and optimized start-up and shut-down times, make the 2EDN7534U the first choice for many fast-switching space constrained applications.

#### **Product features**

- ±5 A source/sink currents

- 19 ns typ. propagation delay

- +6/-4 ns propagation delay accuracy

- 1.8 μs output start-up time

- 500 ns output shut-down time

- · Active output voltage clamping

- -12 V input robustness

- 5 A reverse current robustness

- 4 V UVLO option

- Package option:

- 6-pin TSNP package

- Fully qualified for industrial applications according to JEDEC

#### **Applications**

- Switch-mode power-supplies

- DC-DC power converters

- Synchronous rectification stages

#### **Available device configurations**

| Dook output surrent | Innut config  | 6-pin TSNP |  |

|---------------------|---------------|------------|--|

| Peak output current | Input config. | 4V UVLO    |  |

| 5 A                 | non inverting | 2EDN7534U  |  |

# Dual-channel 5 A, high-speed, low-side gate driver ICs

#### **Table of Contents**

# **Table of Contents**

|                                      | Description                                                                                                                                                                                                                                                                                | 1               |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

|                                      | Table of Contents                                                                                                                                                                                                                                                                          | 2               |

| <b>1</b><br>1.1<br>1.2               | Product versions       Logic configuration versions         Package versions                                                                                                                                                                                                               | 3               |

| <b>2</b><br>2.1                      | Pin configuration and description                                                                                                                                                                                                                                                          |                 |

| 3                                    | Block diagram                                                                                                                                                                                                                                                                              | 5               |

| 44.1 4.2 4.3 4.4 4.5 4.6 5.1 5.2 5.3 | Functional description Introduction Supply voltage Undervoltage lockout (UVLO) function Input configurations Driver outputs Active output voltage clamping  Electrical characteristics Absolute maximum ratings Thermal characteristics Operating range General electrical characteristics | 6 6 6 7 7 8 8 8 |

| 6                                    | Timing diagrams                                                                                                                                                                                                                                                                            | 12              |

| 7                                    | Typical characteristics                                                                                                                                                                                                                                                                    | 14              |

| 8                                    | Application and implementation                                                                                                                                                                                                                                                             | 17              |

| <b>9</b><br>9.1<br>9.2               | Package outlines          Device numbers and markings          PG-TSNP-6                                                                                                                                                                                                                   | 18              |

| 10                                   | Revision history                                                                                                                                                                                                                                                                           | 21              |

#### Dual-channel 5 A, high-speed, low-side gate driver ICs

**Product versions**

#### 1 Product versions

The EiceDRIVER™ 2EDN7534U is available in a direct logic configuration and 4 V undervoltage lockout level.

## 1.1 Logic configuration versions

**Table 1** describes the logic dependence of the output state from undervoltage lockout (UVLO) and input pins. If a UVLO event is triggered, both OUTA and OUTB are kept in a low state, regardless of the input pins status.

The functional description is in **Chapter 3** (**Block diagram**) and **Chapter 4** (**Functional description**).

Table 1 Logic table for TSNP-6 pin package

|     | Inputs | Direct output      |      |      |

|-----|--------|--------------------|------|------|

| INA | INB    | UVLO <sup>1)</sup> | OUTA | OUTB |

| Х   | х      | active             | L    | L    |

| L   | L      | inactive           | L    | L    |

| Н   | L      | inactive           | Н    | L    |

| L   | Н      | inactive           | L    | Н    |

| Н   | Н      | inactive           | Н    | Н    |

<sup>1)</sup> Inactive UVLO:  $V_{DD}$  is above UVLO<sub>ON</sub> voltage threshold and control logic drives the output stage Active UVLO: an undervoltage lockout event has been triggered

## 1.2 Package versions

The EiceDRIVER™ 2EDN7534U is available in one package version. The package type is identified by the last character in the product code:

ultra tiny PG-TSNP-6 is designated by "U" (e.g. 2EDN7534U)

Package drawings are available in **Chapter 9** (**Package outlines**).

## Dual-channel 5 A, high-speed, low-side gate driver ICs

Pin configuration and description

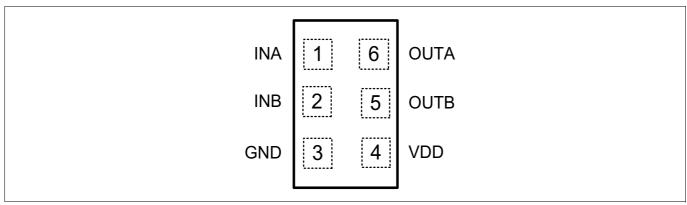

# 2 Pin configuration and description

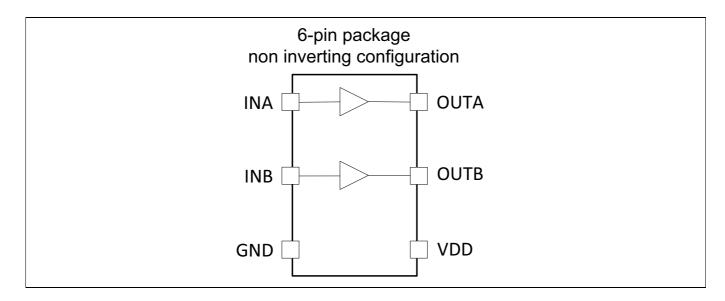

## 2.1 Input configuration for PG-TSNP-6 package

The pin configuration of EiceDRIVER™ 2EDN7534U in the PG-TSNP-6 package is shown in **Figure 1**. Drawings can be viewed in **Chapter 9.2** (**PG-TSNP-6**).

Figure 1 Pin configuration PG-TSNP-6, top view

Table 2 Pin configuration for PG-TSNP-6 package

| Pin<br>number | Symbol | Description                                                                  |

|---------------|--------|------------------------------------------------------------------------------|

| 1             | INA    | Input signal channel A Logic input, controlling OUTA (non-inverting)         |

| 2             | INB    | Input signal channel B Logic input, controlling OUTB (non-inverting)         |

| 3             | GND    | Ground Gate driver reference ground                                          |

| 4             | VDD    | Positive supply voltage Operating range 4.5 V to 20 V                        |

| 5             | OUTB   | Driver output channel B Low-impedance output with source and sink capability |

| 6             | OUTA   | Driver output channel A Low-impedance output with source and sink capability |

**Block diagram**

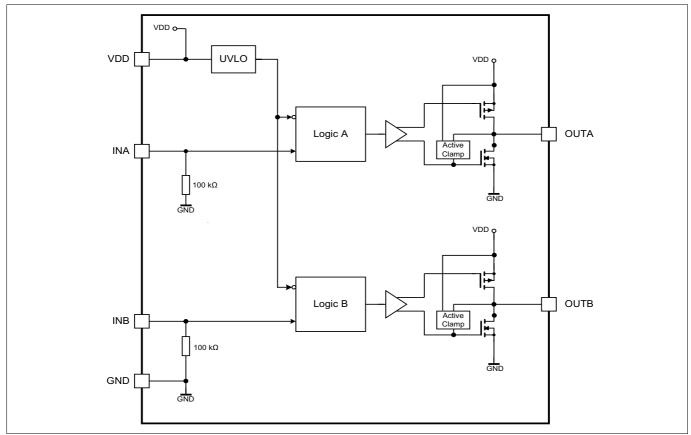

# 3 Block diagram

Simplified functional block diagrams for the TSNP-6 package is shown in **Figure 2**. Please refer to functional description in **Chapter 4**.

Figure 2 Simplified block diagram for direct/non-inverting input configuration, 6-pin package

## Dual-channel 5 A, high-speed, low-side gate driver ICs

**Functional description**

## 4 Functional description

#### 4.1 Introduction

The EiceDRIVER™ 2EDN7534U is a fast dual-channel driver for low-side switches. Two true rail-to-rail output stages with very low output impedance and high current capability are chosen to ensure high flexibility and cover a high variety of applications.

An extended negative voltage range protects input pins against ground shifts. No current flows over the ESD structure in the IC during a negative input level. All outputs are robust against reverse current. During the interaction with the power MOSFET, reverse reflected power is handled by the internal output stage.

All inputs are compatible with LV-TTL signal levels. The threshold voltages have a typical hysteresis of 0.9 V, that is constant over the supply voltage range.

EiceDRIVER™ 2EDN7534U ensures optimal performance in fast-switching applications because of the low delays and rise/fall times. The maximum skew between Channel A and Channel B is 2 ns.

#### 4.2 Supply voltage

The maximum operating supply voltage is 20 V. This high voltage is valuable in order to exploit the full current capability of EiceDRIVER $^{\text{TM}}$  2EDN7534U when driving low  $R_{\text{DSON}}$  MOSFETs. The minimum operating supply voltage is set by the undervoltage lockout function to a typical default values of 4.2 V for the 4 V-UVLO variant.

## 4.3 Undervoltage lockout (UVLO) function

The undervoltage lockout function ensures that the output can be switched to its high level only if the supply voltage exceeds the UVLO threshold voltage. This protects power MOSFETs from running into linear mode, preventing excessive power dissipation if the voltage is not enough to completely turn on the switches.

The UVLO level is set to a typical value of 4.2 V (with hysteresis). UVLO of 4.2 V is normally used for logic level MOSFETs.

Table 3 UVLO turn-on and turn-off thresholds

| Nominal UVLO level | UVLO turn-on threshold (typ.) | UVLO turn-off threshold (typ.) |

|--------------------|-------------------------------|--------------------------------|

| 4.2 V              | 4.2 V                         | 3.9 V                          |

#### 4.4 Input configurations

As described in **Chapter 1**, EiceDRIVER™ 2EDN7534U is available in a non inverting configuration with respect to the logic of the input pins.

The direct PWM inputs are internally pulled down to a logic low voltage. This prevents a switch-on event during power up and a not driven input condition.

All inputs are compatible with LV-TTL levels and provide a hysteresis of 0.9 V typ. This hysteresis is independent of the supply voltage.

All input pins have a negative extended voltage range. This prevents cross-current over single wires during GND shifts between signal source (controller) and driver input.

## Dual-channel 5 A, high-speed, low-side gate driver ICs

#### **Functional description**

#### 4.5 Driver outputs

The two rail-to-rail output stages realized with complementary MOS transistors are able to provide a maximum sinking/sourcing current of 5 A. This driver output stage has a shoot-through protection and current limiting behavior. After a switching event, current limitation is raised up to achieve the typical current peak for an excellent fast reaction time of the following power MOS transistor.

The output impedances for the sourcing p-channel MOS have typical values of  $0.8~\Omega$  for 2EDN7534U. The output impedances for the sinking n-channel MOS transistor have typical values of  $0.6~\Omega$  for 2EDN7534U. The use of a p-channel sourcing transistor is crucial for achieving true rail-to-rail behavior and avoiding a source follower's voltage drop.

Gate drive outputs are kept actively low in case of floating INx inputs, or during startup or power down if the supply voltage is below the UVLO threshold.

#### 4.6 Active output voltage clamping

The undervoltage lockout (UVLO) protection ensures no driver operation when the supply voltage is below the UVLO threshold. However, this is not sufficient to keep output low when  $V_{\rm DD}$  is far below the UVLO threshold. As a result, fast dv/dt of the switches could trigger undesired  $V_{\rm gs}$  of the driven device, leading to abnormal turn-ons.

The fast active output voltage clamping of EiceDRIVER $^{\text{TM}}$  2EDN7534U is intended to actively keep the driver output low when the VDD voltage is between 1.2 V and UVLO $_{\text{ON}}$  threshold, overcoming the unwanted turn-on issue listed above and ensuring safe off state before device operation.

This structure allows fast reaction and effective clamping of the output pins (OUTx). The exact reaction time depends on the power supply  $(V_{DD})$  and on the output voltage levels. Undervoltage Lockout together with the output active clamping ensure that the output is actively held low in case of insufficient supply voltage.

Table 4 Logic table in case of insufficient supply voltages

| Inputs | Supplies                                                      | Output |

|--------|---------------------------------------------------------------|--------|

| INx    | $V_{ m DD}$                                                   | OUTx   |

| X      | $1.2 \text{ V} < V_{\text{DD}} < \text{UVLO}_{\text{VDD,ON}}$ | L      |

#### Dual-channel 5 A, high-speed, low-side gate driver ICs

#### **Electrical characteristics**

#### 5 Electrical characteristics

Note:

The absolute maximum ratings are listed in **Table 5**. Stresses beyond these values may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## 5.1 Absolute maximum ratings

Table 5 Absolute maximum ratings

| Parameter                               | Symbol                                     | Values  |      |                       | Unit            | Note or Test Condition                  |

|-----------------------------------------|--------------------------------------------|---------|------|-----------------------|-----------------|-----------------------------------------|

|                                         |                                            | Min.    | Тур. | Max.                  |                 |                                         |

| Positive supply voltage                 | $V_{\mathrm{DD}}$                          | -0.3    | _    | 22                    | V               | -                                       |

| Voltage at pins INA, INB                | $V_{IN}$                                   | -12     | _    | 22                    | V               | -                                       |

| Voltage at pins OUTA, OUTB              | $V_{OUT}$                                  | -0.3    | _    | V <sub>DD</sub> + 0.3 | V               | 1)                                      |

|                                         |                                            | -2      | _    | V <sub>DD</sub> + 2   | V               | Repetitive pulse < 200 ns <sup>2)</sup> |

| Reverse current peak at pins OUTA, OUTB | I <sub>SNKREV</sub><br>I <sub>SRCREV</sub> | -5<br>- | -    | -<br>5                | A <sub>pk</sub> | < 500 ns                                |

| Junction temperature                    | $T_{J}$                                    | -40     | _    | 150                   | °C              | -                                       |

| Storage temperature                     | $T_{S}$                                    | -55     | _    | 150                   | °C              | -                                       |

| ESD capability                          | V <sub>ESD</sub>                           | _       | _    | 0.5                   | kV              | Charged Device Model (CDM) 3)           |

| ESD capability                          | V <sub>ESD</sub>                           | -       | _    | 2.0                   | kV              | Human Body Model (HBM) 4)               |

- 1) Voltage spikes resulting from reverse current peaks are allowed

- 2) Values are verified by characterization on bench

- 3) According to JESD22-002

- 4) According to JESD22-A114-B (discharging 100 pF capacitor through 1.5  $k\Omega$  resistor)

#### 5.2 Thermal characteristics

Table 6 Thermal characteristics

| Parameter                                      | Symbol                 | Values |          |      | Unit | <b>Note or Test Condition</b> |

|------------------------------------------------|------------------------|--------|----------|------|------|-------------------------------|

|                                                |                        | Min.   | Тур.     | Max. |      |                               |

| PG-TSNP-6, T <sub>amb</sub> =25°C              | 1                      | "      | <u>"</u> |      |      |                               |

| Thermal resistance junction-<br>ambient        | R <sub>thJA25</sub>    | -      | 140      | -    | K/W  | 1)                            |

| Thermal resistance junction-case (top)         | R <sub>thJC25</sub>    | -      | 80       | -    | K/W  | 2)                            |

| Thermal resistance junction-<br>board          | R <sub>thJB25</sub>    | -      | 56       | -    | K/W  | 3)                            |

| Characterization parameter junction-case (top) | $\Psi_{\text{thJC25}}$ | -      | 1.6      | -    | K/W  | 4)                            |

| Characterization parameter junction-board      | $\Psi_{\text{thJB25}}$ | -      | 35       | -    | K/W  | 5)                            |

<sup>1)</sup> The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, high-K board, as specified in JESD51-7, in an environment described in JESD51-2a

#### Dual-channel 5 A, high-speed, low-side gate driver ICs

#### **Electrical characteristics**

- 2) The junction-to-case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDEC standard test exists, but a close description can be found in the ANSI SEMI standard G30-88

- 3) The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB temperature, as described in JESD51-8

- 4) The characterization parameter junction-top, estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $R_{th}$ , using a procedure described in JESD51-2a (sections 6 and 7)

- 5) The characterization parameter junction-board, estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $R_{th}$ , using a procedure described in JESD51-2a (sections 6 and 7)

## 5.3 Operating range

Table 7 Operating range

| Parameter            | Symbol            | Symbol Values |      |      | Unit | Note or Test Condition |

|----------------------|-------------------|---------------|------|------|------|------------------------|

|                      |                   | Min.          | Тур. | Max. |      |                        |

| Supply voltage       | $V_{\mathrm{DD}}$ | 4.5           | _    | 20   | V    | Min. defined by UVLO   |

| Logic input voltage  | V <sub>IN</sub>   | -10           | _    | 20   | V    | _                      |

| Junction temperature | $T_{J}$           | -40           | _    | 150  | °C   | 1)                     |

<sup>1)</sup> Continuous operation above 125°C may reduce life time

#### 5.4 General electrical characteristics

Unless otherwise noted, min./max. values of characteristics are the lower and upper limits respectively. They are valid within the full operating range. The supply voltage is  $V_{DD} = 12 \text{ V}$ . Typical values are given at  $T_{J} = 25 ^{\circ}\text{C}$ .

Table 8 Power supply

| Parameter             | Symbol              | Values |      |      | Unit | Note or Test Condition            |

|-----------------------|---------------------|--------|------|------|------|-----------------------------------|

|                       |                     | Min.   | Тур. | Max. |      |                                   |

| VDD quiescent current | I <sub>VDDQU1</sub> | 0.5    | 0.9  | 1.2  | mA   | OUT = high, $V_{DD}$ = 12 V       |

| VDD quiescent current | I <sub>VDDQU2</sub> | 0.3    | 0.5  | 0.7  | mA   | OUT = low, V <sub>DD</sub> = 12 V |

Table 9 Undervoltage lockout for logic level MOSFET

| Parameter                                      | Symbol Values       |      |      | Unit | <b>Note or Test Condition</b> |   |

|------------------------------------------------|---------------------|------|------|------|-------------------------------|---|

|                                                |                     | Min. | Тур. | Max. |                               |   |

| Undervoltage Lockout (UVLO) turn on threshold  | UVLO <sub>ON</sub>  | -    | 4.2  | 4.5  | V                             | - |

| Undervoltage Lockout (UVLO) turn off threshold | UVLO <sub>OFF</sub> | 3.6  | 3.9  | -    | V                             | - |

| UVLO threshold hysteresis                      | UVLO <sub>HYS</sub> | 0.25 | 0.3  | 0.35 | V                             | - |

## Dual-channel 5 A, high-speed, low-side gate driver ICs

#### **Electrical characteristics**

Table 10 Logic inputs INA, INB

| Parameter                                 | Symbol           | Values |      |      | Unit | Note or Test Condition |

|-------------------------------------------|------------------|--------|------|------|------|------------------------|

|                                           |                  | Min.   | Тур. | Max. |      |                        |

| Input voltage threshold for transition LH | V <sub>INH</sub> | 1.9    | 2.1  | 2.3  | V    | -                      |

| Input voltage threshold for transition HL | V <sub>INL</sub> | 1.0    | 1.2  | 1.4  | V    | -                      |

| Input pull down resistor                  | R <sub>INL</sub> | -      | 100  | -    | kΩ   | 1)                     |

<sup>1)</sup> Inputs with initial low logic level

Table 11 Static output characteristics for 2EDN753x

| Parameter                                                              | Symbol               |      | Values |      |   | <b>Note or Test Condition</b> |  |

|------------------------------------------------------------------------|----------------------|------|--------|------|---|-------------------------------|--|

|                                                                        |                      | Min. | Тур.   | Max. |   |                               |  |

| High level (sourcing) output resistance <sup>1)</sup>                  | R <sub>ONSRC</sub>   | 0.4  | 0.8    | 1.4  | Ω | I <sub>SRC</sub> = 50 mA      |  |

| High level (sourcing) output current 1)                                | I <sub>SRCPEAK</sub> | _    | 5.0    | _    | А | -                             |  |

| Low level (sinking) output $R_{\text{ONSNK}}$ resistance <sup>1)</sup> |                      | 0.35 | 0.6    | 1.2  | Ω | I <sub>SNK</sub> = 50 mA      |  |

| Low level (sinking) output current 1)                                  | I <sub>SNKPEAK</sub> | -    | -5.0   | _    | A | -                             |  |

<sup>1)</sup> Parameter is not subject to production test - verified by design/characterization

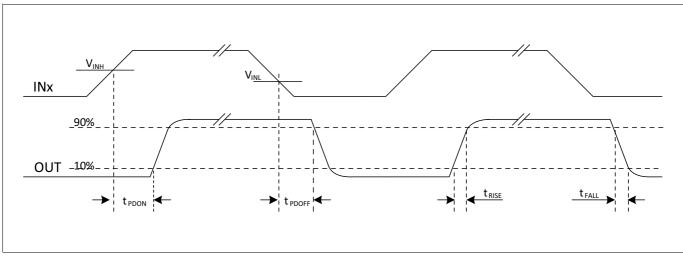

Table 12 Dynamic Characteristics (see Figure 3, Figure 4, Figure 5 and Figure 6)

| Parameter                                                                            | Symbol                  | Values    |     |      | Unit | <b>Note or Test Condition</b>                                                             |  |  |

|--------------------------------------------------------------------------------------|-------------------------|-----------|-----|------|------|-------------------------------------------------------------------------------------------|--|--|

|                                                                                      |                         | Min. Typ. |     | Max. |      |                                                                                           |  |  |

| Input to output propagation delay                                                    | t <sub>PDlh</sub>       | 15        | 19  | 25   | ns   | $C_{\text{LOAD}}$ = 1.8 nF, $V_{\text{DD}}$ = 12 V;<br>low to high transition at<br>Input |  |  |

| Input to output propagation delay                                                    | $t_{PDhl}$              | 15        | 19  | 25   | ns   | $C_{\rm LOAD}$ = 1.8 nF, $V_{\rm DD}$ = 12 V high to low transition at Input              |  |  |

| Input to output propagation delay mismatch between the two channels on the same IC   | $\Delta t_{	extsf{PD}}$ | -         | -   | 2    | ns   | -                                                                                         |  |  |

| Rise time 1)                                                                         | $t_{RISE}$              | _         | 8.6 | 15   | ns   | $C_{LOAD} = 1.8 \text{ nF}, V_{DD} = 12 \text{ V}$                                        |  |  |

| Fall time 1)                                                                         | t <sub>FAll</sub>       | _         | 6   | 13   | ns   | $C_{LOAD} = 1.8 \text{ nF}, V_{DD} = 12 \text{ V}$                                        |  |  |

| Minimum input pulse width that changes output state 1)                               | t <sub>PW</sub>         | _         | 6   | 10   | ns   | $C_{LOAD} = 1.8 \text{ nF}, V_{DD} = 12 \text{ V}$                                        |  |  |

| $V_{\rm DD}$ start-up time <sup>1)</sup> from UVLO <sub>ON</sub> to OUT <sub>x</sub> | $t_{START}$             | -         | 1.8 | -    | μs   | V <sub>DD</sub> rising to 12 V;<br>see <b>Figure 4</b>                                    |  |  |

## Dual-channel 5 A, high-speed, low-side gate driver ICs

#### **Electrical characteristics**

Dynamic Characteristics (see Figure 3, Figure 4, Figure 5 and Figure 6) Table 12

| Parameter                                                                                            | Symbol          | Values |          |   | Unit | <b>Note or Test Condition</b>                             |  |

|------------------------------------------------------------------------------------------------------|-----------------|--------|----------|---|------|-----------------------------------------------------------|--|

|                                                                                                      |                 | Min.   | . Typ. M |   |      |                                                           |  |

| $\overline{V_{\rm DD}}$ deactivation time <sup>1)</sup> from UVLO <sub>OFF</sub> to OUT <sub>x</sub> | $t_{STOP}$      | -      | 500      | _ | ns   | V <sub>DD</sub> falling from 12 V;<br>see <b>Figure 4</b> |  |

| Activation time of output clamping in UVLO condition 1)                                              | $t_{CLAMP,OUT}$ | -      | 20       | _ | ns   | see <b>Figure 6</b>                                       |  |

<sup>1)</sup> Parameter is not subject to production test - verified by component verification

**Timing diagrams**

# 6 Timing diagrams

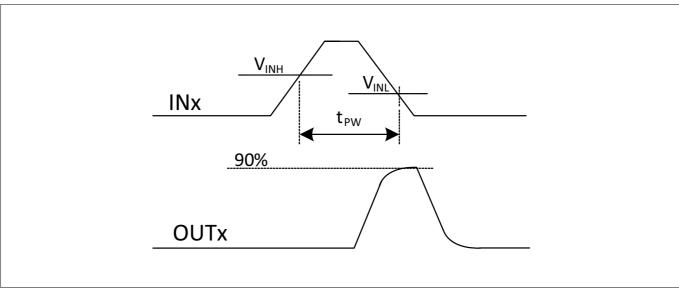

Figure 3 shows the definition of rise, fall and delay times for the inputs of the non-inverting/direct version.

Figure 3 Propagation delay, rise and fall time definition for the direct/non-inverting configuration

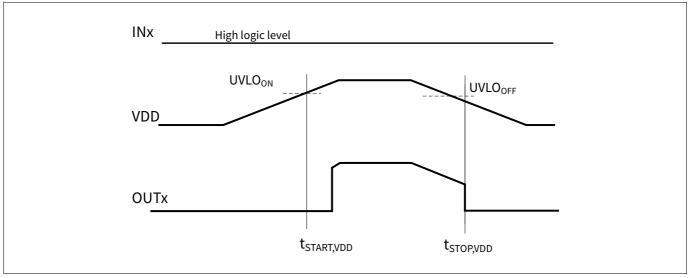

Figure 4 illustrates the undervoltage lockout function.

Figure 4 UVLO behaviour

## Dual-channel 5 A, high-speed, low-side gate driver ICs

#### **Timing diagrams**

Figure 5 illustrates the minimum input pulse width that changes output state.

Figure 5 Minimum input pulse width definition

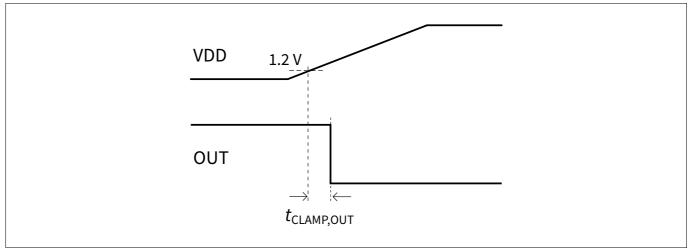

Figure 6 illustrates  $t_{\text{CLAMP,OUT}}$ , the time required to clamp potential output induced overshoots in UVLO condition  $(VDD < UVLO_{ON})$ .

Activation time of output clamping in UVLO conditions (unloaded output) Figure 6

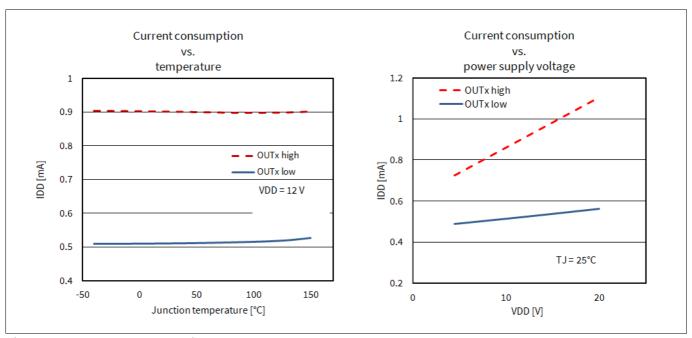

**Typical characteristics**

#### **Typical characteristics** 7

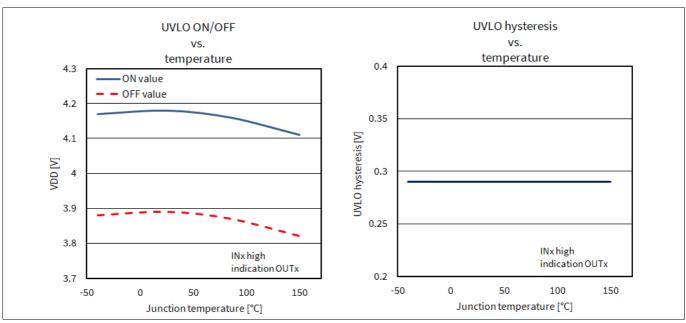

Figure 7 Typical undervoltage lockout behavior vs. temperature for 2EDN7x (4 V)

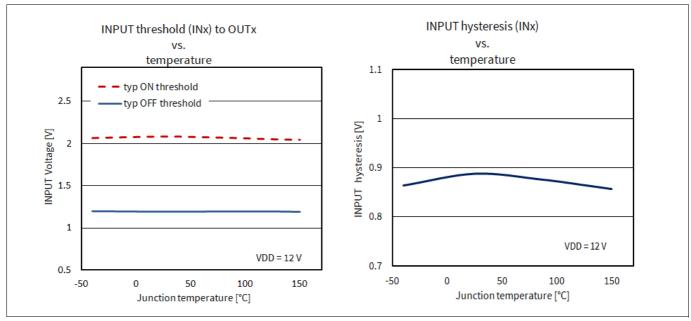

Figure 8 Input characteristics (INx)

## Dual-channel 5 A, high-speed, low-side gate driver ICs

#### **Typical characteristics**

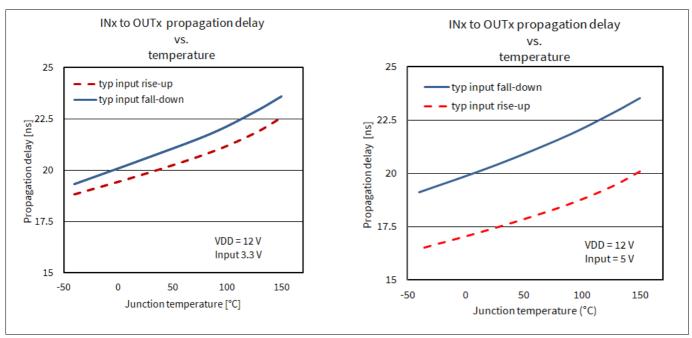

Figure 9 Propagation delay (INx) on different input logic levels (see Figure 3)

Figure 10 Rise/fall times with load on output (see Figure 3)

## Dual-channel 5 A, high-speed, low-side gate driver ICs

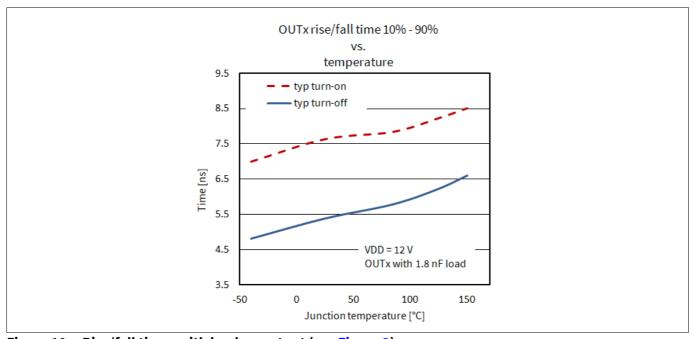

#### **Typical characteristics**

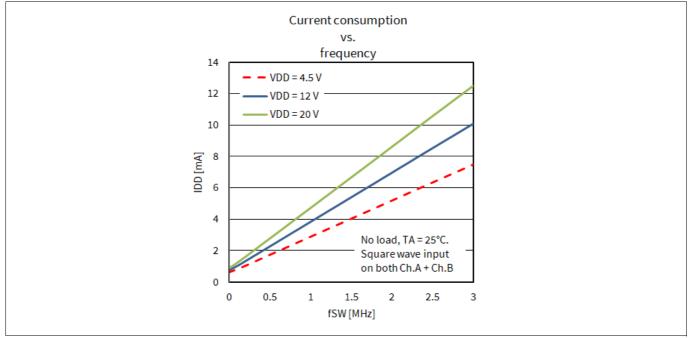

Figure 11 Power consumption related to temperature and power supply

Figure 12 Current consumption versus frequency

**Application and implementation**

#### **Application and implementation** 8

Note:

The following information is given as an example for the implementation of the device only and shall not be regarded as a description or warranty of a certain functionality, condition or quality of the device.

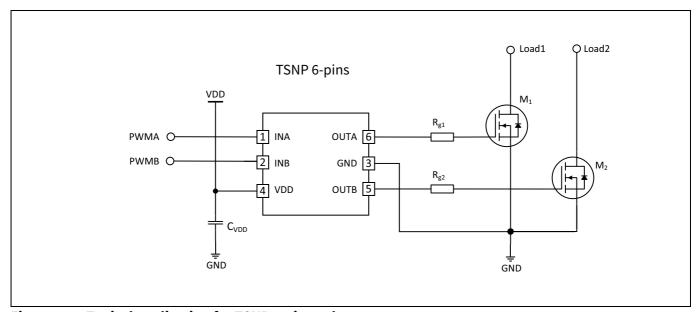

Figure 13 shows a typical application for 6-pin package version.

Figure 13 Typical application for TSNP-6 pin package

## Dual-channel 5 A, high-speed, low-side gate driver ICs

#### **Package outlines**

## 9 Package outlines

Note: For further information on package types, recommendation for board assembly, please go to:

Infineon packages.

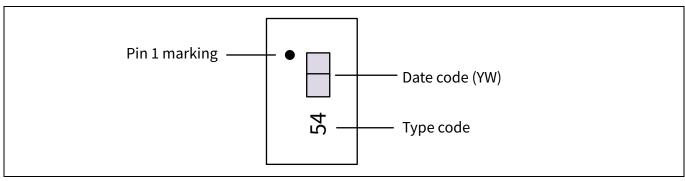

## 9.1 Device numbers and markings

Table 13 Product versions

| Part number | Orderable part number (OPN) | Device marking         |  |  |

|-------------|-----------------------------|------------------------|--|--|

| 2EDN7534U   | 2EDN7534UXTSA1              | YW <sup>1)</sup><br>54 |  |  |

<sup>1)</sup> The date code digits "Y" and "W" in device marking for the TSNP-6 package are explained in **Table 14** and **Table 15**

Figure 14 Package marking (PG-TSNP-6)

Table 14 Year date code marking - digit "Y"

| Year | Υ | Year | Υ | Year | Υ |

|------|---|------|---|------|---|

| 2000 | 0 | 2010 | 0 | 2020 | 0 |

| 2001 | 1 | 2011 | 1 | 2021 | 1 |

| 2002 | 2 | 2012 | 2 | 2022 | 2 |

| 2003 | 3 | 2013 | 3 | 2023 | 3 |

| 2004 | 4 | 2014 | 4 | 2024 | 4 |

| 2005 | 5 | 2015 | 5 | 2025 | 5 |

| 2006 | 6 | 2016 | 6 | 2026 | 6 |

| 2007 | 7 | 2017 | 7 | 2027 | 7 |

| 2008 | 8 | 2018 | 8 | 2028 | 8 |

| 2009 | 9 | 2019 | 9 | 2029 | 9 |

## Dual-channel 5 A, high-speed, low-side gate driver ICs

#### **Package outlines**

Week date code marking - digit "W" Table 15

| Week | W |

|------|---|------|---|------|---|------|---|------|---|

| 1    | Α | 12   | N | 23   | 4 | 34   | h | 45   | V |

| 2    | В | 13   | Р | 24   | 5 | 35   | j | 46   | х |

| 3    | С | 14   | Q | 25   | 6 | 36   | k | 47   | у |

| 4    | D | 15   | R | 26   | 7 | 37   | l | 48   | Z |

| 5    | E | 16   | S | 27   | a | 38   | n | 49   | 8 |

| 6    | F | 17   | T | 28   | b | 39   | р | 50   | 9 |

| 7    | G | 18   | U | 29   | С | 40   | q | 51   | 2 |

| 8    | Н | 19   | ٧ | 30   | d | 41   | r | 52   | 3 |

| 9    | J | 20   | W | 31   | е | 42   | S | _    | _ |

| 10   | К | 21   | Υ | 32   | f | 43   | t | -    | _ |

| 11   | L | 22   | Z | 33   | g | 44   | u | _    | _ |

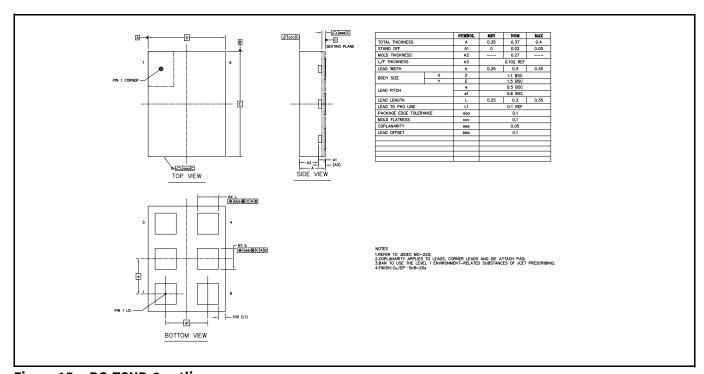

#### **PG-TSNP-6** 9.2

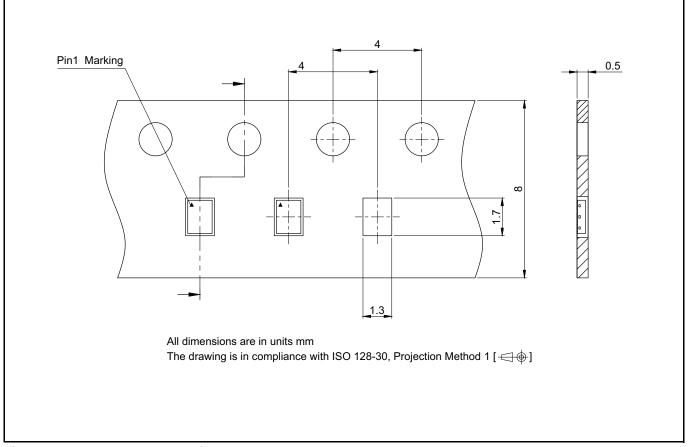

Figure 15 PG-TSNP-6 outline

#### **Package outlines**

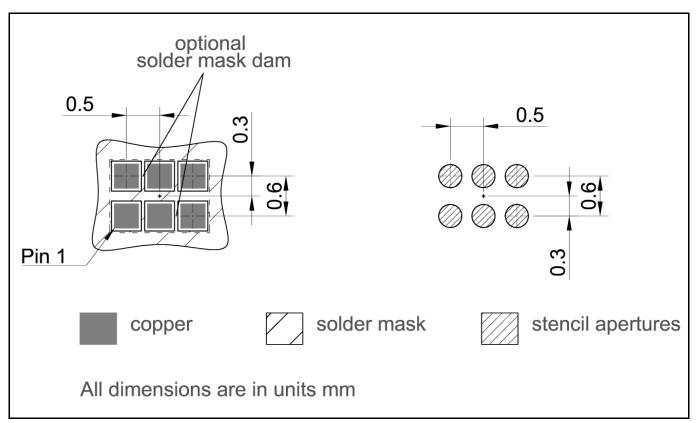

Figure 16 PG-TSNP-6 footprint

Figure 17 PG-TSNP-6 packaging

## Dual-channel 5 A, high-speed, low-side gate driver ICs

**Revision history**

# 10 Revision history

| Version | Date       | Changes                                 |

|---------|------------|-----------------------------------------|

| Rev.1.1 | 2024-03-12 | Replaced Figure 17                      |

| Rev.1.0 | 2024-02-13 | Datasheet release for 2EDN7534U version |

#### Trademarks

Edition 2024-03-12 Published by Infineon Technologies AG 81726 Munich, Germany

© 2024 Infineon Technologies AG. All Rights Reserved.

Do you have a question about any aspect of this document?

Email: erratum@infineon.com

Document reference EiceDRIVER™ 2EDN7534U

#### IMPORTANT NOTICE

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie").

With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### WARNINGS

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.