# **PNP Silicon Transistor**

Rev. V2

#### **Features**

- Available in JAN, JANTX, JANTXV and JANS per MIL-PRF-19500/512

- 2N4029 available in TO-18

- 2N4033 available in TO-39, UA and UB package styles

- Suitable for High Speed Switching and Driver Applications

#### **Electrical Characteristics**

| Parameter                             | Test Conditions                                                                                                                                                                 | Symbol                                                                       | Units | Min.                  | Max.                   |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-------|-----------------------|------------------------|

| Off Characteristics                   |                                                                                                                                                                                 |                                                                              |       |                       |                        |

| Collector - Base Cutoff Current       | V <sub>CB</sub> = -80 V dc                                                                                                                                                      | I <sub>CBO1</sub>                                                            | μA dc | _                     | -10                    |

| Emitter - Base Cutoff Current         | V <sub>EB</sub> = -5 V dc                                                                                                                                                       | I <sub>EBO1</sub>                                                            | μA dc | _                     | -10                    |

| Collector - Base Cutoff Current       | V <sub>CB</sub> = -60V dc                                                                                                                                                       | I <sub>CBO2</sub>                                                            | nA dc | _                     | -10                    |

| Collector - Emitter Cutoff Current    | $V_{BE} = -2.0 \text{ V dc}; V_{CE} = -60 \text{V dc}$                                                                                                                          | I <sub>CEX1</sub>                                                            | nA dc | _                     | -25                    |

| Base - Emitter Cutoff Current         | V <sub>BE</sub> = -3.0 V dc                                                                                                                                                     | I <sub>EBO2</sub>                                                            | nA dc | _                     | -25                    |

| Collector-Base Cutoff Current         | $T_A = +150^{\circ}C$<br>$V_{CB} = -60 \text{ V dc}$                                                                                                                            | I <sub>CBO3</sub>                                                            | μA dc | _                     | -25                    |

| On Characteristics                    |                                                                                                                                                                                 |                                                                              |       |                       |                        |

| Forward Current Transfer Ratio        | $V_{CE}$ = -5.0 V dc; $I_{C}$ = -100 $\mu A$ dc $V_{CE}$ = -5.0 V dc; $I_{C}$ = -100 mA dc $V_{CE}$ = -5.0 V dc; $I_{C}$ = -500 mA dc $V_{CE}$ = -5.0 V dc; $I_{C}$ = -1.0 A dc | h <sub>FE1</sub><br>h <sub>FE2</sub><br>h <sub>FE3</sub><br>h <sub>FE4</sub> | -     | 50<br>100<br>70<br>25 | 300                    |

| Collector - Emitter Saturated Voltage | $I_C$ = -150 mA dc; $I_B$ = -15 mA dc<br>$I_C$ = -500 mA dc; $I_B$ = -50 mA dc<br>$I_C$ = -1.0 A dc; $I_B$ = -100 mA dc                                                         | V <sub>CE(SAT)1</sub><br>V <sub>CE(SAT)2</sub><br>V <sub>CE(SAT)3</sub>      | V dc  | _                     | -0.15<br>-0.50<br>-1.0 |

| Base - Emitter Saturated Voltage      | $I_C$ = -150 mA dc; $I_B$ = -15 mA dc $I_C$ = -500 mA dc; $I_B$ = -50 mA dc                                                                                                     | V <sub>BE(SAT)1</sub>                                                        | V dc  | _                     | -0.9<br>-1.2           |

| Forward Current Transfer Ratio        | $T_A = -55^{\circ}\text{C}$<br>$V_{CE} = -5.0 \text{ V dc}; I_C = -500 \text{ mA dc}$                                                                                           | h <sub>FE5</sub>                                                             | -     | 30                    |                        |

# **PNP Silicon Transistor**

Rev. V2

| Parameter                                                                             | Test Conditions                                                                         | Symbol           | Units | Min. | Max. |

|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------------------|-------|------|------|

| Dynamic Characteristics                                                               |                                                                                         |                  |       |      |      |

| Magnitude of Common Emitter Small-Signal Short-Circuit Forward Current Transfer Ratio | $V_{CE}$ = -10 V dc; $I_{C}$ = -50 mA dc; f = 100 MHz                                   | h <sub>FE</sub>  | -     | 1.5  | 6.0  |

| Open Circuit Output Capacitance                                                       | V <sub>CB</sub> = -10 V dc; I <sub>E</sub> = 0; 100 kHz <u>&lt;</u> f <u>&lt;</u> 1 MHz | C <sub>obo</sub> | pF    | _    | 20   |

| Input Capacitance (Output Open-Circuited)                                             | $V_{EB}$ = -0.5 V dc; $I_{C}$ = 0; 100 kHz $\leq$ f $\leq$ 1 MHz                        | C <sub>ibo</sub> | pF    | _    | 80   |

| Pulse Response                                                                        |                                                                                         |                  |       |      |      |

| On-Time                                                                               | $I_{\rm C}$ = -500 mA dc; $I_{\rm B1}$ = -50 mA dc                                      | td               | ns    | _    | 15   |

| Rise Time                                                                             | $I_{\rm C}$ = -500 mA dc; $I_{\rm B1}$ = -50 mA dc                                      | tr               | ns    | _    | 25   |

| Storage Time                                                                          | $I_{\rm C}$ = -500 mA dc; $I_{\rm B1}$ = -50 mA dc                                      | ts               | ns    | _    | 175  |

| Fall Time                                                                             | $I_{\rm C}$ = -500 mA dc; $I_{\rm B1}$ = -50 mA dc                                      | tf               | ns    | _    | 35   |

# **PNP Silicon Transistor**

Rev. V2

# Absolute Maximum Ratings ( $T_A = +25^{\circ}C$ unless otherwise specified)

| Ratings                                                                                              | Symbol            | Value                                                   |

|------------------------------------------------------------------------------------------------------|-------------------|---------------------------------------------------------|

| Collector - Emitter Voltage                                                                          | V <sub>CEO</sub>  | -80 V dc                                                |

| Collector - Base Voltage                                                                             | V <sub>CBO</sub>  | -80 V dc                                                |

| Emitter - Base Voltage                                                                               | V <sub>EBO</sub>  | -5.0 V dc                                               |

| Collector Current                                                                                    | I <sub>C</sub>    | -1.0 A dc                                               |

| Total Power Dissipation $T_{A} = +25^{\circ}C^{(1)(2)}$ $2N4033$ $2N4029$ $2N4033UA$ $2N4033UB$      | P <sub>T</sub>    | 0.800 W<br>0.500 W<br>0.500 W<br>0.500 W <sup>(4)</sup> |

| Total Power Dissipation $T_{C} = +25^{\circ}C^{(1)(2)}$ $2N4033$ $2N4029$ $2N4033UA$ $2N4033UB$      | P <sub>T</sub>    | 4 W<br>1 W<br>N/A<br>N/A                                |

| Total Power Dissipation $T_{SP(IS)} = +25^{\circ}C^{(1)(2)}$ $2N4033$ $2N4029$ $2N4033UA$ $2N4033UB$ | P <sub>T</sub>    | N/A<br>N/A<br>1.5 W<br>1.5 W                            |

| Junction & Storage Temperature Range                                                                 | $T_J$ , $T_{STG}$ | -65°C to +200°C                                         |

## **PNP Silicon Transistor**

Rev. V2

# Absolute Maximum Ratings (T<sub>A</sub> = +25°C unless otherwise specified)

| Ratings                                                                                                      | Symbol                | Value                                        |

|--------------------------------------------------------------------------------------------------------------|-----------------------|----------------------------------------------|

| Thermal Resistance, Junction to Ambient <sup>(2) (3)</sup> 2N4033 2N4029 2N4033UA 2N4033UB                   | $R_{	heta JA}$        | 195 °C/W<br>325 °C/W<br>325 °C/W<br>325 °C/W |

| Thermal Resistance, Junction to Case (2) (3)<br>2N4033<br>2N4029<br>2N4033UA<br>2N4033UB                     | $R_{	heta JC}$        | 40 °C/W<br>150 °C/W<br>N/A<br>N/A            |

| Thermal Resistance, Junction to Case Kovar <sup>(2) (3)</sup> 2N4033 2N4029 2N4033UA 2N4033UB                | $R_{	heta JC}$        | 35 °C/W<br>N/A<br>N/A<br>N/A                 |

| Thermal Resistance, Junction to Solder Pad, Infinite Sink <sup>(2) (3)</sup> 2N4033 2N4029 2N4033UA 2N4033UB | $R_{\theta JSP(IS)}$  | N/A<br>N/A<br>110 °C/W<br>90 °C/W            |

| Thermal Resistance, Junction to Solder Pad, Ambient <sup>(2) (3)</sup> 2N4033 2N4029 2N4033UA 2N4033UB       | R <sub>0JSP(AM)</sub> | N/A<br>N/A<br>40 °C/W<br>N/A                 |

<sup>(1)</sup> For derating, for encapsulated devices, see figures 7, 8, 9, 10 and 11 of MIL-PRF-19500/512

<sup>(2)</sup> See paragraph 3.3 of MIL-PRF-19500/512

<sup>(3)</sup> For thermal impedance curves, see figures 12, 13, 13a, 14, 15, 16, 17 and 18 of MIL-PRF-19500/512

<sup>(4)</sup> For non-thermal conductive PCB or unknown PCB surface mount conditions in free air, substitute figures 8 and 16 for the UB package and use R<sub>0JA</sub>

Rev. V2

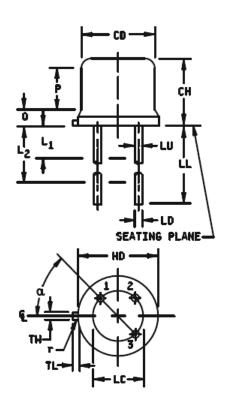

#### **Outline Drawing (TO-18)**

|                |         | Dimer | nsions  |       |          |

|----------------|---------|-------|---------|-------|----------|

| Symbol         | Incl    | nes   | Millim  | eters | Notes    |

|                | Min     | Max   | Min     | Max   |          |

| CD             | .178    | .195  | 4.52    | 4.95  |          |

| СН             | .170    | .210  | 4.32    | 5.33  |          |

| HD             | .209    | .230  | 5.31    | 5.84  |          |

| LC             | .100 TP |       | 2.54 TP |       | 6        |

| LD             | .016    | .021  | 0.41    | 0.53  | 7, 8     |

| LL             | .500    | .750  | 12.70   | 19.05 | 7, 8, 12 |

| LU             | .016    | .019  | 0.41    | 0.48  | 7, 8     |

| L <sub>1</sub> |         | .050  |         | 1.27  | 7.8      |

| L <sub>2</sub> | .250    |       | 6.35    |       | 7, 8     |

| Q              |         | .040  |         | 1.02  | 5        |

| TL             | .028    | .048  | 0.71    | 1.22  | 3, 4     |

| TW             | .036    | .046  | 0.91    | 1.17  | 3        |

| R              |         | .010  |         | 0.25  | 10       |

| Р              | .100    |       | 2.54    |       |          |

| α              | 45°TP   |       | 459     | TP    | 6        |

- 1. Dimensions are in inches.

- 2. Millimeters equivalents are given for general information only.

- Beyond r (radius) maximum, TW shall be held for a minimum length of .011 (0.28 mm).

- Dimension TL measured from maximum HD.

- Body contour optional within zone defined by HD, CD, and Q.

- Leads at gauge plane .054 +.001 -.000 inch (1.37 +0.03 –0.00 mm) below seating plane shall be within .007 inch (0.18 mm) radius of true position (TP) at maximum material condition (MMC) relative to tab at MMC. The device may be measured by direct methods.

- Dimension LU applies between L1 and L2. Dimension LD applies between L2 and minimum. Diameter is uncontrolled in L1 and beyond LL minimum.

- 8. All three leads.

- 9. The collector shall be internally connected to the case.

- Dimension r (radius) applies to both inside comers of tab.

- In accordance with ASME Y14.5M, diameters are equivalent to φx symbology.

- For "L" suffix devices, dimension LL is 1.50 (38.10 mm) minimum, 1.75 (44.45 mm) maximum.

FIGURE 1. Physical dimensions (type 2N4029) (TO-18).

Rev. V2

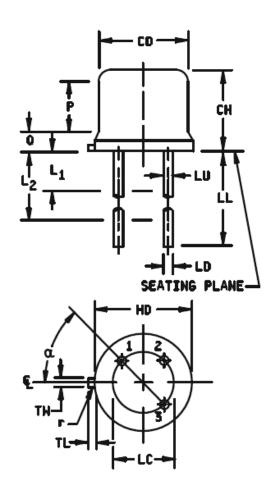

#### Outline Drawing (TO-39)

|                |         | Dime | nsions  |        |          |

|----------------|---------|------|---------|--------|----------|

| Symbol         | Inc     | hes  | Millir  | neters | Notes    |

|                | Min     | Max  | Min Max |        |          |

| CD             | .305    | .335 | 7.75    | 8.51   |          |

| СН             | .240    | .260 | 6.10    | 6.60   |          |

| HD             | .335    | .370 | 8.51    | 9.40   |          |

| LC             | .200 TP |      | 5.08 TP |        | 6        |

| LD             | .016    | .021 | 0.41    | 0.53   | 7, 8     |

| LL             | .500    | .750 | 12.70   | 19.05  | 7, 8, 12 |

| LU             | .016    | .019 | 0.41    | 0.48   | 7, 8     |

| L <sub>1</sub> |         | .050 |         | 1.27   | 7, 8     |

| L <sub>2</sub> | .250    |      | 6.35    |        | 7, 8     |

| Q              |         | .050 |         | 1.27   | 5        |

| TL             | .029    | .045 | 0.74    | 1.14   | 3, 4     |

| TW             | .028    | .034 | 0.71    | 0.86   | 3        |

| R              |         | .010 |         | 0.25   | 10       |

| Р              | .100    |      | 2.54    |        |          |

| α              | 45°TP   |      | 45      | °TP    | 6        |

- 1. Dimensions are in inches.

- 2. Millimeters equivalents are given for general information only.

- 3. Beyond r (radius) maximum, TW shall be held for a minimum length of .011 (0.28 mm).

- 4. Dimension TL measured from maximum HD.

- 5. Body contour optional within zone defined by HD, CD, and Q.

- Leads at gauge plane .054 +.001 -.000 inch (1.37 +0.03 -0.00 mm) below seating plane shall be within .007 inch (0.18 mm) radius of true position (TP) at maximum material condition (MMC) relative to tab at MMC. The device may be measured by direct methods.

- Dimension LU applies between L1 and L2. Dimension LD applies between L2 and minimum. Diameter is uncontrolled in L1 and beyond LL minimum.

- 8. All three leads

- 9. The collector shall be internally connected to the case.

- 10. Dimension r (radius) applies to both inside comers of tab.

- 11. In accordance with ASME Y14.5M, diameters are equivalent to φx symbology.

- For "L" suffix devices, dimension LL is 1.50 (38.10 mm) minimum, 1.75 (44.45 mm) maximum.

FIGURE 2. Physical dimensions (type 2N4033) (TO-39).

Rev. V2

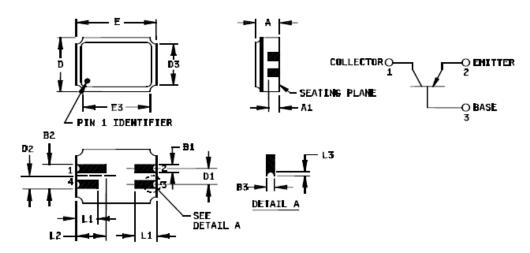

### **Outline Drawing (UA Package)**

|                |      | Dime | nsions |          |       |                | Dimensions |      |        |       |       |

|----------------|------|------|--------|----------|-------|----------------|------------|------|--------|-------|-------|

| Ltr            | Inc  | hes  | Millin | neters   | Notes | Ltr            | Inc        | hes  | Millir | meter | Notes |

|                | Min  | Max  | Min    | Max      | ]     |                | Min        | Max  | Min    | Max   | ]     |

| Α              | .061 | .075 | 1.55   | 1.91     | 3     | D <sub>2</sub> | .0375      | BSC  | 0.952  | BSC   |       |

| A <sub>1</sub> | .029 | .041 | 0.74   | 1.04     |       | D <sub>3</sub> |            | .155 |        | 3.94  |       |

| B <sub>1</sub> | .022 | .028 | 0.56   | 0.71     |       | E              | .215       | .225 | 5.46   | 5.72  |       |

| B <sub>2</sub> | .075 | REF  | 1.91   | 1.91 REF |       | E <sub>3</sub> |            | .225 |        | 5.72  |       |

| Вз             | .006 | .022 | 0.15   | 0.56     | 5     | L1             | .032       | .048 | 0.81   | 1.22  |       |

| D              | .145 | .155 | 3.68   | 3.9      |       | L2             | .072       | .088 | 1.83   | 2.24  |       |

| D <sub>1</sub> | .045 | .055 | 1.14   | 1.39     |       | L <sub>3</sub> | .003       |      | 0.08   |       | 5     |

- Dimensions are in inches.

- 2. Millimeters equivalents are given for general information only.

- Dimension "A" controls the overall package thickness. When a window lid is used, dimension "A" must increase by a minimum of .010 inch (0.254 mm) and a maximum of .040 inch (1.020 mm).

- The corner shape (square, notch, radius, etc.) may vary at the manufacturer's option, from that shown on the drawing.

- 5. Dimensions "B3" minimum and "L3" minimum and the appropriately castellation length define an unobstructed three-dimensional space traversing all of the ceramic layers in which a castellation was designed. (Castellations are required on bottom two layers, optional on top ceramic layer.) Dimension "B3" maximum define the maximum width and depth of the castellation at any point on its surface. Measurement of these dimensions may be made prior to solder dipping.

FIGURE 3. Physical dimensions, surface mount (UA version).

Rev. V2

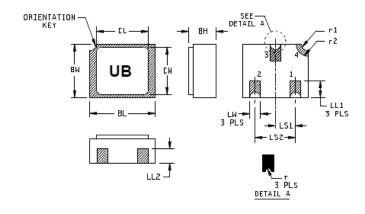

## **Outline Drawing (UB Package)**

| Symbol |      | Note |        |        |  |

|--------|------|------|--------|--------|--|

|        | Inc  | hes  | Millin | neters |  |

|        | Min  | Max  | Min    | Max    |  |

| BH     | .046 | .056 | 1.17   | 1.42   |  |

| BL     | .115 | .128 | 2.92   | 3.25   |  |

| BW     | .085 | .108 | 2.16   | 2.74   |  |

| CL     |      | .128 |        | 3.25   |  |

| CW     |      | .108 |        | 2.74   |  |

| LL1    | .022 | .038 | 0.56   | 0.97   |  |

| LL2    | .017 | .035 | 0.43   | 0.89   |  |

| Symbol          |                    | Note |      |      |  |

|-----------------|--------------------|------|------|------|--|

|                 | Inches Millimeters |      |      |      |  |

|                 | Min Max Min M      |      | Max  |      |  |

| LS <sub>1</sub> | .036               | .040 | 0.91 | 1.02 |  |

| LS <sub>2</sub> | .071 .079          |      | 1.80 | 2.01 |  |

| LW              | .016               | .024 | 0.41 | 0.61 |  |

| Г               |                    | .008 |      | .203 |  |

| r1              |                    | .012 |      | .305 |  |

| r2              | .022               |      |      | .559 |  |

|                 |                    |      |      |      |  |

- 1. Dimensions are in inches.

- 2. Millimeters are given for general information only.

- 3. Hatched areas on package denote metallized areas

- Pad 1 = Base, Pad 2 = Emitter, Pad 3 = Collector, Pad 4 = Shielding connected to the lid.

- In accordance with ASME Y14.5M, diameters are equivalent to φx symbology.

FIGURE 4. Physical dimensions, surface mount (UB version).

Rev. V2

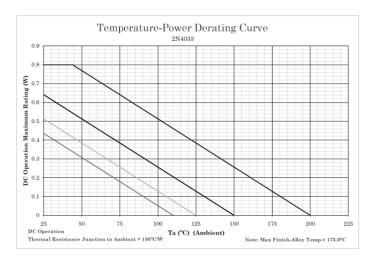

### **Temperature-Power Derating Curves**

- This is the true inverse of the worst case thermal resistance value. All devices are capable of operating at ≤ T<sub>J</sub> specified on this curve. Any parallel line to this curve will intersect the appropriate power for the desired maximum T<sub>J</sub> allowed.

- Derate design curve constrained by the maximum junction temperature ( $T_J \le 200^{\circ}C$ ) and power rating specified. (See 1.3 herein.) Derate design curve chosen at  $T_J \le 150^{\circ}C$ , where the maximum temperature of electrical test is

- performed. Derate design curves chosen at T<sub>J</sub> ≤, 125°C, and 110°C to show power rating where most users want to limit T<sub>J</sub> in their application.

FIGURE 7. Derating for 2N4033 (R<sub>0JA</sub>) (TO-39).

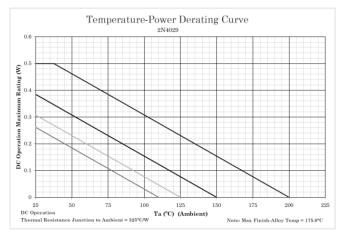

- This is the true inverse of the worst case thermal resistance value. All devices are capable of operating at ≤ T<sub>J</sub> specified on this curve. Any parallel line to this curve will intersect the appropriate power for the desired maximum T<sub>J</sub> allowed.

- Derate design curve constrained by the maximum junction temperature (T<sub>J</sub> ≤ 200°C) and power rating specified. (See 1.3 herein.)

Derate design curve chosen at T<sub>J</sub> ≤ 150°C, where the maximum temperature of electrical test is

- Deriate design curves chosen at Ty ≤ 125°C, and 110°C to show power rating where most users want to

FIGURE 8. Derating for 2N4029 (R<sub>0JA</sub>) (TO-18), leads .125 inch (3.17 mm).

Rev. V2

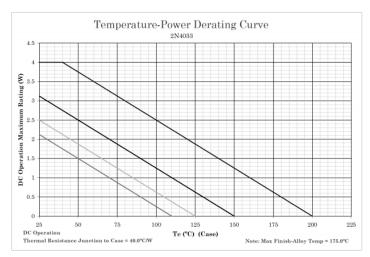

#### **Temperature-Power Derating Curves**

#### NOTES:

- This is the true inverse of the worst case thermal resistance value. All devices are capable of operating

at ≤ T<sub>J</sub> specified on this curve. Any parallel line to this curve will intersect the appropriate power for the desired maximum T<sub>.I</sub> allowed.

- Derate design curve constrained by the maximum junction temperature (T<sub>J</sub> ≤ 200°C) and power rating specified. (See 1.3 herein.)

- Derate design curve chosen at T<sub>J</sub> ≤ 150°C, where the maximum temperature of electrical test is

- performed.

Derate design curve chosen at  $T_J \le 125^{\circ}C$ , and  $110^{\circ}C$  to show power rating where most users want to limit  $T_J$  in their application.

FIGURE 9. Derating for 2N4033 (R<sub>0JC</sub>) (TO-39).

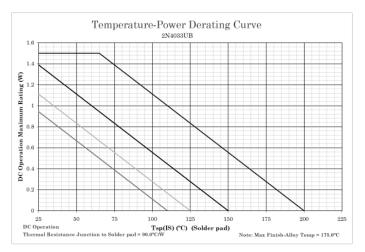

- This is the true inverse of the worst case thermal resistance value. All devices are capable of operating at ≤ T<sub>J</sub> specified on this curve. Any parallel line to this curve will intersect the appropriate power for the desired maximum T<sub>J</sub> allowed.

- Derate design curve constrained by the maximum junction temperature (T<sub>J</sub> ≤ 200°C) and power rating specified. (See 1.3 herein.)

- 3. Derate design curve chosen at  $T_J \le 150$  °C, where the maximum temperature of electrical test is

- performed.

Derate design curve chosen at T<sub>J</sub> ≤ 125°C, and 110°C to show power rating where most users want to limit T<sub>J</sub> in their application.

FIGURE 10. Derating for 2N4033UB (R<sub>BUSP(IS)</sub>), infinite sink 3-points.

Rev. V2

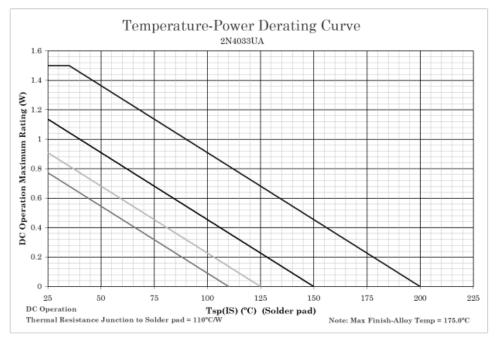

### **Temperature-Power Derating Curves**

- This is the true inverse of the worst case thermal resistance value. All devices are capable of operating

at ≤ T<sub>J</sub> specified on this curve. Any parallel line to this curve will intersect the appropriate power for the

desired maximum T<sub>J</sub> allowed.

- Derate design curve constrained by the maximum junction temperature (T<sub>J</sub> ≤ 200°C) and power rating specified. (See 1.3 herein.)

- Derate design curve chosen at T<sub>J</sub> ≤ 150°C, where the maximum temperature of electrical test is performed.

- Derate design curve chosen at T<sub>J</sub> ≤ 125°C, and 110°C to show power rating where most users want to limit T<sub>J</sub> in their application.

FIGURE 11. Derating for 2N4033UA (Rouse(IS)).

Rev. V2

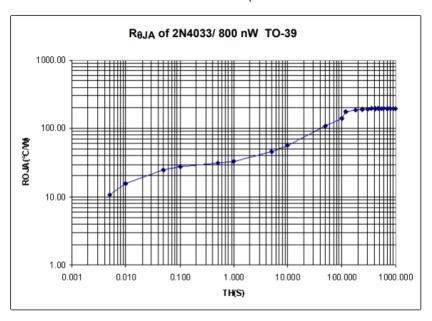

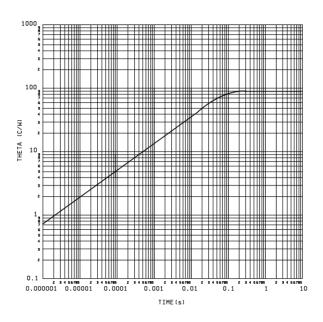

# **Thermal Impedance Curves**

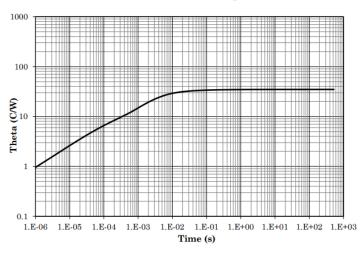

#### Maximum Thermal Impedance

FIGURE 12. Thermal impedance graph (R<sub>BJA</sub>) for 2N4033 (TO-39).

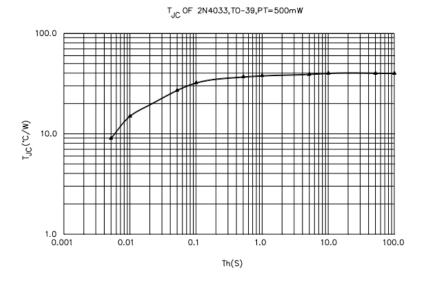

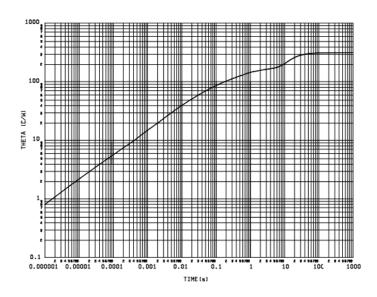

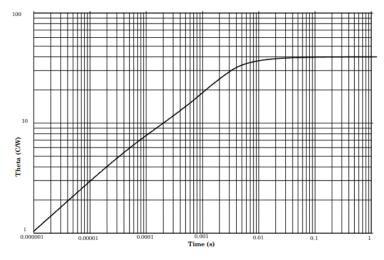

Maximum Thermal Impedance

FIGURE 13. Thermal impedance graph (R<sub>NC</sub>) for 2N4033 (TO-39)

Rev. V2

# **Thermal Impedance Curves**

#### **Maximum Thermal Impedance**

\* FIGURE 13a. Thermal impedance graph (R<sub>0JC</sub>) for Kovar 2N4033 (TO-39).

#### Maximum Thermal Impedance

FIGURE 14. Thermal impedance graph (R<sub>BJA</sub>) for 2N4029 (TO-18)

Rev. V2

# **Thermal Impedance Curves**

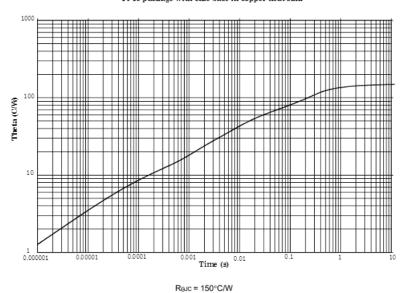

#### Maximum Thermal Impedance T0-18 package with case base in copper heat sink

FIGURE 15. Thermal impedance graph (R<sub>BJC</sub>) for 2N4029 (TO-18).

#### Maximum Thermal Impedance

FIGURE 16. Thermal impedance graph (R<sub>BJSP(IS)</sub>) for 2N4033 (UA).

Rev. V2

# **Thermal Impedance Curves**

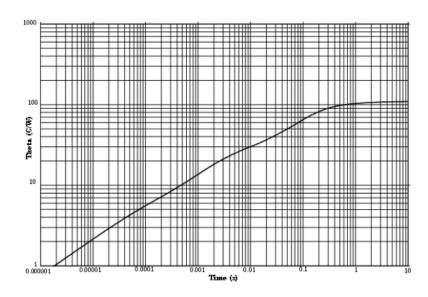

Ceramic UB package soldered to PCB 3 points solder pad (infinite sink to PCB).  $R_{\text{RJSP(IS)}} = 90^{\circ}\text{C/W}$

FIGURE 17. Thermal impedance graph (R<sub>BJSP(IS)</sub>) for 2N4029 (UB).

#### **Maximum Thermal Impedance**

2N4033UA 4 point solder pad (adhesive mount to PCB), ReJSP(AM) = 40°C/W

FIGURE 18. Thermal impedance graph Reusp(AM) for 2N4033UA.

#### **PNP Silicon Transistor**

Rev. V2

#### VPT COMPONENTS. ALL RIGHTS RESERVED.

Information in this document is provided in connection with VPT Components products. These materials are provided by VPT Components as a service to its customers and may be used for informational purposes only. Except as provided in VPT Components Terms and Conditions of Sale for such products or in any separate agreement related to this document, VPT Components assumes no liability whatsoever. VPT Components assumes no responsibility for errors or omissions in these materials. VPT Components may make changes to specifications and product descriptions at any time, without notice. VPT Components makes no commitment to update the information and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to its specifications and product descriptions. No license, express or implied, by estoppels or otherwise, to any intellectual property rights is granted by this document.

THESE MATERIALS ARE PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, RELATING TO SALE AND/OR USE OF VPT COMPONENTS PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, CONSEQUENTIAL OR INCIDENTAL DAMAGES, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. VPT COMPONENTS FURTHER DOES NOT WARRANT THE ACCURACY OR COMPLETENESS OF THE INFORMATION, TEXT, GRAPHICS OR OTHER ITEMS CON-TAINED WITHIN THESE MATERIALS. VPT COMPONENTS SHALL NOT BE LIABLE FOR ANY SPECIAL, IN-DIRECT, INCIDENTAL, OR CONSEQUENTIAL DAMAGES, INCLUDING WITHOUT LIMITATION, LOST REVE-NUES OR LOST PROFITS, WHICH MAY RESULT FROM THE USE OF THESE MATERIALS.

VPT Components products are not intended for use in medical, lifesaving or life sustaining applications. VPT Components customers using or selling VPT Components products for use in such applications do so at their own risk and agree to fully indemnify VPT Components for any damages resulting from such improper use or sale.