### **Description:**

The 2N6547 transistor is designed for high-voltage, high-speed, power switching in inductive circuits where fall time is critical. They are particularly suited for 115 and 220V line operated switch-mode applications.

#### Features:

High temperature performance specified for:

Reversed biased SOA with inductive loads.

Switching time with inductive loads.

Saturation voltages.

Leakage currents.

## **Applications:**

Switching regulators.

PWM inverters and motor controls.

Solenoid and relay drivers.

Deflection circuits.

### **Maximum Ratings**

| Rating                                                                                   | Symbol                            | Value           | Unit      |  |

|------------------------------------------------------------------------------------------|-----------------------------------|-----------------|-----------|--|

| Collector-Emitter Voltage                                                                | V <sub>CEO (SUS)</sub>            | 400             |           |  |

| Collector-Emitter Voltage                                                                | V <sub>CEX (SUS)</sub>            | 450 V DC        |           |  |

| Collector-Emitter Voltage                                                                | V <sub>CEV</sub>                  |                 |           |  |

| Emitter-Base Voltage                                                                     | V <sub>EB</sub>                   | 9               |           |  |

| Collector Current - Continuous - Peak                                                    | I <sub>C</sub>                    | 15<br>30        |           |  |

| Base Current - Continuous<br>- Peak                                                      | I <sub>B</sub>                    | 10<br>20        | A DC      |  |

| Emitter Current - Continuous<br>- Peak                                                   | I <sub>E</sub><br>I <sub>EM</sub> | 25<br>35        |           |  |

| Total Power Dissipation at $T_C = 25^{\circ}C$ at $T_C = 100^{\circ}C$ Derate above 25°C | P <sub>D</sub>                    | 175<br>100<br>1 | W<br>W/°C |  |

| Operating and Storage Junction Temperature Range                                         | $T_JT_stg$                        | -65 to +200     | °C        |  |

#### **Thermal Characteristics**

| Characteristics                                                           | Symbol          | Max. | Unit |

|---------------------------------------------------------------------------|-----------------|------|------|

| Thermal Resistance Junction to Case                                       | $R_{\theta JC}$ | 1    | °C/W |

| Max. Lead Temperature for Soldering Purposes 1/8" from Case for 5 Seconds | TL              | 275  | °C   |

www.element14.com www.farnell.com www.newark.com

## Electrical Characteristics (TC = 25°C unless otherwise noted)

| Characteristic                                                                                                                                                        | Symbol                  | Min.       | Max.            | Unit  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------|-----------------|-------|--|

| Off Characteristics (1)                                                                                                                                               | Off Characteristics (1) |            |                 |       |  |

| Collector-Emitter Sustaining Voltage $(I_C = 100 \text{mA}, I_B = 0)$                                                                                                 | V <sub>EO (sus)</sub>   | 400        | -               |       |  |

| Collector-Emitter Sustaining Voltage ( $I_C$ = 8A, $V_{clamp}$ = Rated $V_{CEX}$ , $T_C$ = 100°C) ( $I_C$ = 15A, $V_{clamp}$ = Rated $V_{CEO}$ = 100V, $T_C$ = 100°C) | V <sub>CEX (sus)</sub>  | 450<br>300 | -               | V DC  |  |

| Collector Cut off Current $(V_{CEV} = Rated \ Value, \ V_{BE \ (off)} = 1.5V \ DC)$ $(V_{CEV} = Rated \ Value, \ V_{BE \ (off)} = 1.5V \ DC, \ T_C = 100^{\circ}C)$   | I <sub>CEV</sub>        | -          | 1<br>4          |       |  |

| Collector Cut off Current $(V_{CE} = Rated V_{CEV}, R_{BE}, = 50\Omega, T_C = 100^{\circ}C)$                                                                          | I <sub>CER</sub>        | -          | 5               | mA DC |  |

| Emitter Cut off Current $(V_{EB} = 9V DC, I_C = 0)$                                                                                                                   | I <sub>ERO</sub>        | 1          | 1               | 1     |  |

| Second Breakdown                                                                                                                                                      |                         |            |                 |       |  |

| Second Breakdown Collector Current with Base Forward Biased t = 1s (Non-repetitive) ( $V_{CE}$ = 100V DC)                                                             | I <sub>S/b</sub>        | 0.2        | 1               | A DC  |  |

| On Characteristic (1)                                                                                                                                                 |                         |            |                 |       |  |

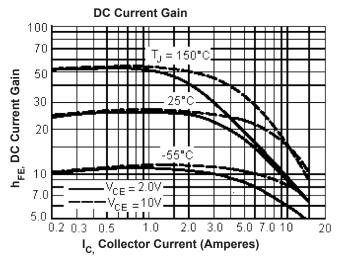

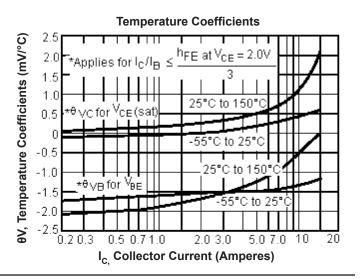

| DC Current Gain ( $I_C = 5A$ DC, $V_{CE} = 2V$ DC) ( $I_C = 10A$ DC, $V_{CE} = 2V$ DC)                                                                                | h <sub>FE</sub>         | 12<br>6    | 60<br>30        | -     |  |

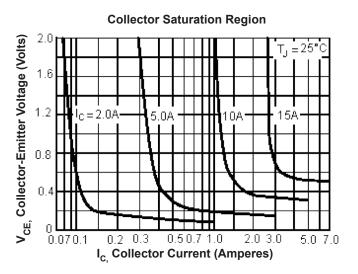

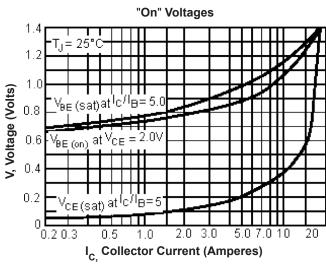

| Collector-Emitter Saturation Voltage ( $I_C = 10A$ DC, $I_B = 2A$ DC) ( $I_C = 15A$ DC, $I_B = 3A$ DC) ( $I_C = 10A$ DC, $I_B = 2A$ DC, $I_C = 100$ °C)               | V <sub>CE (sat)</sub>   | -          | 1.5<br>5<br>2.5 | V DC  |  |

| Base-Emitter Saturation Voltage ( $I_C = 10A DC$ , $I_B = 2A DC$ ) ( $I_C = 10A DC$ , $I_B = 2A DC$ , $T_C = 100^{\circ}C$                                            | V <sub>BE (sat)</sub>   | -          | 1.6             |       |  |

| Dynamic Characteristics                                                                                                                                               |                         |            |                 |       |  |

| Current-Gain-Bandwidth Product ( $I_C$ = 500mA DC, $V_{CE}$ = 10V DC, $f_{test}$ = 1MHz)                                                                              | f <sub>⊤</sub>          | 6          | 28              | MHz   |  |

| Output Capacitance $(V_{CB} = 10V DC, I_E = 0, f_{test} = 1MHz)$                                                                                                      | C <sub>ob</sub>         | 125        | 500             | pF    |  |

Indicates JEDEC Registered Data.

(1) Pulse Test: Pulse Width = 300µs, Duty Cycle = 2%.

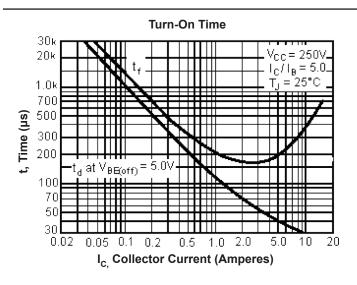

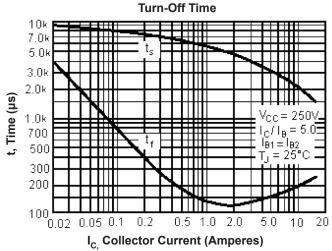

## **Switching Characteristics**

| Resistive Load          |                                                                                                     |                |       |         |      |

|-------------------------|-----------------------------------------------------------------------------------------------------|----------------|-------|---------|------|

| Delay Time              |                                                                                                     | t <sub>d</sub> | -     | 0.05    |      |

| Rise Time               | $(V_{CC} = 250V, I_C = 10A,$                                                                        | t <sub>r</sub> | -     | 1       |      |

| Storage Time            | l <sub>B1</sub> = l <sub>B2</sub> = 2A, t <sub>p</sub> = 100μS,<br>Duty Cycle ≤2%                   | t <sub>s</sub> | -     | 4       | μs   |

| Fall Time               |                                                                                                     | t <sub>f</sub> | -     | 0.7     |      |

| Inductive Load, Clamped |                                                                                                     |                |       |         |      |

| Storage Time            | $(I_C = 10A (pk), V_{clamp} = Rated V_{CEX}, I_{B1} = 2A, V_{BE (off)} = 5V DC, T_C = 100°C)$       | t <sub>s</sub> | -     | 5       |      |

| Fall Time               |                                                                                                     | t <sub>f</sub> | -     | 1.5     | μs   |

| Storage Time            | $(I_C = 10A (pk), V_{clamp} = Rated V_{CEX}, I_{B1} = 2A, V_{BE (off)} = 5V DC, T_C = 25^{\circ}C)$ | t <sub>s</sub> | Тур   | ical 2  | II.6 |

| Fall Time               |                                                                                                     | t <sub>f</sub> | Typic | al 0.09 | μs   |

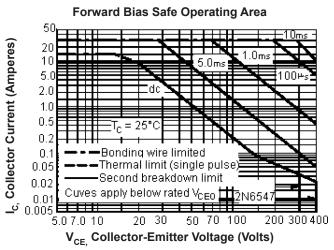

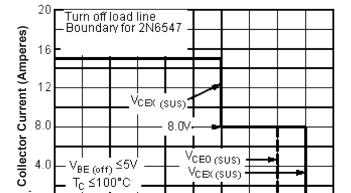

# **Typical Electrical Characteristics**

www.element14.com www.farnell.com www.newark.com

**Reverse Bias Safe Operating Area**

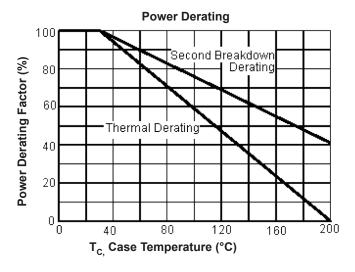

There are two limitations on the power handling ability of a transistor: average junction temperature and second breakdown. Safe operating area curves indicate  $\rm I_C - \rm V_{CE}$  limits of the transistor that must be observed for reliable operation; i.e., the transistor must not be subjected to greater dissipation than the curves indicate.

200

V<sub>CE.</sub> Collector-Emitter Voltage (Volts)

300

The data is based on  $T_C = 25^{\circ}C$ ;  $T_{J(pk)}$  is variable depending on power level. Second breakdown pulse limits are valid for duty cycles to 10% but must be derated when  $T_C \ge 25^{\circ}C$ . Second breakdown limitations do not derate the same as thermal limitations. Allowable current at the voltages shown may be found at any case temperature by using the appropriate curve.  $T_{J(pk)}$  may be calculated from the data. At high case temperatures, thermal limitations will reduce the power that can be handled to values less than the limitations imposed by second breakdown.

www.element14.com www.farnell.com www.newark.com

0

100

500

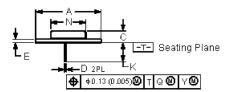

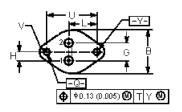

#### **Dimensions**

#### TO-204 (TO-3)

| Dim. | Min.                    | Max.         |  |

|------|-------------------------|--------------|--|

| Α    | 1.55 (39.37) Reference  |              |  |

| В    | -                       | 1.05 (26.67) |  |

| С    | 0.25 (6.35)             | 0.335 (8.51) |  |

| D    | 0.038 (0.97)            | 0.043 (1.09) |  |

| Е    | 0.055 (1.4)             | 0.07 (1.77)  |  |

| G    | 0.43 (10.92) BSC        |              |  |

| Н    | 0.215 (5.46) BSC        |              |  |

| K    | 0.44 (11.18) 0.48 (12.1 |              |  |

| L    | 0.665 (16.89) BSC       |              |  |

| N    | -                       | 0.83 (21.08) |  |

| Q    | 0.151 (3.84)            | 0.165 (4.19) |  |

| U    | 1.187 (30.15) BSC       |              |  |

| V    | 0.131 (3.33)            | 0.188 (4.77) |  |

Dimensions: Inches (Millimetres)

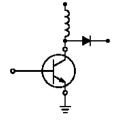

### **Pin Configuration**

Pin 1. Base

2. Emitter Collector (Case)

### **Part Number Table**

| Description           | Part Number |  |

|-----------------------|-------------|--|

| Transistor, NPN, TO-3 | 2N6547      |  |

Important Notice: This data sheet and its contents (the "Information") belong to the members of the Premier Farnell group of companies (the "Group") or are licensed to it. No licence is granted for the use of it other than for information purposes in connection with the products to which it relates. No licence of any intellectual property rights is granted. The Information is subject to change without notice and replaces all data sheets previously supplied. The Information supplied is believed to be accurate but the Group assumes no responsibility for its accuracy or completeness, any error in or omission from it or for any use made of it. Users of this data sheet should check for themselves the Information and the suitability of the products for their purpose and not make any assumptions based on information included or omitted. Liability for loss or damage resulting from any reliance on the Information or use of it (including liability resulting from negligence or where the Group was aware of the possibility of such loss or damage arising) is excluded. This will not operate to limit or restrict the Group's liability for death or personal injury resulting from its negligence. Multicomp is the registered trademark of the Group. © Premier Farnell plc 2012.

www.element14.com www.farnell.com www.newark.com