## SSI 32P4904

## PRML Read Channel with PR4, 8/9 ENDEC, FWR Servo

May 1996

#### DESCRIPTION

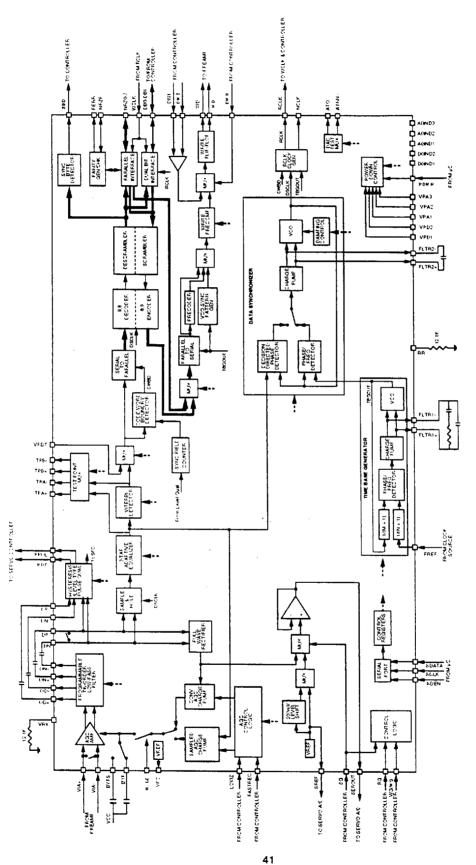

The SSI 32P4904 is a high performance BiCMOS read channel IC that provides all of the functions needed to implement an entire Partial Response Class 4 (PR4) read channel for zoned recording hard disk drive systems with data rates from 24 to 80 Mbit/s.

Functional blocks include AGC, programmable filter, adaptive transversal filter, Viterbi qualifier, 8,9 GCR ENDEC, data synchronizer, time base generator, and FWR servo.

Programmable functions such as data rate, filter cutoff, filter boost, etc. are controlled by writing to the serial port registers so no external component changes are required to change zones. The part requires a single +5V power supply.

The SSI 32P4904 utilizes an advanced BiCMOS process technology along with advanced circuit design techniques which result in high performance devices with low power consumption.

#### **FEATURES**

#### **GENERAL**

- Register programmable data rates from 24 to 80 Mbit/s

- Sampled data read channel with Viterbi qualification

- Programmable filter for PR4 equalization

- 3-tap transversal filter for adaptive PR4 equalization

- 8/9 GCR ENDEC

- Data scrambler/descrambler

- Programmable write precompensation

- Low operating power (0.75W typical at 5V)

- Register programmable power management

- Presettable precoder state

- Register programmable WG polarity

- Dual bit and byte wide bi-directional NRZ data interfaces

- Serial interface port for access to internal program storage registers

- Single power supply (5V ±10%)

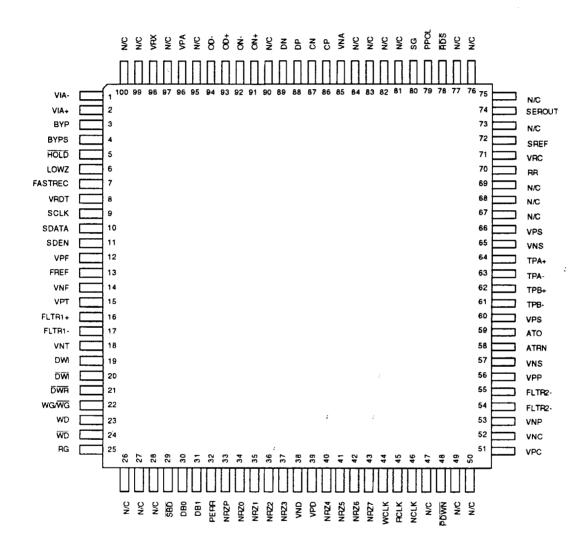

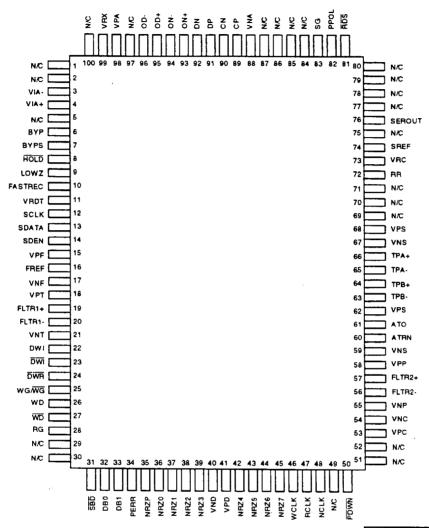

- Small footprint 100-Lead TQFP and 100-Lead QFP packages

#### **AUTOMATIC GAIN CONTROL**

- Dual mode AGC, analog during acquisition, sampled during read data

- Separate AGC level storage pins for data and servo

- Dual rate attack and decay charge pump for rapid AGC recovery

- Programmable, symmetric, charge pump currents during read data

- Charge pump currents track programmable data rate

- Low drift AGC hold circuitry

- Low-Z input switch

- AGC hold, fast recovery, and AGC input impedance control signals

- Wide bandwidth, precision full-wave rectifier

#### FILTER/EQUALIZER

- Programmable, 7-pole, continuous time filter provides:

- Channel filter and pulse slimming equalization for equalization to PR4

- Programmable cutoff frequency, 3 to 24 MHz

- Programmable boost/equalization, 0 to 12.75 dB

- $\pm 0.6$  ns group delay variation from 0.2 fc to fc, with fc = 24 MHz

- Minimizes size and power

- Low-Z input switch

1

- 3-tap self adapting transversal filter for fine equalization to PR4

- No external components required

(continued)

05/30/96 - rev.

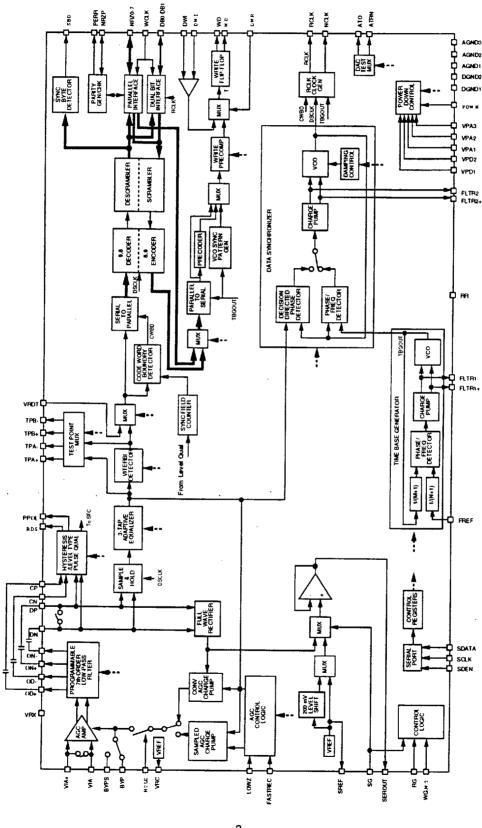

## **BLOCK DIAGRAM**

#### FEATURES (continued)

#### **PULSE QUALIFICATION**

- Sampled Viterbi qualification of signal equalized to PR4

- Register selection between dual level pulse qualifier or hysteresis qualifier for servo reads

#### TIME BASE GENERATOR

- Less than 1% frequency resolution

- Up to 90 MHz frequency output

- Independent M and N divide-by registers

- No active external components required

#### **DATA SEPARATOR**

- Fully integrated data separator includes data synchronizer and 8,9 GCR ENDEC

- Register programmable to 80 Mbit/s operation

- · Fast acquisition, sampled data phase lock loop

- Decision directed clock recovery from data samples

- Adaptive (+) and (-) clock recovery thresholds for use with asymmetrical amplitude signals (e.g. from MR heads)

- Programmable damping ratio for data synchronizer

PLL is constant for all data rates

- Data scrambler/descrambler to reduce fixed pattern effects

- Dual bit and byte wide NRZ data interfaces

- Time base tracking, programmable write precompensation

- Differential PECL write data output

- Integrated sync byte detection

## **SERVO**

- Wide bandwidth, precision full-wave rectifier

- Buffered FWR analog servo output with selectable reference voltage

- Separate, automatically selected, registers for servo fc, boost, and threshold

- Compatible with SSI 32H6521 Embedded Servo Controller

#### **FUNCTIONAL DESCRIPTION**

The SSI 32P4904 implements a complete high performance PR4 read channel, including an AGC, programmable filter/equalizer, adaptive transversal filter, Viterbi pulse qualifier, time base generator, data separator with 8,9 ENDEC and scrambler/descrambler, and FWR servo, that supports data rates up to 80 Mbit/s.

A serial port is provided to write control data to the 16 internal program storage registers.

#### **AGC CIRCUIT DESCRIPTION**

The automatic gain control (AGC) circuit is used to maintain a constant signal amplitude at the input of the pulse detector while the input to the amplifier varies. The circuit consists of a loop that includes the AGC amplifier and charge pump, the programmable continuous time filter, and the precision wide band full wave rectifier. Depending on whether the read is of servo or data type, the specific blocks utilized in the loop are slightly different. Both loop paths are fully differential to minimize susceptibility to noise.

During servo reads the loop consists of the AGC amplifier with a continuous dual rate charge pump, the programmable continuous time filter, and the precision wide band full wave rectifier. The gain of the AGC amplifier is controlled by the voltage stored on the BYPS hold capacitor (CBYPS). The dual rate charge pump drives CBYPS with currents that drive the differential voltage at DP/DN to 1.4 Vp-pd. Attack currents lower the VBYPS which reduces the amplifier gain. The dual rate attack charge pump is included for fast transient recovery. The normal AGC attack current in servo mode is 150 µA. When the signal exceeds 125% of the nominal signal level, the attack current is increased by a factor of 8. The nominal decay current is 8.3 µA, and increases by a factor of 8 when the FASTREC input is high. In this mode, transients that produce low gain will recover more rapidly with the fast decay current, while transients that produce high gain will put the circuit in the fast attack recovery mode.

#### AGC CIRCUIT DESCRIPTION (continued)

For data reads, the loop described above is used until the data synchronizer is locked to the incoming VCO preamble, except that to optimize recovery for constant density recording, both of the AGC charge pumps' currents track the data rate value loaded in the Data Rate Register and that the BYP hold capacitor (CBYP) is now used. In addition, at the maximum data rate. the nominal AGC attack current is 360 µA and the nominal decay current is 20 µA. The fast attack and fast decay current factors are the same as in servo mode. After VCO lock (SFC), the loop is switched to include the AGC amplifier with a sampled dual rate charge pump, the programmable continuous time filter. full-wave rectifier, and the sampling 3-tap adaptive equalizer. This allows more accurate control of the signal amplitude into the Viterbi qualifier. In this sampled AGC mode, a symmetrical attack and decay charge pump is used. The "1" sample amplitudes are sampled and held and compared to a threshold to generate the error current. The maximum charge pump current value can be programmed from the Sample Loop Control Register to 0, 20, 40, or 60 µA.

For maximum application flexibility, all AGC mode control inputs are designed to be externally controlled. When the LOWZ input is high, Low-Z mode is activated. In the Low-Z mode, the AGC amplifier input impedance is reduced to allow quick recovery of the AGC amplifier input AC coupling capacitors. This mode should be activated during and for a short time after a write operation.

When the HOLD input is low, the dual rate attack charge pumps are disabled. This deactivates the AGC loop. The AGC amplifier gain will be held constant at a level set by the voltage at the BYP or BYPS pins.

In most applications, the BYP and BYPS pin voltages are stored on external capacitors. In applications where AGC action is not desired, the BYP and BYPS voltages can be set by resistor divider networks connected from VPA to VRC. If programmable gain is desired, the resistor network could be driven by a current DAC.

#### PULSE QUALIFICATION CIRCUIT DESCRIPTIONS

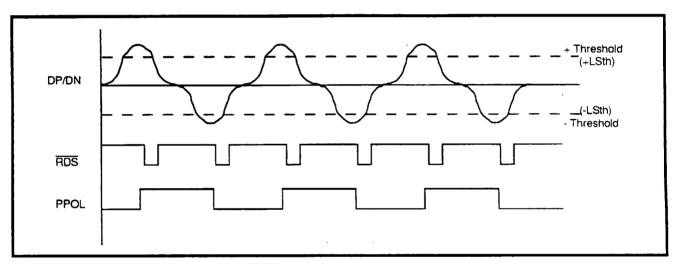

This device utilizes three different types of pulse qualification, two primarily for servo reads and the other for data reads.

## Servo Qualifiers (Dual Level/Window & Hysteresis)

During servo reads (SG high) and when bit 6 of the Control Operating Register is set to 1, a dual level/ window type of pulse qualifier is used. The level qualification thresholds are set by a 7-bit DAC which is controlled by the Servo Level Threshold Register. The register value is relative to the peak voltage at the output of the continuous time filter, and the DAC is referenced to a fixed internal reference voltage. The positive and negative thresholds are equal in magnitude. The state of the adaptive threshold level enable (ALE) bit in the WP/LT Register does not affect this DAC's reference. The RDS and the PPOL outputs of the level qualifier indicate a qualified servo pulse and the polarity of the pulse, respectively.

When bit 6 of the Control Operating Register is set to 0, a hysteresis type of pulse qualifier is used. The RDS output will recognize only alternating polarity qualified pulses. If a pulse exceeds the threshold and is of the same polarity of the previous qualified pulse, then it is ignored.

In data read mode (RG high), the same window mode qualifier is always used for ensuring pulse polarity changes during VCO sync field counting. It's qualification thresholds are set by a 7-bit DAC which is controlled by or the Data Level Threshold Register. The register value is relative to the peak voltage at output of the continuous time filter and the DAC is referenced to an fixed internal reference voltage. The positive and negative thresholds are equal in magnitude. The state of the adaptive threshold level enable (ALE) bit in the WP/LT Register does not affect the DAC's reference until the sync field count has been achieved. The RDS and the PPOL outputs of the level qualifier are not active in data read mode.

#### Viterbi Qualifier

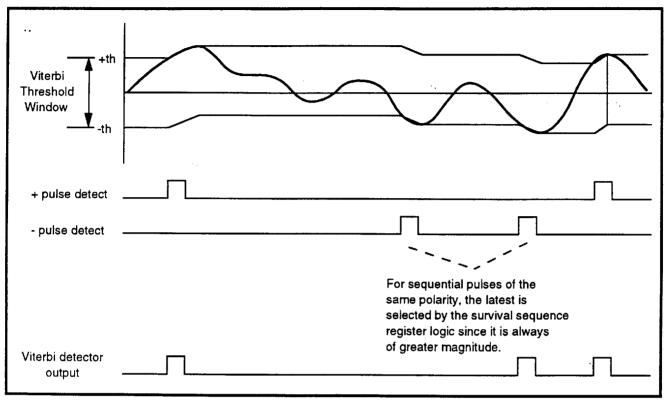

The second type of pulse qualification, the Viterbi qualifier, is only used during data read mode after the sync field count has been achieved. The Viterbi qualifier has two significant blocks, one that feeds the other. The first block is the sampled pulse detector and the second is the survival sequence register.

The sampled pulse detector performs the pulse acquisition/detection in the sampled domain. It acquires pulses by comparing the code clock sampled level of the analog waveform to the positive and negative thresholds established by the programmable Viterbi threshold window. The Viterbi threshold window is defined to be the difference between the positive and negative threshold levels. The threshold window, Vth, is set by a 7-bit DAC which is controlled by the Viterbi Detector Control Register. While the window size is fixed by the programmed Vth value, the actual positive and negative thresholds track the most positive and the most negative samples of the equalized input signal. For example, the Viterbi positive signal threshold, Vpt = Vpeak (+) max if the previous detected level was (+). If the previous detect level was (-), Vpt = Vpeak(-)max + Vth, where Vpeak(-)max is the maximum amplitude of the previously detected negative signal. Normally Vth is set to equal Vpeak (approx. 500 mV).

After the pulses have been detected they must be further qualified by the survival sequence registers and associated logic. This logic guarantees that for sequential pulses of the same polarity within the maximum run length, only the latest is qualified. By definition, this is the pulse of greatest amplitude.

The Viterbi qualifier is implemented as two parallel qualifiers that operate on interleaved samples. Each qualifier has a survival sequence register length of 5.

#### PROGRAMMABLE FILTER CIRCUIT DESCRIPTION

The on-chip, continuous time, low pass filter has register programmable cutoff and boost settings, and provides both normal and differentiated outputs. It is a 7th order filter that provides a 0.05° phase equiripple response. The group delay is relatively constant up to 1.75 times the cutoff frequency. For pulse slimming two zero programmable boost equalization is provided with no degradation to the group delay performance. The differentiated output is created by a single-pole, single-zero differentiator. Both the boost and the filter cutoff frequency are programmed through internal 7-bit DACs, accessed via the serial port logic. The nominal boost range at the cutoff frequency is 0 to 12.75 dB at maximum fc and is controlled by the Data Boost Register or the Servo Boost Register in the servo mode. The cutoff frequency, fc is variable from 3 to 24 MHz and controlled by the Data Cutoff Register or Servo Cutoff Register in the servo mode. The cutoff and boost values for servo reads are automatically switched when servo mode is entered.

The current reference for the filter DACs is set using a single 12.1 k $\Omega$  resistor, from the VRX pin to ground. The voltage at VRX is proportional-to-absolute-temperature (PTAT).

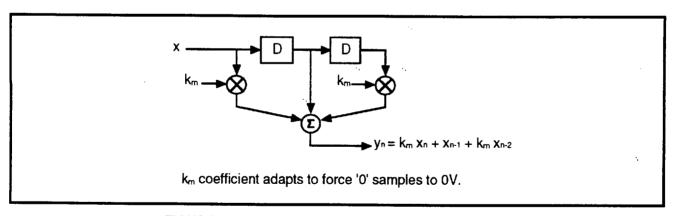

## ADAPTIVE EQUALIZER CIRCUIT DESCRIPTION

Up to 7 dB of cosine equalization for fine shaping of the incoming read signal to the PR4 waveshape is provided by a 3-tap, sampled analog, transversal filter with an adaptive multiplier coefficient. The same multiplier coefficient ( $k_m$ ) is used for both of the outside taps. The value of  $k_m$  is adjusted to force "zero" samples to zero volts. A special equalizer training pattern, located after the VCO sync field in the sector format, is used to provide an optimum signal for the equalizer to adapt to. The adaptive property of the equalizer is enabled or disabled by the AEE bit in the Sample Loop Register. If the adaptive property is enabled, whether adaptation occurs only during the training pattern or both during the training pattern and the user data is controlled by the AED bit in the Sample Loop Register.

**FIGURE 1: Viterbi Detection**

FIGURE 2: Block Diagram of 3-Tap Adaptive Equalizer

## FUNCTIONAL DESCRIPTION (continued)

#### TIME BASE GENERATOR CIRCUIT DESCRIPTION

The time base generator (TBG) is a PLL based circuit, that provides a programmable reference frequency to the data separator for constant density recording applications. This time base generator output frequency can be programmed with a better than 1% accuracy via the M, N and DR Registers. The TBG output frequency, Fout, should be programmed as close as possible to ((9/8) • NRZ Data Rate). The time base also supplies the timing reference for write precompensation so that the precompensation tracks the reference time base period.

The time base generator requires an external passive loop filter to control its PLL locking characteristics. This filter is fully-differential and balanced in order to reduce the effects of common mode noise.

In servo read, write and idle modes, the programmable time base generator is used to provide a stable reference frequency for the data separator. In the write and idle modes, the time base generator output, when selected by the Control Test Mode Register, can be monitored at the TPA+ and TPA- test pins. In the read mode, the TBG output should not be selected for output on the test pins so that the possibility of jitter in the data separator PLL is minimized.

The reference frequency is programmed using the M and N Registers of the time base generator via the serial port, and is related to the external reference clock input, FREF, as follows:

FTBG = FREF

$$[(M + 1) \div (N + 1)]$$

The M and N values should be chosen with the consideration of phase detector update rate and the external passive loop filter design. The Data Rate Register must be set to the correct VCO center frequency. The time base generator PLL responds to any changes to the M and N Registers, only after the DR Register is updated.

The DR Register value, directly affects the following:

- center frequency of the time base generator VCO

- center frequency of the data separator VCO

- phase detector gain of the time base generator phase detector

- phase detector gain of the data separator phase detector

- write precompensation

The reference current for the DR DAC is set by an external resistor, RR, connected between the ground and RR pins.

$$RR = 12.1 \text{ k}\Omega$$

Note: SSI 32P4904 must have its VCO's trimmed for 80 Mbit/s

## **DATA SEPARATOR CIRCUIT DESCRIPTION**

The data separator circuit provides complete encoding, decoding, and synchronization for 8,9 (0,4,4) GCR data. In data read mode, the circuit performs address mark detect, clock recovery, code word synchronization, decoding, sync byte detection, descrambling, and NRZ interface conversion. In the write mode, the circuit generates address marks, generates the VCO sync field, scrambles and converts the NRZ data into 8,9 (0,4,4) GCR format, precodes the data, and performs write precompensation.

The circuit consists of five major functional blocks; the data synchronizer, 8,9 ENDEC, NRZ scrambler/descrambler, NRZ interface, and write precompensation.

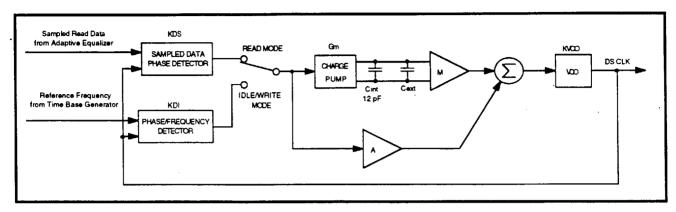

#### Data Synchronizer

The data synchronizer uses a fully integrated, fast acquisition, PLL to recover the code rate clock from the incoming read data. To achieve fast acquisition, the data synchronizer PLL uses two separate phase detectors to drive the loop. A decision-directed phase detector is used in the read mode and phase-frequency detector is used in the idle, servo, and write modes.

#### Data Synchronizer (continued)

In the read mode the decision-directed timing recovery updates the PLL by comparing amplitudes of adjacent "one" samples or comparing the "zero" sample magnitude to ground for the entire sample period. A special (non IBM) algorithm is used to prevent "hang up" during the acquisition phase. The determination of whether a sample is a "one" or a "zero" is performed by a dedicated, dual mode, threshold comparator. This comparator's threshold levels are determined by the value, Lth, programmed in the Data Threshold Register. The fixed level threshold before the sync field count (SFC) has been achieved will be 1.4 times the threshold level after SFC since this is the ratio of the peak signal to the sampled "1" signal amplitude for PR4. The dual mode nature of this comparator allows the selection of either symmetric fixed or independent self adapting (+) and (-) thresholds by programming the adaptive level enable (ALE) bit in the WP/LT Register.

The adaptive reference allows the specification of the threshold value to be a percentage of an averaged peak value. When adaptive mode is selected, the fixed thresholds are used until the sync field count (SFC) has been reached, then the adaptive levels are internally enabled. The time constant of a single-pole filter that controls the rate of adaptation, is programmable by bits TC3-1 in the WP/LT Register.

In the write and idle modes the non-harmonic phase-frequency detector is continuously enabled, thus maintaining both phase and frequency lock to the time base generator's VCO output signal, FTBG. The polarity and width of the detector's output current pulses correspond to the direction and magnitude of the phase error.

The two phase detectors' outputs are muxed into a single differential charge pump which drives the loop filter directly. The loop filter requires an external capacitor. The loop damping ratio is programmed by bits 6-0 in the Damping Ratio Control Register. The programmed damping ratio is independent of data rate.

In write mode, the TBG output is used to clock the encoder, precoder, and write precompensation circuits. The output of the precompensation circuit is then fed to the write data flip-flop which generates the write data (WD, WD) outputs.

#### **ENDEC**

The ENDEC implements an 8,9 (0,4,4) group coded recording (GCR) algorithm. The code has a minimum of no zeros between ones and a maximum of four zeros between ones for the interleaved samples. During write operations the encoder portion of the ENDEC converts 8-bit parallel, scrambled or nonscrambled, data to 9-bit parallel code words that are then converted to serial format. In data read operation, after the code word boundary has been detected in the Viterbi qualified serial data stream, the data is converted to 9-bit parallel form and the decoder portion of the ENDEC converts the 9-bit code words to 8-bit NRZ format.

#### Scrambler/Descrambler

The scrambler/descrambler circuit is provided to reduce fixed pattern effects on the channel's performance. It is enabled or disabled by bit 2 of the Control Operating Register. In write mode, if enabled, the circuit scrambles the 8-bit internal NRZ data before passing it to the encoder. Only user data, i.e., the NRZ data following the sync byte, is scrambled. In data read mode, only the decoded NRZ data after the sync byte is descrambled. The scrambler polynomial is  $H(X) = 1 \oplus X7 \oplus X10$ .

#### **NRZ** Interface

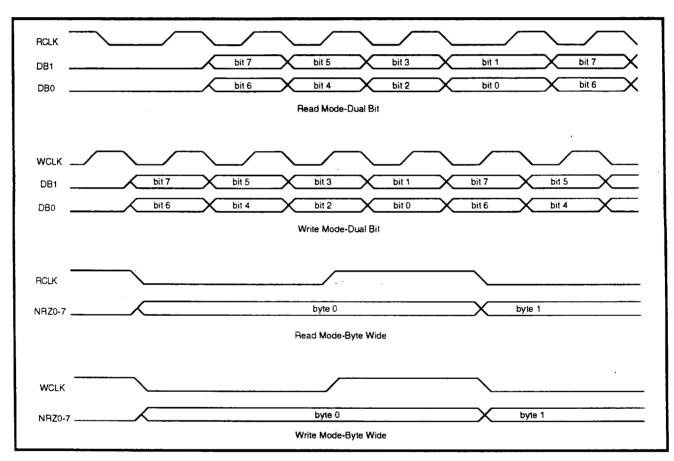

The NRZ interface circuit provides the ability to interface with either a dual bit or byte wide controller. The NRZ interface type is specified by the programming of bit 4 of the Control Operating Register. If byte wide mode is selected, the circuit does not reformat the data before passing it to and from the internal 8-bit bus. If dual-bit mode is selected, the NRZ interface circuit converts the external dual-bit bus to the internal 8-bit bus. Only the selected NRZ interface is enabled and the other can be left floating. Both the byte wide and dual bit interfaces define the most significant bit of the interface as the most significant bit of the data and the dual bit interface defines the first pair clocked in or out as the most significant pair.

FIGURE 3: Data Synchronizer Phase Locked Loop

FIGURE 4: RCLK, WCLK vs. NRZ Data

#### NRZ Interface (continued)

For both byte wide and dual bit operation, the NRZ write data is latched by the SSI 32P4904 on the rising edge of the WCLK input. The WCLK frequency must be appropriate for the data rate chosen or else overflow/underflow will occur. It is recommended that WCLK be connected to RCLK to prevent this from occurring. In byte-wide mode, as each NRZ byte is input to the SSI 32P4904, its parity is checked against the controller supplied parity bit NRZP. If an error is detected, the PERR output pin goes high and remains high until WG goes low.

In data read mode, the NRZ data will be presented to the controller near the falling edge of RCLK so that it can be latched by the controller on the rising edge of RCLK. When RG goes high, the selected NRZ interface will output low data until the sync byte has been detected. The first non-zero data presented will be the sync byte (96H). The NRZ interface is at a high impedance state when not in data read mode. In byte-wide mode, an even parity bit, NRZP, is generated for each output byte.

#### Write Precompensation

The write precompensation circuitry is provided to compensate for media bit shift caused by magnetic nonlinearities. The circuit recognizes specific write data patterns and can add delays in the time position of write data bits to counteract the magnetic nonlinearity effect. The magnitude of the time shift, WPC, is programmable via the Write Precomp Register and is made proportional to the time base generator's VCO period (i.e., data rate). The circuit performs write precompensation only on the second of two consecutive "ones" and only shifts in the late direction. If more than two consecutive "ones" are written, all but the first are precompensated in the late direction.

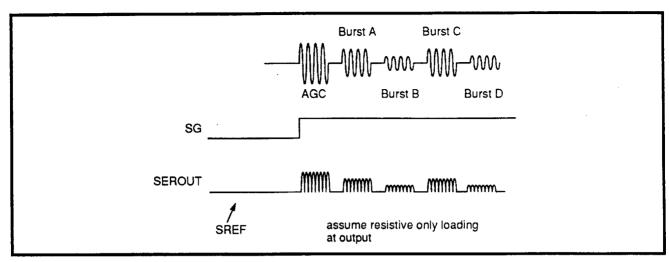

#### SERVO CIRCUIT DESCRIPTION

Embedded servo capture is provided with a buffered full-wave rectified (FWR) output. The differential signal across the DP/DN inputs is applied to a full-wave rectifier. The output signal of the rectifier is the rectified servo burst signal, level-shifted above SREF (which is a bandgap reference from VPA). The output at the SEROUT pin is selectable between the FWR output and SREF. When the SG is high (active) the FWR output is selected for the SEROUT pin. When SG is low (i.e., during the data field) then the SEROUT pin is SREF.

The dual level pulse qualifier outputs  $\overline{\text{RDS}}$  and PPOL are enabled when the servo gate input (SG) goes high and provide the indication of a qualified servo pulse and the polarity of the pulse, respectively.

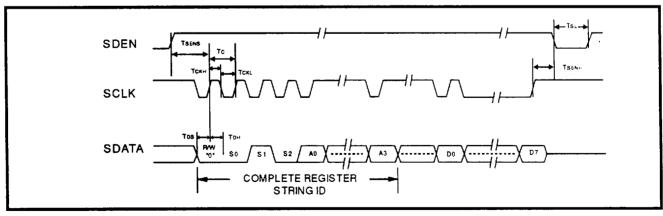

#### SERIAL PORT CIRCUIT DESCRIPTION

The serial port interface is used to program the SSI 32P4904's sixteen internal registers. The serial port is enabled for data transfer when the serial data enable (SDEN) pin is high ("1"). SDEN must be asserted high prior to any transmission and it should remain high until the completion of the transfer. At the end of each transfer SDEN should be brought low ("0").

When SDEN is high, the data presented to the serial data (SDATA) pin will be latched into the SSI 32P4904 on each rising edge of the serial clock (SCLK). Rising edges of SCLK should only occur when the desired bit of address or data is being presented on the serial data line. Serial data transmissions must occur in 16-bit packets. During a serial data transmission, if SDEN is switched low before 16 SCLK pulses are received or if more than 16 SCLK pulses are received, that serial transmission will be aborted. For all valid transmissions, the data is latched into the internal register on the falling edge of SDEN.

Each 16-bit transmission consists of a  $R/\overline{W}$  bit  $(R/\overline{W}="0")$  followed by 3 device select bits, 4 address bits and 8 data bits. The address bits select the internal register to be written to. The device select, address and data fields are input LSB first, MSB last, where LSB is defined as bit 0. The three device select bits select the device on the Silicon Systems serial bus to be communicated with and must set S0 = 0, S1 = 1, and S2 = 0 when communicating with the SSI 32P4904. Figure 7 shows the serial interface timing diagram.

FIGURE 5: Servo Function Diagram

FIGURE 6: RDS and PPOL vs. DP/DN Relationship

FIGURE 7: Serial Interface Timing

www.DataSheet4U.com

#### FUNCTIONAL DESCRIPTION (continued)

## **OPERATING MODES**

The fundamental operating modes of the SSI 32P4904 are controlled by the servo gate (SG), read gate (RG), and write gate (WG/WG) input pins. The exclusive assertion of any these inputs causes the device to enter that mode. If none of these inputs is asserted, the device is in the idle mode. If more than one of the inputs is asserted, the mode is determined by the following hierarchy: SG overrides RG which overrides WG. The mode that is overriding takes effect immediately.

RG and SG are asynchronous inputs and may be initiated or terminated at any position on the disk. WG is also an asynchronous input, but should not be terminated prior to the last output write data (WD/WD) pulse.

#### **IDLE MODE OPERATION**

If SG, RG, and WG are not active, the SSI 32P4904 is in Idle mode. When in Idle mode, the time base generator and the data separator PLL are running and the data separator PLL is phase-frequency locked to the TBG VCO output. The AGC, continuous time filter, and pulse qualifiers are active but the outputs of the pulse qualifiers are disabled. The continuous time filter is using its programmed values for cutoff frequency and boost determined by the data mode registers. The AGC operation is the same as in the VCO preamble portion of a data read.

#### **SERVO MODE OPERATION**

If SG is high, the device is in the servo mode. This mode is the same as Idle except that the filter cutoff and boost settings are switched from those programmed for data read mode to those programmed for servo mode, the AGC is switched to servo mode, and the  $\overline{\text{RDS}}$ , PPOL, and SEROUT outputs are enabled. The assertion of SG causes read mode and write mode to be overridden.

#### WRITE MODE OPERATION

The SSI 32P4904 supports three different write modes; Normal write mode, direct write mode 1 and direct write mode 2. The direct write modes require that either the direct write bit, bit 0 of the Control Operating Register, or the DWR pin be active. All three write modes require that the data separator be powered on.

#### **Normal Write Mode**

The SSI 32P4904 is in the normal write mode if WG/WG is active (register bit selectable whether active high or active low), DWR is high, and the direct write bit in the Control Operating Register is low. A minimum of one NRZ time period must elapse after RG goes low before WG/WG can be set active. The data separator PLL is phase-frequency locked to the TBG VCO output in this mode.

In normal write mode, the circuit first auto generates the VCO sync pattern, and finally scrambles the incoming NRZ data from the controller, encodes it into 8,9 GCR formatted data, precodes it, precompensates it, feeds it to a write data toggle flip-flop, and outputs it to the preamp for storage on the disk. The write data flip-flop is reset when WG/WG goes inactive to ease testing. This causes WD to be low and  $\overline{\text{WD}}$  to be high when not in write mode.

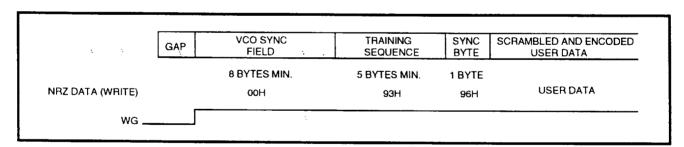

While the preamble is being written, WCLK must continue to clock in all "0" NRZ data. After the required sync field has been written (approx. 8 byte times, min.), the NRZ data must be changed to 93H for a minimum of 5 byte times to write the minimum 5 byte equalizer training pattern. The device will continue to autogenerate the sync field pattern until the first 93H is latched at the NRZ interface, and detected. The device encodes the 93H pattern and writes the result as the training sequence. Next, the NRZ data must be changed to 96H for 1 byte time to write the sync byte. The user data must be presented at the NRZ interface immediately following the sync byte. Finally, after the last byte of user data has been clocked in, the WG/WG must remain active for a minimum of 28 NRZ-bit times in byte-wide mode to ensure the that the device is flushed of data (The delay is 29 NRZ-bit times in dual bit mode). WG/WG can then go inactive. WD/WD stops toggling a maximum of 2 NRZ (RCLK) time periods after WG/WG goes inactive.

The SSI 32P4904 also allows the precoder to be preset when the first training byte arrives at the precoder. With the Power-Down Register bit 4 (PCDIS) set to 0, the SSI 32P4904 allows presetting of the precoder. When the PCDIS bit is set to 0, the Power-Down Register bit 5 (PCSPOL) allows the precoder to be preset if the PCSPOL bit is a 1 and reset if the PCSPOL bit is set to 0. This allows the state of the sync pattern to be determined depending on the amount of training bytes sent to the NRZ interface. If the PCSPOL bit is set at 0 (precoder reset), the low frequency sync byte pattern

(or its inverse) is output of WD/WD. If an odd number of training bytes is sent. If an even number of training bytes are sent, then the high frequency sync byte is output from WD/WD.

#### **Direct Write Mode 1**

In this direct write mode, the NRZ data from the byte-wide interface bypasses the scrambler, the 8,9 encoder and the precoder, but is precompensated before going to the write data flip-flop and then to the WD/WD output pins. The precomp should be set to zero in this mode. The purpose of routing the signal to the precomp circuit is to generate a return to zero pulse every time a "1" occurs in the data so that the write data flip-flop is toggled. WCLK is required to clock the byte-wide NRZ data into the NRZ interface. Direct write mode 1 is entered simply by setting the DW bit (bit 0) in the Control Operating Register. This mode is not valid when using the dual bit NRZ interface.

#### **Direct Write Mode 2**

In this direct write mode, the data presented at the DWI/DWI input pins directly toggles the write data flip-flop which drives the WD/WD output pins. No WCLK is required in this mode, and the WD/WD output is not resynchronized. Direct write mode 2 is entered simply by driving the DWR input low.

#### **DATA READ MODE OPERATION**

Data read mode is initiated by setting the read gate (RG) input pin high. This action causes the data synchronizer to begin acquisition of the clock from the incoming VCO sync pattern. To achieve this, the data synchronizer utilizes a fully integrated fast acquisition PLL to accurately develop the sample clock. This PLL is normally locked to the time base generator output, but when the read gate input (RG) goes high, the PLL's reference input is switched to the filtered incoming read signal.

#### Acquisition of DS VCO Sync

When RG is asserted an internal counter begins counting the pulses that are qualified by the dual level pulse qualifier given the polarity changes of the incoming 1,1,-1,-1,1,1 read back pattern defined by the VCO sync field. When the count reaches 4, the internal read gate is asserted and the DS PLL input is switched from the TBG's VCO output to the sampled data input. This is also the point at which the DS PLL's phase detector is switched from the phase-frequency detector to the decision directed phase detector. The counter is also used to determine whether the selected sync field count, SFC, has been achieved. When the

FIGURE 8: Hard Sector Write Sequence

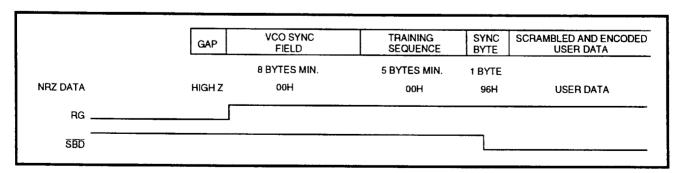

FIGURE 9: Hard Sector Read Sequence

#### Acquisition of DS VCO Sync (continued)

counter reaches the value specified by SFC, the data synchronizer PLL is assumed to be locked and settled (VCO lock). Also at SFC, the phase detector gain switch and the AGC mode switch occur. To allow for different preamble lengths, the SFC can be set to 64, 80, 96 or 128 from the Sample Loop Control Register. These values for the SFC may be thought of as the number of code clock periods in the sync field, but they actually represent twice the number of incoming polarity changes required.

## VCO Lock, PD Gain, AGC Mode Switch, and Code Word Boundary Detector Enable

At SFC, one of two phase tracking methods will be chosen depending on the enable phase detector gain switching (GS) bit in the Control Operating Mode Register. When the GS bit is high, the phase detector gain is reduced by a factor of 5 after the SFC count is reached. When the GS bit is low, no phase detector gain switching takes place.

Also after SFC, the AGC feedback will be switched from the continuous time full-wave rectifier to sampled data feedback.

At SFC, the internal VCO lock signal activates the code word boundary detection circuitry to define the proper decode boundaries. Also, at count SFC, the RCLK generator source switches from the TBG's VCO output to the DS VCO clock signal which is phase locked to the incoming read data samples. The DS VCO is assumed locked to the incoming read samples at this point. A maximum of 1 RCLK time period may occur for the RCLK transition, however, no short duration glitches will occur. After the code word detection circuitry finds the proper code word boundary, the RCLK generator is resynchronized to guarantee that the RCLK is in sync with the data. The RCLK and NCLK outputs will not glitch and will not toggle during the RCLK generator resynchronization for up to 2 byte times maximum.

Also at the code word boundary detect, the internal 9-bit code words are allowed to pass to the ENDEC for decoding. This decoding will occur until read gate is deasserted.

#### **Adaptive Equalizer Training Sequence**

As was previously discussed, in a normal write sequence, a minimum of 5 bytes of NRZ 93H and one byte of 96H must be written between the end of the VCO sync field and the beginning of the user data. The 5 bytes of 93H are 8,9 encoded and precoded during write mode to produce the adaptive equalizer training pattern. During read mode, this sequence (100110011 read data sequence) is used to adaptively train the 3-tap transversal filter in a zero forcing manner. The error at the filter output is integrated to derive the tap weight multiplying coefficient,  $k_{\rm m}$ . The filter input and output taps will have the same km. It is anticipated that the continuous time filter will be used for coarse equalization and that transversal filter will be used adaptively for fine tuning. This will reduce k<sub>m</sub>'s range and accuracy requirements. Since there are encoded user data patterns that will not produce an equalizer correction error, an equalization hold during data mode can selected from the Sample Loop Control Register. After the training pattern, if the loop is active during data, the equalizer loop gain will be reduced by 4. The loop's integration time constant is made inversely proportional to the selected data rate.

#### Sync Byte Detect and NRZ Output

As the read data is 8,9 decoded, it is compared to an internally fixed sync byte (96H). When a match is found, the sync byte detect (SBD) pin goes low and the NRZ output data that until now was held low, is changed to 96H. The next byte presented on the NRZ outputs is the first byte of user data. SBD will remain low and NRZ data will continue to be presented at the NRZ interface until the read gate is deasserted at which point SBD goes high and the NRZ outputs go to a high impedance state.

#### **POWER-DOWN OPERATION**

The power management modes of the SSI 32P4904 are determined by the states of the Power-Down Register bits and the PDWN and SG inputs. The individual sections of the chip can be powered down or up using the Power-Down Register. A high level in a Power-Down Register bit disables that section of the circuit. The power-down information from the Power-Down Register takes effect immediately after the SDEN pin goes low.

When the PDWN input is low, the chip goes into full power-down mode regardless of the Power-Down Register settings or the state of the SG input.

When PDWN is high, SG will force the AGC, filter, and pulse qualifier circuits (front end) to be active by overriding the front end register bit. The back end Power-Down Register bits, which include the data separator and time base generator are not affected by the SG input.

The serial port is active in all power-down modes.

The time to restart from a full power-down is dependent on the PLL loop filter and the data rate.

The truth table for the various modes of operation is shown below:

| SG, PDWN            | 1,1 | 1,0 | 0,1 | 0,0 |

|---------------------|-----|-----|-----|-----|

| Front End           | ON  | OFF | R   | OFF |

| Data Separator      | R   | OFF | R   | OFF |

| Time Base Generator | R   | OFF | R   | OFF |

| Serial Port         | ON  | ON  | ON  | ON  |

R = Controlled by register bit. (Register bit = 1 turns circuits OFF, Register bit = 0 turns circuits ON)

## **REGISTER DESCRIPTION**

## **SERIAL PORT REGISTER DEFINITIONS**

| Complete Register String ID  | А3       | A2     | <b>A</b> 1                                                                                                                                     | A0                                     | S2         | S1                                   | S0         | R/W             |                |

|------------------------------|----------|--------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------------|--------------------------------------|------------|-----------------|----------------|

| Power-Down Register          | 0        | 0      | 0                                                                                                                                              | 0                                      | 0          | 1                                    | 0          | 0               | 04H            |

|                              | Bit 7    | ATO    | Bit set                                                                                                                                        | to 1 enab                              | les ATO.   | Set bit to                           | 0 for no   | rmal oper       | ation          |

|                              | Bit 6    | PCD    | Bit set to 1 disables precoder but does not initialize the flip-flop                                                                           |                                        |            |                                      |            |                 | e the          |

|                              | Bit 5    | PCSPOL | 1 =                                                                                                                                            |                                        | ecoder s   | Bit<br>tate is 1 (<br>tate is 0 (    |            |                 |                |

|                              | Bit 4    | PCSDIS | 1 =                                                                                                                                            | ler Force<br>= disable  <br>= enable p | precoder   | force                                |            |                 |                |

|                              | Bit 3    | FBYP   | 1 =                                                                                                                                            | lypass Bit<br>bypass t<br>normal c     | filter     | l                                    |            |                 |                |

|                              | Bit 2    | TB     | Time b                                                                                                                                         | ase gene                               | rator pov  | ver-down                             | when bit   | set to 1        |                |

|                              | Bit 1    | DS     | Data s                                                                                                                                         | eparator p                             | oower-do   | wn when                              | bit set to | 1               |                |

|                              | Bit 0    | PD     | AGC, F                                                                                                                                         |                                        | se detect  | or, and se                           | ervo pow   | er-down v       | vhen           |

| Data Filter Cutoff Register  | 0        | 0      | 0                                                                                                                                              | 1                                      | 0          | 1                                    | 0          | 0               | 14H            |

|                              | Bit 7    | X      | Don't C                                                                                                                                        | Care                                   |            |                                      |            |                 |                |

|                              | Bits 6-0 | FC6-0  | fc (MH                                                                                                                                         |                                        | 0122 • F   | tting in no<br>C <sup>2</sup> + 0.17 |            |                 |                |

| Servo Filter Cutoff Register | 0        | 0      | . 1                                                                                                                                            | 0                                      | 0          | . 1                                  | 0          | 0               | 24H            |

|                              | Bit 7    | Х      | Don't C                                                                                                                                        | Care                                   |            | . ,                                  | <u></u>    | .,,             |                |

|                              | Bits 6-0 | FCS6-0 | fc (MH                                                                                                                                         |                                        | 0122 • F   | tting in se<br>CS <sup>2</sup> + 0.1 |            | e<br>5 - 0.6118 | ,              |

| Data Filter Boost Register   | 0        | 0      | 1                                                                                                                                              | 1                                      | 0          | 1                                    | 0          | 0               | 34H            |

|                              | Bit 7    | Х      | Don't C                                                                                                                                        | Care                                   |            |                                      |            |                 |                |

|                              | Bits 6-0 | FB6-0  | Filter boost setting in servo mode Boost (dB) = 20 • log [0.02083 • FB + 0.000056 • FB • F0 - 0.000013 • FB <sup>2</sup> + 1] 0 ≤ FB ≤ 127 dec |                                        |            |                                      |            | • FC            |                |

| Servo Filter Boost Register  | 0        | 1      | 0                                                                                                                                              | 0                                      | 0          | 1                                    | 0          | 0               | 44H            |

|                              | Bit 7    | Х      | Don't C                                                                                                                                        | are                                    |            |                                      |            |                 |                |

|                              | Bits 6-0 | FBS6-0 | Boost (d                                                                                                                                       |                                        | log [0.020 |                                      |            | 56 • FBS        | • F <b>C</b> S |

<sup>1 =</sup> power-down; 0 = power-up

| Complete Register String ID | А3       | <b>A2</b> | <b>A</b> 1                                                                                                                                                                                                                                                              | A0                     | S2 | S1 | S0        | R/W |     |

|-----------------------------|----------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----|----|-----------|-----|-----|

| Viterbi Detector            | 0        | 1         | 0                                                                                                                                                                                                                                                                       | 1                      | 0  | 1  | 0         | 0   | 54H |

| Threshold Register          | Bit 7    | Х         | Don't (                                                                                                                                                                                                                                                                 | Care                   | •  | *  |           |     |     |

|                             | Bits 6-0 | VD6-0     | Viterbi qualification threshold voltage<br>Vтн (mV) = 7.42 • VD + 20<br>45 ≤ VD ≤ 127 dec                                                                                                                                                                               |                        |    |    |           |     |     |

| Data Level Threshold        | 0        | 1         | 1                                                                                                                                                                                                                                                                       | 0                      | 0  | 1  | 0         | 0   | 64H |

| Register                    | Bit 7    | Х         | Don't (                                                                                                                                                                                                                                                                 | Care                   |    |    |           |     |     |

|                             | Bits 6-0 | LD6-0     | Data level qualification threshold voltage if WP/LT Register: ALE = 0 ( Fixed levels ) Prior to SFC: Lth (mV) = 4.784 • LD + 26 After SFC: Lth (mV) = 3.768 • LD + 18, 32 ≤ LD ≤ 127 dec if WP/LT Register: ALE = 1 ( Adaptive levels ) After SFC: Lth (%) = 0.787 • LD |                        |    |    |           |     |     |

| Servo Level Threshold       | 0        | 1         | 1                                                                                                                                                                                                                                                                       | 1                      | 0  | 1  | 0         | 0   | 74H |

| Register                    | Bit 7    | Х         | Don't                                                                                                                                                                                                                                                                   | Care                   |    |    | -         |     |     |

|                             | Bits 6-0 | LDS6-0    |                                                                                                                                                                                                                                                                         | level qua<br>mV) = 4.7 |    |    | l voltage | ,   |     |

| Complete Register String ID | АЗ       |            | A2                                                                                                                                         | A1                                                                                                                                              | A0                                  | S2                                                                                                                              | 2       | S1        | SO      |       | R/W       |       |  |          |

|-----------------------------|----------|------------|--------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|---------|-----------|---------|-------|-----------|-------|--|----------|

| Control Test Mode Register  | 1        |            | 0                                                                                                                                          | 0                                                                                                                                               | 0                                   | 0                                                                                                                               |         | 1         | 0       |       | 0         | 84H   |  |          |

|                             | Bit      | 7          | EFR                                                                                                                                        | 0 =                                                                                                                                             | e Clock S<br>sample cl<br>sample cl | lock is                                                                                                                         | from    |           | -       |       | •         |       |  |          |

|                             | Bit (    | Bit 6      |                                                                                                                                            | Bit 6 -                                                                                                                                         |                                     | 1 = sample clock is from the TBG output, a test mode  Factory reserved bit, must be set to 0 in application                     |         |           |         |       |           |       |  | <u>_</u> |

|                             | Bits 5   | -3         | TP3-1                                                                                                                                      | Multipl                                                                                                                                         | exed test                           | point                                                                                                                           | selec   | ction     |         |       |           |       |  |          |

|                             | ТРЗ      | TP2        | TP1                                                                                                                                        | FU                                                                                                                                              | NCTION                              |                                                                                                                                 | TPA     | λ+, ΤΡΔ   | ١-      | TF    | PB+, TP   | B-    |  |          |

|                             | 0        | 0          | 0                                                                                                                                          | Test                                                                                                                                            | Points Of                           | f H                                                                                                                             | ligh I  | mpeda     | nce     | High  | Imped     | ance  |  |          |

|                             | 0        | 0          | 1                                                                                                                                          | Equali                                                                                                                                          | zer Outpu                           | ıts                                                                                                                             | Equ     | alizer /  | Α .     | Ec    | qualizer  | В     |  |          |

|                             | 0        | 1          | 0                                                                                                                                          | Eq Con                                                                                                                                          | t/Phase [                           | Det E                                                                                                                           | quali   | zer Cor   | ntrol F | Phase | e Detec   | t Out |  |          |

|                             | 0        | 1          | 1                                                                                                                                          | Viterbi                                                                                                                                         | Survival                            | ln                                                                                                                              | SSI     | N B+, E   | 3-      | SS    | SIN A+,   | A-    |  |          |

|                             | 1        | 0          | 0                                                                                                                                          | Survi                                                                                                                                           | val Out/ Ir                         | n                                                                                                                               | Regi    | sters A,  | В       | SS    | SIN A+,   | A-    |  |          |

|                             | 1        | 0          | 1                                                                                                                                          | TBG /A                                                                                                                                          | GC Cont                             | rol                                                                                                                             | TBG     | 3 Outpu   | ıt 📗    | BYP   | Buffe (Bu | red)  |  |          |

|                             | 1        | 1          | 0                                                                                                                                          | Eq Oı                                                                                                                                           | ıt/Viterbi I                        | n                                                                                                                               | Equ     | ıalizer A | 4       | SS    | SIN A+,   | Α-    |  |          |

|                             | 1        | 1          | 1                                                                                                                                          | Eq Oı                                                                                                                                           | ıt/VCO ÷                            | 2                                                                                                                               | Equ     | ıalizer A | ١       | DS    | VCO -     | - 2   |  |          |

|                             | Bit 2    | 2   \      | /RDT                                                                                                                                       | 1 =                                                                                                                                             | digital inp                         | 'RDT Input<br>igital input to the data decoder, used in testing only<br>iterbi survival outputs to the data decoder, normal use |         |           |         |       |           |       |  |          |

|                             | Bit 1    |            | DT                                                                                                                                         | Enable TBG Pump-Down  1 = continuous pump-down, for test use only; FLTR1+ sinks current; FLTR1- sources current  0 = not in pump-down test mode |                                     |                                                                                                                                 |         |           |         | ent   |           |       |  |          |

|                             | Bit 0 UT |            | Enable TBG Pump-Up  1 = continuous pump-up, for test use only;  FLTR1+ sources current; FLTR1- sinks current  0 = not in pump-up test mode |                                                                                                                                                 |                                     |                                                                                                                                 |         |           | ent     |       |           |       |  |          |

| N Counter Register          | 1        |            | 0                                                                                                                                          | 0                                                                                                                                               | 1                                   | 0                                                                                                                               |         | 1         | 0       |       | 0         | 94H   |  |          |

|                             | Bit 7    | <u>'  </u> | Х                                                                                                                                          | Don't Care                                                                                                                                      |                                     |                                                                                                                                 |         |           |         |       |           |       |  |          |

|                             | Bits 6   | -0         | N6-0                                                                                                                                       | N Cour<br>2 < N <                                                                                                                               |                                     |                                                                                                                                 |         |           |         |       |           |       |  |          |

| M Counter Register          | 1        |            | 0                                                                                                                                          | 1                                                                                                                                               | 0                                   | 0                                                                                                                               |         | 1         | 0       |       | 0         | A4H   |  |          |

|                             | Bits 7   | -0         | M7-0                                                                                                                                       | M Cour<br>2 < M <<br>FTBG =                                                                                                                     |                                     | [(M+1                                                                                                                           | I) ÷ (N | N+1)]     |         | •     |           |       |  |          |

| Data Rate Register          | 1        |            | .0                                                                                                                                         | 1                                                                                                                                               | 1                                   | 0                                                                                                                               |         | 1         | 0       |       | 0         | B4H   |  |          |

|                             | Bit 7    |            | Х                                                                                                                                          | Don't C                                                                                                                                         | are                                 |                                                                                                                                 |         |           |         |       |           |       |  |          |

|                             | Bits 6   | -O [       | )R6-0                                                                                                                                      | Fvco (MHz) = 9/8 Data Rate = 0.6685 •DR + 5.1<br>Write Precomp/Level Threshold Time Constant Register                                           |                                     |                                                                                                                                 |         |           | ster    |       |           |       |  |          |

| Complete Register String ID   | АЗ       | A2     | A1                                                                                                        | A0                      | S2       | <b>S</b> 1  | S0     | R/W |      |

|-------------------------------|----------|--------|-----------------------------------------------------------------------------------------------------------|-------------------------|----------|-------------|--------|-----|------|

| Write Precomp/Level Threshold | 1        | 1      | 0                                                                                                         | 0                       | 0        | 1           | 0      | 0   | C4H  |

| Time Constant Register        | Bits 7-5 | TC3-1  | Adaptive level qualification threshold time constator decision directed phase detector. (valid after SFC) |                         |          |             |        |     |      |

|                               | ТСЗ      | TC2    | TC1                                                                                                       | TIME                    | CONSTA   | NT          |        |     |      |

|                               | 0        | 0      | 0                                                                                                         | 0 300 ns                |          |             |        |     |      |

|                               | 0        | 0      | 1                                                                                                         | 400 n                   | S        |             |        |     |      |

|                               | 0        | 1      | 0                                                                                                         | 500 n                   | 5        |             |        |     |      |

|                               | 0        | 1      | 1                                                                                                         | 600 n                   | s        |             |        |     |      |

|                               | 1        | 0      | 0                                                                                                         | 700 n                   | s        |             |        |     |      |

|                               | 1        | 0      | 1                                                                                                         | 800 n                   | s        |             |        |     |      |

|                               | 1        | 1      | 0                                                                                                         | 900 n                   | S        |             |        |     |      |

|                               | 1        | 1      | 1                                                                                                         | 1000                    | ns       |             |        |     |      |

|                               | Bit 4    | ALE    | Enable Adaptive Level Qualification in Decision Directed Phase Detector 1 = adaptive mode                 |                         |          |             |        |     | cted |

|                               |          |        |                                                                                                           | fixed lev               |          | cation      |        |     |      |

|                               | Bit 3    | FSD    | Fail Safe Disable Bit                                                                                     |                         |          |             |        |     |      |

|                               |          |        | 1 = precomp fail safe off<br>0 = precomp fail safe on                                                     |                         |          |             |        |     |      |

| Write Precomp/Level Threshold | 1        | 1      | 0                                                                                                         | 0                       | 0        | 1           | 0      | 0   | C4H  |

| Time Constant Register        | Bits 2-0 | WPC2-0 | Write F                                                                                                   | recomp                  | Setting  |             |        |     |      |

|                               | WPC2     | WPC1   | WPC0                                                                                                      | WRIT                    | E PREC   | OMP MA      | GNITUD | E   |      |

|                               | 0        | 0      | 0                                                                                                         | No pr                   | ecomp    |             |        |     |      |

|                               | . 0      | 0      | · 1                                                                                                       | 3.3%                    | code per | iod shift   |        |     |      |

|                               | 0        | 1      | 0                                                                                                         | 6.6%                    | code per | iod shift   |        |     |      |

|                               | 0        | 1      | 1                                                                                                         | 9.9%                    | code pei | iod shift   |        |     |      |

|                               | 1        | 0      | 0                                                                                                         | 13.2% code period shift |          |             |        |     |      |

|                               | 1        | 0      | 1                                                                                                         | 16.5% code period shift |          |             |        |     |      |

|                               | 1        | 1      | 0                                                                                                         | 19.8%                   | 6 code p | eriod shift |        |     |      |

|                               | 1        | 1      | 1                                                                                                         | 23.1%                   | 6 code p | eriod shift |        |     |      |

| Complete Register String ID | А3     | A2   | A1                                                                                                                                                                | A0                                                                       | S2        | S1    | S0  | R/W |     |  |  |

|-----------------------------|--------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-----------|-------|-----|-----|-----|--|--|

| Control Operating Register  | 1      | 1    | 0                                                                                                                                                                 | 1                                                                        | 0         | 1     | 0   | 0   | D4H |  |  |

|                             | Bits 7 | WGP  | 1 =                                                                                                                                                               | Write Gate Polarity 1 = positive (active high) 0 = negative (active low) |           |       |     |     |     |  |  |

|                             | Bit 6  | SPDM | Servo Peak Detect Mode  1 = dual comparator (window)  0 = hysteresis                                                                                              |                                                                          |           |       |     |     |     |  |  |

|                             | Bit 5  | ВР   | 1 =                                                                                                                                                               | e Bypass<br>= enabled<br>= disabled                                      |           |       | on) |     |     |  |  |

|                             | Bit 4  | DB   | Enable Dual Bit Interface  1 = dual bit DB1-0 interface enabled  0 = dual bit interface disabled,  i.e. byte-wide interface enabled                               |                                                                          |           |       |     |     |     |  |  |

|                             | Bit 3  | ВТ   | Bypass Time Base Generator  1 = data synchronizer reference frequency is FREF input  0 = data synchronizer reference frequency is TBG  output, (normal operation) |                                                                          |           |       |     |     |     |  |  |

|                             | Bit 2  | SD   | 1 =                                                                                                                                                               | e Data So<br>= disableo<br>= enabled                                     | i         |       |     |     |     |  |  |

|                             | Bit 1  | GS   | DS Phase Detector Gain Switching 1 = disabled 0 = enabled, (normal operation)                                                                                     |                                                                          |           |       |     |     |     |  |  |

|                             | Bit 0  | DW   | (bypas<br>1 =                                                                                                                                                     | e Direct W<br>ses scrar<br>e enabled<br>disablec                         | nbler & E | NDEC) |     |     |     |  |  |

| Complete Register String ID                                                                                                                                                                                                                          | А3       | A2     | <b>A</b> 1                     | A0                                                 | S2                                                      | S1                                    | S0                           | R/W                      |         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------|--------------------------------|----------------------------------------------------|---------------------------------------------------------|---------------------------------------|------------------------------|--------------------------|---------|

| Sample Loop Control                                                                                                                                                                                                                                  | 1        | 1      | 1                              | 0                                                  | 0                                                       | 1                                     | 0                            | 0                        | E4H     |

| Register                                                                                                                                                                                                                                             | Bit 7    | WGH    | Bit set                        | to 1 enab                                          | les hold                                                | while Wo                              | is active                    | •                        |         |