Data sheet: Advance Information

#### Document Number: MC34GD3000 Rev. 3.0, 5/2016

# Three phase field effect transistor pre-driver

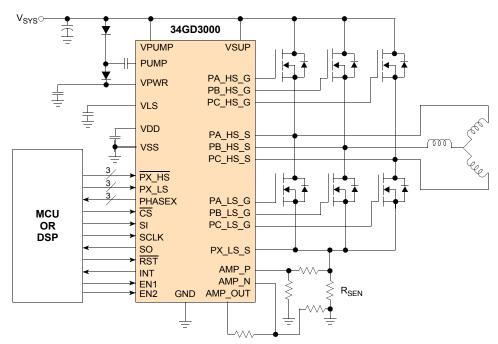

The 34GD3000 is a field effect transistor (FET) pre-drivers designed for three phase motor control and similar applications. The integrated circuit (IC) uses SMARTMOS technology.

The IC contains three high-side FET pre-drivers and three low-side FET pre-drivers. Three external bootstrap capacitors provide gate charge to the high-side FETs.

The IC interfaces to a MCU via six direct input control signals, an SPI port for device setup and asynchronous reset, enable and interrupt signals. Both 5.0 V and 3.3 V logic level inputs are accepted and 5.0 V logic level outputs are provided.

#### **Features**

- Extended supply voltage operating range: 6.0 V to 60 V

- Wide dead time range (50 ns to 12  $\mu s$ ) programmable via the SPI port

- · Gate drive capability of 1.0 A to 2.5 A

- Charge pump ensures sufficient external FET drive at low supply voltages

- Device protection against reverse charge-injection from C<sub>GD</sub> and C<sub>GS</sub> of external FETS

- Integrated overcurrent, desaturation, and phase fault-detection

- Immunity against positive or negative transient voltage spikes on the gate driver

- · Current shoot-through protection built into dead time control

- Supports direct 3.3 V and 5.0 V logic interface to MCUs

- · Integrated current sensing amplifier

- · Device configuration and diagnostics through the SPI

### 34GD3000 Industrial

#### THREE PHASE PRE-DRIVER

EP SUFFIX (Pb-FREE) 98ASA00654D 56-PIN QFN

#### **Applications**

- 12 V 48 V 3-phase brushless DC (BLDC) motors and permanent magnet synchronous motors (PMSM)

- Pool pumps, hospital beds, electric scooters

- · Industrial robotics, pumps and fans

- · Portable power tools, commercial fans/blowers

- Small kitchen appliances

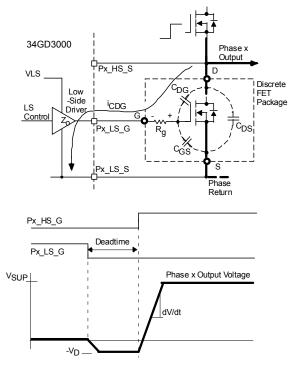

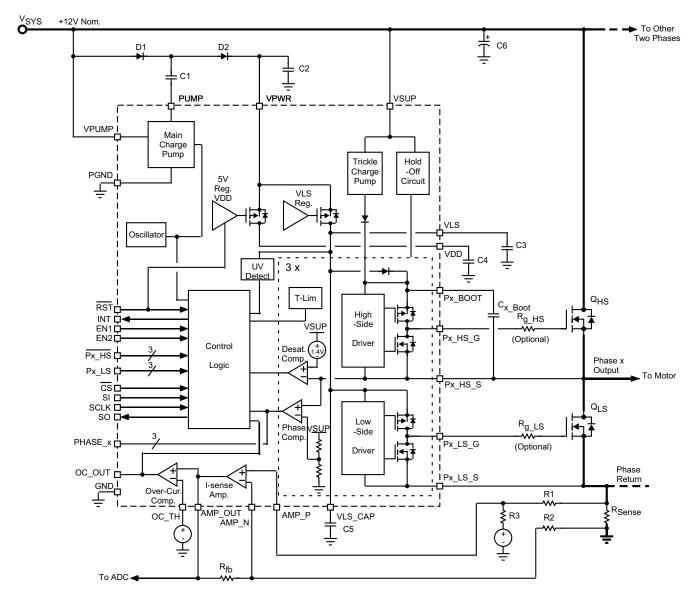

Figure 1. 34GD3000 simplified application diagram

<sup>\*</sup> This document contains certain information on a new product.

Specifications and information herein are subject to change without notice.

# 1 Orderable parts

#### Table 1. Orderable part variations

| Part number <sup>(1)</sup> | Temperature (T <sub>A</sub> ) | Package    |  |  |

|----------------------------|-------------------------------|------------|--|--|

| MC34GD3000EP               | -20 °C to 105 °C              | 56 Pin QFN |  |  |

#### Notes

1. To order parts in tape & reel, add the R2 suffix to the part number.

# 2 Internal block diagram

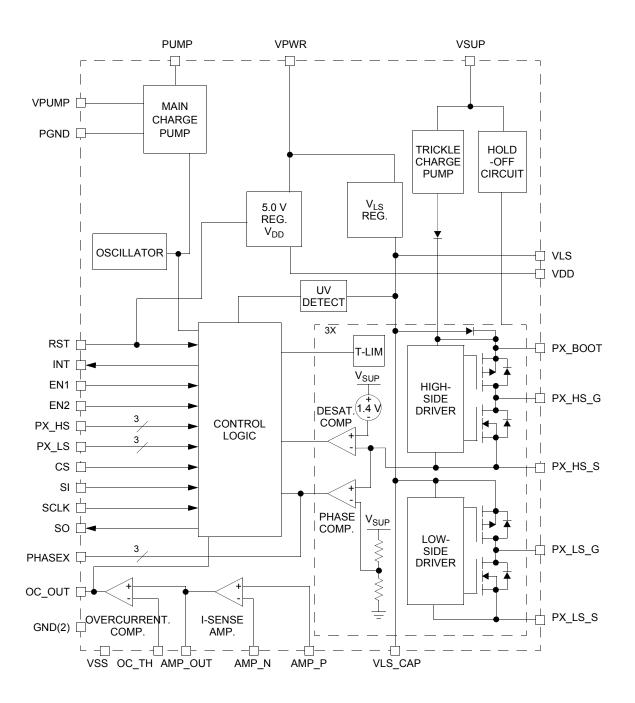

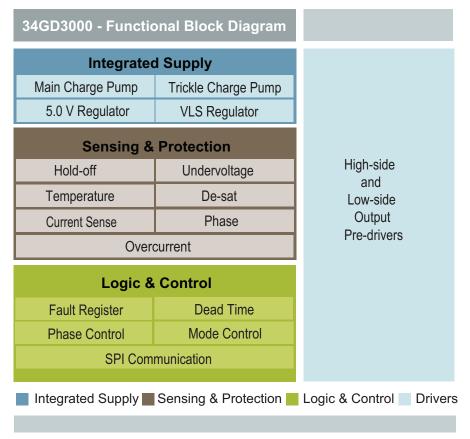

Figure 2. 34GD3000 simplified internal block diagram

3

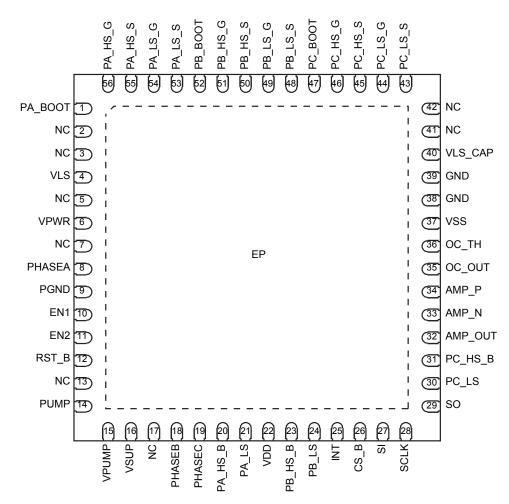

### 3 Pin connections

Transparent

Top View

Figure 3. 34GD3000 pin connections

A functional description of each pin can be found in the Functional pin description section beginning on page 20.

Table 2. 34GD3000 pin definitions

| Pin                           | Pin name | Pin function   | Formal name       | Definition                                                                                                                                             |

|-------------------------------|----------|----------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                             | PA_BOOT  | Analog input   | Phase A bootstrap | Bootstrap capacitor for Phase A                                                                                                                        |

| 2, 3, 5, 7, 13,<br>17, 41, 42 | NC       | No connect     |                   | No connection                                                                                                                                          |

| 4                             | VLS      | Analog output  | VLS regulator     | VLS regulator output; power supply for the gate drives                                                                                                 |

| 6                             | VPWR     | Power input    | Voltage power     | Power supply input for gate drives                                                                                                                     |

| 8                             | PHASEA   | Digital output | Phase A           | Totem pole output of Phase A comparator; this output is low when the voltage on PA_HS_S (source of high-side FET) is less than 50% of V <sub>SUP</sub> |

| 9                             | PGND     | Ground         | Power ground      | Power ground for charge pump                                                                                                                           |

| 10                            | EN1      | Digital input  | Enable 1          | Logic signal input must be high (ANDed with EN2) to enable any gate drive output.                                                                      |

| 11                            | EN2      | Digital input  | Enable 2          | Logic signal input must be high (ANDed with EN1) to enable any gate drive output                                                                       |

Table 2. 34GD3000 pin definitions

| Pin    | Pin name | Pin function    | Formal name                    | Definition                                                                                                                                          |

|--------|----------|-----------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 12     | RST_B    | Digital input   | Reset                          | Reset input                                                                                                                                         |

| 14     | PUMP     | Power drive out | Pump                           | Charge pump output                                                                                                                                  |

| 15     | VPUMP    | Power input     | Voltage pump                   | Charge pump supply                                                                                                                                  |

| 16     | VSUP     | Analog input    | Supply voltage                 | Supply voltage to the load. This pin is to be connected to the common drains of the external high-side FETs                                         |

| 18     | PHASEB   | Digital output  | Phase B                        | Totem pole output of Phase B comparator. This output is low when the voltage on PB_HS_S (source of high-side FET) is less than 50% of $\rm V_{SUP}$ |

| 19     | PHASEC   | Digital output  | Phase C                        | Totem pole output of Phase C comparator. This output is low when the voltage on PC_HS_S (source of high-side FET) is less than 50% of $\rm V_{SUP}$ |

| 20     | PA_HS_B  | Digital input   | Phase A high-side              | Active low input logic signal enables the high-side driver for Phase A                                                                              |

| 21     | PA_LS    | Digital input   | Phase A low-side               | Active high input logic signal enables the low-side driver for Phase A                                                                              |

| 22     | VDD      | Analog output   | VDD regulator                  | VDD regulator output capacitor connection                                                                                                           |

| 23     | PB_HS_B  | Digital input   | Phase B high-side              | Active low input logic signal enables the high-side driver for Phase B                                                                              |

| 24     | PB_LS    | Digital input   | Phase B low-side               | Active high input logic signal enables the low-side driver for Phase B                                                                              |

| 25     | INT      | Digital output  | Interrupt                      | Interrupt pin output                                                                                                                                |

| 26     | CS_B     | Digital input   | Chip select                    | Chip select input. It frames SPI commands and enables SPI port                                                                                      |

| 27     | SI       | Digital input   | Serial in                      | Input data for SPI port. Clocked on the falling edge of SCLK, MSB first                                                                             |

| 28     | SCLK     | Digital input   | Serial clock                   | Clock for SPI port and typically is 3.0 MHz                                                                                                         |

| 29     | SO       | Digital output  | Serial Out                     | Output data for SPI port. Tri-state until CS becomes low                                                                                            |

| 30     | PC_LS    | Digital Input   | Phase C low-side               | Active high input logic signal enables the low-side driver for Phase C                                                                              |

| 31     | PC_HS_B  | Digital input   | Phase C high-side              | Active low input logic signal enables the high-side driver for Phase C                                                                              |

| 32     | AMP_OUT  | Analog output   | Amplifier output               | Output of the current-sensing amplifier                                                                                                             |

| 33     | AMP_N    | Analog input    | Amplifier invert               | Inverting input of the current-sensing amplifier                                                                                                    |

| 34     | AMP_P    | Analog input    | Amplifier non-invert           | Non-inverting input of the current-sensing amplifier                                                                                                |

| 35     | OC_OUT   | Digital output  | Overcurrent out                | Totem pole digital output of the overcurrent comparator                                                                                             |

| 36     | OC_TH    | Analog input    | Overcurrent threshold          | Threshold of the overcurrent detector                                                                                                               |

| 37     | VSS      | Ground          | Voltage source supply          | Ground reference for logic interface and power supplies                                                                                             |

| 38, 39 | GND      | Ground          | Ground                         | Substrate and ESD reference, connect to VSS                                                                                                         |

| 40     | VLS_CAP  | Analog output   | VLS regulator output capacitor | VLS Regulator connection for additional output capacitor, providing low impedance supply source for low-side gate drive                             |

| 43     | PC_LS_S  | Power input     | Phase C Low-side<br>Source     | Source connection for Phase C low-side FET                                                                                                          |

| 44     | PC_LS_G  | Power Output    | Phase C low-side gate drive    | Gate drive output for Phase C low-side                                                                                                              |

| 45     | PC_HS_S  | Power input     | Phase C high-side source       | Source connection for Phase C high-side FET                                                                                                         |

| 46     | PC_HS_G  | Power output    | Phase C high-side gate drive   | Gate drive for output Phase C high-side FET                                                                                                         |

| 47     | PC_BOOT  | Analog input    | Phase C bootstrap              | Bootstrap capacitor for Phase C                                                                                                                     |

34GD3000

Table 2. 34GD3000 pin definitions

| Pin  | Pin name     | Pin function     | Formal name                  | Definition                                                                                                                                                            |

|------|--------------|------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FIII | riii ilaille | r iii iulictioii | i omiai name                 | Delinition                                                                                                                                                            |

| 48   | PB_LS_S      | Power input      | Phase B low-side source      | Source connection for Phase B low-side FET                                                                                                                            |

| 49   | PB_LS_G      | Power output     | Phase B low-side gate drive  | Gate drive for output Phase B low-side                                                                                                                                |

| 50   | PB_HS_S      | Power input      | Phase B high-side source     | Source connection for Phase B high-side FET                                                                                                                           |

| 51   | PB_HS_G      | Power output     | Phase B high-side gate drive | Gate drive for output Phase B high-side                                                                                                                               |

| 52   | PB_BOOT      | Analog input     | Phase B bootstrap            | Bootstrap capacitor for Phase B                                                                                                                                       |

| 53   | PA_LS_S      | Power input      | Phase A low-side source      | Source connection for Phase A low-side FET                                                                                                                            |

| 54   | PA_LS_G      | Power output     | Phase A low-side gate drive  | Gate drive for output Phase A low-side                                                                                                                                |

| 55   | PA_HS_S      | Power input      | Phase A high-side source     | Source connection for Phase A high-side FET                                                                                                                           |

| 56   | PA_HS_G      | Power output     | Phase A high-side gate drive | Gate drive for output Phase A high-side                                                                                                                               |

|      | EP           | Ground           | Exposed pad                  | Device performs as specified with the exposed pad un-terminated (floating) however, it is recommended the exposed pad be terminated to pin 29 (VSS) and system ground |

### 4 Electrical characteristics

### 4.1 Maximum ratings

Table 3. Maximum ratings

All voltages are with respect to V<sub>SS</sub> unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Symbol                                                                           | Ratings                                                                                                                                                                                                                              | Value                                                       | Unit | Notes |

|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|------|-------|

| Electrical rating                                                                | s                                                                                                                                                                                                                                    |                                                             |      |       |

| V <sub>SUP</sub>                                                                 | VSUP supply voltage     Normal operation (steady-state)     Transient survival                                                                                                                                                       | 60<br>-1.5 to 80                                            | V    | (2)   |

| $V_{PWR}$                                                                        | VPWR supply voltage     Normal operation (steady-state)     Transient survival                                                                                                                                                       | 58<br>-1.5 to 80                                            | V    | (2)   |

| V <sub>PUMP</sub>                                                                | Charge pump (PUMP, VPUMP)                                                                                                                                                                                                            | -0.3 to 40                                                  | V    |       |

| V <sub>LS</sub>                                                                  | VLS regulator outputs (VLS, VLS_CAP)                                                                                                                                                                                                 | -0.3 to 18                                                  | V    |       |

| $V_{DD}$                                                                         | Logic supply voltage                                                                                                                                                                                                                 | -0.3 to 7.0                                                 | V    |       |

| V <sub>OUT</sub>                                                                 | Logic output (INT, SO, PHASEA, PHASEB, PHASEC, OC_OUT)                                                                                                                                                                               | -0.3 to 7.0                                                 | V    | (3)   |

| V <sub>IN</sub>                                                                  | Logic input pin voltage (EN1, EN2, Px_HS, Px_LS, SI, SCLK, CS, RST) 10 mA                                                                                                                                                            | -0.3 to 7.0                                                 | V    |       |

| V <sub>IN_A</sub>                                                                | Amplifier input voltage  • (both inputs-GND), (AMP_P - GND) or (AMP_N - GND) 6.0 mA source or sink                                                                                                                                   | -7.0 to 7.0                                                 | V    |       |

| V <sub>OC</sub>                                                                  | Overcurrent comparator threshold 10 mA                                                                                                                                                                                               | -0.3 to 7.0                                                 | V    |       |

| V <sub>BOOT</sub><br>V <sub>HS_G</sub><br>V <sub>LS_G</sub>                      | Driver output voltage  • High-side bootstrap (PA_BOOT, PB_BOOT, PC_BOOT)  • High-side (PA_HS_G, PB_HS_G, PC_HS_G)  • Low-side (PA_LS_G, PB_LS_G, PC_LS_G)                                                                            | 75<br>75<br>16                                              | V    | (4)   |

| V <sub>HS_G</sub><br>V <sub>HS_S</sub><br>V <sub>LS_G</sub><br>V <sub>LS_S</sub> | Driver voltage transient survival  • High-side (PA_HS_G, PB_HS_G, PC_HS_G, PA_HS_S, PB_HS_S, PC_HS_S)  • Low-side (PA_LS_G, PB_LS_G, PC_LS_G, PA_LS_S, PB_LS_S, PC_LS_S)                                                             | -7.0 to 75.0<br>-7.0 to 75.0<br>-7.0 to 18.0<br>-7.0 to 7.0 | V    | (5)   |

| V <sub>ESD</sub>                                                                 | ESD voltage  Human body model - HBM (All pins except for the pins listed below)  Pins: PA_Boot, PA_HS_S, PA_HS_G, PB_Boot, PB_HS_S, PB_HS_G, PC_Boot, PC_HS_S, PC_HS_G, VPWR  Charge device model - CDM  Corner pins  All other pins | ±2000<br>±1000<br>±750<br>±300                              | V    | (6)   |

#### Notes

- 2. The device can withstand a voltage transient as defined by ISO7637 with peak voltage of 80 V.

- 3. Short-circuit proof, the device is not be damaged or induce unexpected behavior due to shorts to external sources within this range.

- 4. This voltage should not be applied without also taking voltage at HS\_S and voltage at PX\_LS\_S into account.

- 5. Actual operational limitations may differ from survivability limits. The V<sub>LS</sub> V<sub>LS\_S</sub> differential and the V<sub>BOOT</sub> V<sub>HS\_S</sub> differential must be greater than 3.0 V to insure the output gate drive maintains a commanded OFF condition on the output.

- 6. ESD testing is performed in accordance with the human body model (HBM) ( $C_{ZAP} = 100 \text{ pF}$ ,  $R_{ZAP} = 1500 \Omega$ ) and the charge device model (CDM), robotic ( $C_{ZAP} = 4.0 \text{ pF}$ ).

#### Table 3. Maximum ratings (continued)

All voltages are with respect to  $V_{SS}$  unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Symbol              | Ratings                                | Value       | Unit | Notes |

|---------------------|----------------------------------------|-------------|------|-------|

| Thermal ratings     |                                        |             |      | •     |

| T <sub>STG</sub>    | Storage temperature                    | -55 to +150 | °C   |       |

| T <sub>J</sub>      | Operating junction temperature         | -40 to +150 | °C   | (7)   |

| $R_{	heta JC}$      | Thermal resistance  • Junction-to-case | 1.5         | °C/W | (8)   |

| T <sub>SOLDER</sub> | Soldering temperature                  | Note 10     | °C   | (9)   |

#### Notes

- In order to meet or exceed the expected reliability performance level over 10 years of continuous operation, the user must take measures to

guarantee the device's average junction temperature does not exceed 125 °C. The device's maximum junction temperature remains as specified

in the data sheet.

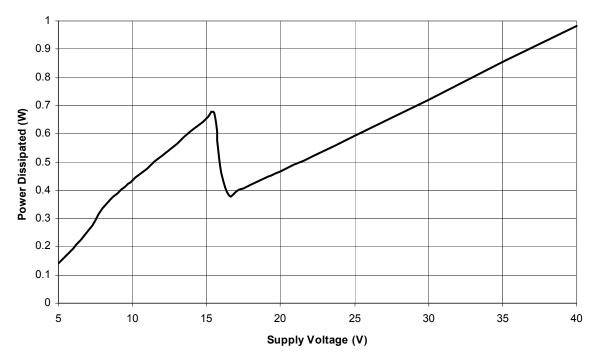

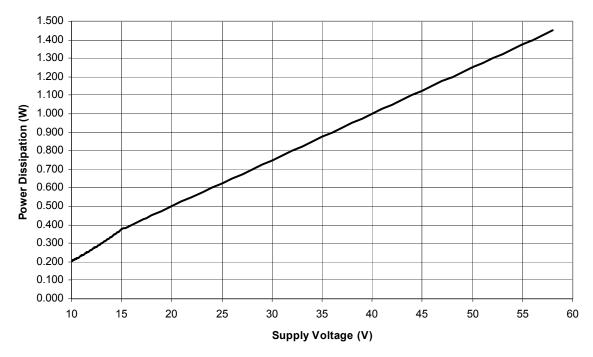

- 8. Case is considered EP pin 55 under the body of the device. The actual power dissipation of the device is dependent on the operating mode, the heat transfer characteristics of the board and layout and the operating voltage. See <a href="Figure 22">Figure 22</a> and <a href="Figure 23">Figure 23</a> for examples of power dissipation profiles of two common configurations. Operation above the maximum operating junction temperature results in a reduction in reliability leading to malfunction or permanent damage to the device.

- 9. Pin soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

- 10. NXP's package reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For peak package reflow temperature and moisture sensitivity levels (MSL), Go to www.nxp.com, search by part number [e.g. remove prefixes/suffixes and enter the core ID to view all orderable parts. (i.e. MC33xxxD enter 33xxx), and review parametrics.

### 4.2 Static electrical characteristics

#### Table 4. Static electrical characteristics

Characteristics noted under conditions 8.0 V  $\leq$  V<sub>PWR</sub> = V<sub>SUP</sub>  $\leq$  48 V, -20 °C  $\leq$  T<sub>A</sub>  $\leq$  105 °C, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Symbol                               | Characteristic                                                                                                                                                                                      | Min.        | Тур.     | Max.      | Unit | Notes |

|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------|-----------|------|-------|

| Power inputs                         |                                                                                                                                                                                                     |             | <u>I</u> | 1         |      |       |

| V <sub>PWR_ST</sub>                  | VPWR supply voltage startup threshold                                                                                                                                                               | -           | 6.0      | 8.0       | ٧    | (11)  |

| I <sub>SUP</sub>                     | VSUP supply current, V <sub>PWR</sub> = V <sub>SUP</sub> = 48 V  RST and ENABLE = 5.0 V  No output loads on gate drive pins, no PWM  No output loads on gate drive pins, 20 kHz, 50% duty cycle     | _<br>_<br>_ | 1.0      | _<br>10   | mA   |       |

| I <sub>PWR_ON</sub>                  | VPWR supply current, V <sub>PWR</sub> = V <sub>SUP</sub> = 48 V  RST and ENABLE = 5.0 V  No output loads on gate drive pins, no PWM, outputs initialized  Output loads = 620 nC per FET, 20 kHz PWM | -<br>-      | 11<br>-  | 20<br>95  | mA   | (12)  |

| I <sub>SUP</sub><br>I <sub>PWR</sub> | Sleep state supply current, RST = 0 V  • V <sub>SUP</sub> = 48 V  • V <sub>PWR</sub> = 48 V                                                                                                         | -<br>-      | 14<br>56 | 30<br>110 | μΑ   |       |

| $V_{GATESS}$                         | Sleep state output gate voltage • IG < 100 μA                                                                                                                                                       | _           | _        | 1.3       | V    |       |

| $V_{Boot}$                           | Trickle charge pump (bootstrap voltage)  • V <sub>SUP</sub> = 14 V                                                                                                                                  | 22          | 28       | 32        | V    |       |

| V <sub>F</sub>                       | Bootstrap diode forward voltage at 10 mA                                                                                                                                                            | -           | _        | 1.2       | V    |       |

| /DD internal reç                     | ulator                                                                                                                                                                                              |             |          |           |      |       |

| $V_{DD}$                             | $V_{DD}$ output voltage, $V_{PWR}$ = 8.0 V to 48 V, C = 0.47 μF<br>• External load $I_{DD\_EXT}$ = 0 mA to 1.0 mA                                                                                   | 4.5         | _        | 5.5       | V    | (13)  |

| I <sub>DD</sub>                      | Internal V <sub>DD</sub> supply current, V <sub>DD</sub> = 5.5 V, no external load                                                                                                                  | _           | _        | 12        | mA   |       |

| VLS regulator                        |                                                                                                                                                                                                     |             | 1        |           |      | - 11  |

| I <sub>PEAK</sub>                    | Peak output current, V <sub>PWR</sub> = 16 V, V <sub>LS</sub> = 10 V                                                                                                                                | 350         | 600      | 800       | mA   |       |

| $V_{LS}$                             | Linear regulator output voltage, $I_{VLS}$ = 0 mA to 60 mA, $V_{PWR}$ > $V_{LS}$ + 2.0 V                                                                                                            | 13.5        | 15       | 17        | V    | (14)  |

| V <sub>THVLS</sub>                   | VLS disable threshold <sup>(15)</sup>                                                                                                                                                               | 7.5         | 8.0      | 8.5       | V    |       |

#### Notes

- 11. Operation with the charge pump is recommended when minimum system voltage could be less than 14 V.V<sub>PWR</sub> must exceed this threshold in order for the charge pump and V<sub>DD</sub> regulator to startup and drive V<sub>PWR</sub> to > 8.0 V. Once V<sub>PWR</sub> exceeds 8.0 V, the circuits continues to operate even if system voltage drops below 6.0 V.

- 12. This parameter is guaranteed by design. It is not production tested.

- 13. Minimum external capacitor for stable  $V_{DD}$  operation is 0.47  $\mu F$ .

- Recommended external capacitor for the V<sub>LS</sub> regulator is 2.2 μF low ESR at each pin VLS and VLS\_CAP.

- 15. When V<sub>LS</sub> is less than this value, the outputs are disabled and holdoff circuits are active. Recovery requires initialization when V<sub>LS</sub> rises above this threshold again. A filter delay of approximately 700 ns on the comparator output eliminates responses to spurious transients on V<sub>LS</sub>.

Characteristics noted under conditions 8.0 V  $\leq$  V<sub>PWR</sub> = V<sub>SUP</sub>  $\leq$  48 V, -20 °C  $\leq$  T<sub>A</sub>  $\leq$  105 °C, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Symbol                                                                   | Characteristic                                                                                                                                                                                                                                                         | Min.          | Тур.              | Max.             | Unit                 | Notes      |

|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------------|------------------|----------------------|------------|

| Charge pump                                                              |                                                                                                                                                                                                                                                                        |               | 1                 |                  | 1                    |            |

| R <sub>DS(on)</sub> _HS<br>R <sub>DS(on)</sub> _LS<br>V <sub>THREG</sub> | Charge pump  High-side switch on resistance Low-side switch on resistance Regulation threshold difference                                                                                                                                                              | -<br>-<br>250 | 6.0<br>5.0<br>500 | 10<br>9.4<br>900 | $\Omega$ $\Omega$ mV | (16), (18) |

| V <sub>CP</sub>                                                          | Charge pump output voltage  • I <sub>OUT</sub> = 40 mA, 6.0 V < V <sub>SYS</sub> < 8.0 V  • I <sub>OUT</sub> = 40 mA, V <sub>SYS</sub> > = 8.0 V                                                                                                                       | 8.5<br>12     | 9.5<br>-          | _<br>_           | V                    | (17), (18) |

| Gate drive                                                               |                                                                                                                                                                                                                                                                        |               |                   |                  |                      |            |

| R <sub>DS(on)_</sub> H_SRC                                               | $\label{eq:high-side} \begin{array}{l} \mbox{High-side driver on resistance (sourcing)} \\ \bullet \ \ \mbox{$V_{PWR}$ = $V_{SUP}$ = 16 V, -20 °C $\le $T_A$ $\le 25 °C$} \\ \bullet \ \ \mbox{$V_{PWR}$ = $V_{SUP}$ = 16 V, 25 °C $< $T_A$ $\le 105 °C$} \end{array}$ |               | _<br>_            | 6.0<br>8.5       | Ω                    |            |

| R <sub>DS(on)</sub> _H_SINK                                              | High-side driver on resistance (sinking)  • V <sub>PWR</sub> = V <sub>SUP</sub> = 16 V                                                                                                                                                                                 | -             | -                 | 3.0              | Ω                    |            |

| I <sub>HS_INJ</sub>                                                      | High-side current injection allowed without malfunction                                                                                                                                                                                                                | _             | _                 | 0.5              | Α                    | (18), (19) |

| R <sub>DS(on)_L_SRC</sub>                                                | Low-side driver on resistance (sourcing) $ \bullet \ \ V_{PWR} = V_{SUP} = 16 \ V, -20 \ ^{\circ}\text{C} \le T_{A} \le 25 \ ^{\circ}\text{C} $ $ \bullet \ \ V_{PWR} = V_{SUP} = 16 \ V, 25 \ ^{\circ}\text{C} < T_{A} \le 105 \ ^{\circ}\text{C} $                   |               | _<br>_            | 6.0<br>8.5       | Ω                    |            |

| R <sub>DS(on)_</sub> L_SINK                                              | Low-side driver on-resistance (sinking)  • V <sub>PWR</sub> = V <sub>SUP</sub> = 16 V                                                                                                                                                                                  | -             | -                 | 3.0              | Ω                    |            |

| I <sub>LS_INJ</sub>                                                      | Low-side current injection allowed without malfunction                                                                                                                                                                                                                 | _             | _                 | 0.5              | A                    | (18), (19) |

| V <sub>GS_H</sub><br>V <sub>GS_L</sub>                                   | Gate source voltage, V <sub>PWR</sub> = V <sub>SUP</sub> = 48 V  • High-side, I <sub>GATE</sub> = 0  • Low-side, I <sub>GATE</sub> = 0                                                                                                                                 | 13<br>13      | 14.8<br>15.4      | 16.5<br>17       | V                    | (20)       |

| V <sub>HS_G_HOLD</sub>                                                   | Reverse high-side gate holding voltage Gate output holding current = 2.0 μA Gate output holding current = 5.0 μA, V <sub>SUP</sub> < 26 V Gate output holding current = 5.0 μA, V <sub>SUP</sub> < 48 V                                                                | -<br>-<br>-   | 10<br>10<br>–     | 15<br>15<br>15   | V                    | (21)       |

#### Notes

- 16. When  $V_{LS}$  is this amount below the normal  $V_{LS}$  linear regulation threshold, the charge pump is enabled.

- 17.  $V_{SYS}$  is the system voltage on the input to the charge pump. Recommended external components: 1.0  $\mu$ F MLC, MUR 120 diode.

- 18. This parameter is a design characteristic, not production tested.

- 19. Current injection only occurs during output switch transitions. The IC is immune to specified injected currents for a duration of approximately 1.0 µs after an output switch transition. 1.0 µs is sufficient for all intended applications of this IC.

- 20. If a slightly higher gate voltage is required, larger bootstrap capacitors are required. At high duty cycles, the bootstrap voltage may not recover completely, leading to a higher output on-resistance. This effect can be minimized by using low ESR capacitors for the bootstrap and the VLS capacitors.

- 21. High-side gate holding voltage is the voltage between the gate and source of the high-side FET when held in an on condition. The trickle charge pump supplies bias and holding current for the high-side FET gate driver and output to maintain voltages after bootstrap events. This parameter is a design characteristic, not production tested.

Characteristics noted under conditions 8.0 V  $\leq$  V<sub>PWR</sub> = V<sub>SUP</sub>  $\leq$  48 V, -20 °C  $\leq$  T<sub>A</sub>  $\leq$  105 °C, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Notes                   |

|-------------------------|

|                         |

| (23)                    |

|                         |

| (22)                    |

|                         |

|                         |

| (24)                    |

|                         |

|                         |

|                         |

|                         |

|                         |

| (22), (27)              |

|                         |

| (25)                    |

|                         |

|                         |

| (28)                    |

|                         |

| (22), (26)              |

|                         |

| (22)                    |

| /<br>Ω<br>N<br>/<br>'°C |

#### Notes

- 22. This parameter is a design characteristic, not production tested.

- 23. As long as one input is in the common mode range there is no phase inversion on the output.

- 24. The hold off circuit is designed to operate over the full operating range of  $V_{SUP}$ . The specification indicates the conditions used in production test. Hold off is activated at  $V_{POR}$  or  $V_{THVLS}$ .

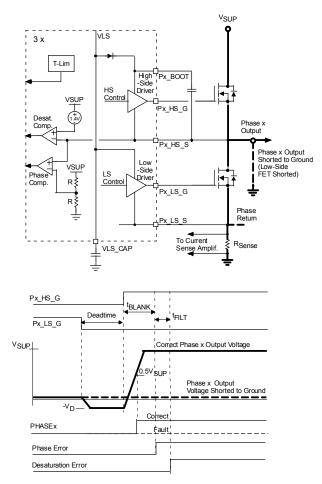

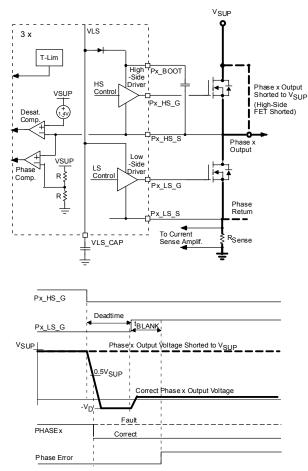

- 25. Desaturation is measured as the voltage drop below V<sub>SUP</sub>, thus the threshold is compared to the drain-source voltage of the external high-side FET. See Figure 5.

- 26. As long as one input is within V<sub>CM</sub> the output is guaranteed to have the correct phase. Exceeding the common mode rails on one input does not cause a phase inversion on the output.

- 27. Input resistance is impedance from the high-side source and is referenced to VSS. Approximate tolerance is ±20%.

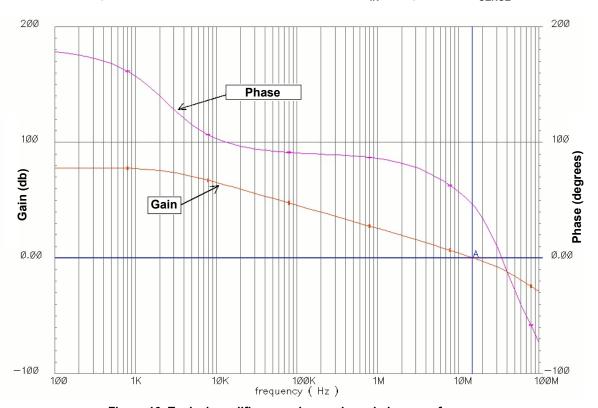

- 28. The current sense amplifier is unity gain stable with a phase margin of approximately 45°. See Figure 10.

34GD3000

Characteristics noted under conditions 8.0 V  $\leq$  V<sub>PWR</sub> = V<sub>SUP</sub>  $\leq$  48 V, -20 °C  $\leq$  T<sub>A</sub>  $\leq$  105 °C, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Symbol                             | Characteristic                                                                                                                                  | Min.                 | Тур.   | Max.                   | Unit  | Notes    |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------|------------------------|-------|----------|

| rent sense a                       | mplifier (continued)                                                                                                                            |                      |        | I                      |       |          |

| I <sub>b</sub>                     | Input bias current  • V <sub>CM</sub> = 2.0 V                                                                                                   | -200                 | -      | +200                   | nA    |          |

| I <sub>OS</sub>                    | Input offset current  • I <sub>OS</sub> = I <sub>AMP_P</sub> - I <sub>AMP_N</sub>                                                               | -80                  | ı      | +80                    | nA    |          |

| δl <sub>OS</sub> /δT               | Input offset current drift                                                                                                                      | _                    | 40     | _                      | pA/°C | (29)     |

| V <sub>OH</sub><br>V <sub>OL</sub> | Output voltage  • High level with $R_{LOAD}$ = 10 k $\Omega$ to $V_{SS}$ • Low level with $R_{LOAD}$ = 10 k $\Omega$ to $V_{DD}$                | V <sub>DD</sub> -0.2 | _<br>_ | V <sub>DD</sub><br>0.2 | V     |          |

| R <sub>I</sub>                     | Differential input resistance                                                                                                                   | 1.0                  | _      | _                      | MΩ    |          |

| I <sub>SC</sub>                    | Output short-circuit current                                                                                                                    | 5.0                  | _      | _                      | mA    |          |

| C <sub>I</sub>                     | Common mode input capacitance at 10 kHz                                                                                                         | _                    | -      | 10                     | pF    | (29), (3 |

| CMRR                               | Common mode rejection ratio at DC • CMRR = 20*log ((V <sub>OUT_DIFF</sub> /V <sub>IN_DIFF</sub> ) * (V <sub>IN_CM</sub> /V <sub>OUT_CM</sub> )) | 60                   | 80     | -                      | dB    |          |

| A <sub>OL</sub>                    | Large signal open loop voltage gain (DC)                                                                                                        | _                    | 78     | _                      | dB    | (29), (3 |

| NL                                 | Nonlinearity • $R_L = 1.0 \text{ k}\Omega$ , $C_L = 500 \text{ pF}$ , $0.3 < V_O < 4.8 \text{ V}$ , Gain = 5.0 to 15                            | -1.0                 | -      | +1.0                   | %     | (29), (3 |

| ervisory and                       | d control circuits                                                                                                                              |                      |        | ı                      | II.   | I        |

| V <sub>IH</sub><br>V <sub>IL</sub> | Logic inputs (Px_LS, Px_HS, EN1, EN2)  • High level input voltage threshold  • Low level input voltage threshold                                | 2.1                  | _<br>_ | _<br>0.9               | V     | (32)     |

| V <sub>IH</sub><br>V <sub>IL</sub> | Logic inputs (SI, SCLK, CS)  High level input voltage threshold  Low level input voltage threshold                                              | 2.1                  | -<br>- | _<br>0.9               | V     | (31), (3 |

| V <sub>IHYS</sub>                  | Input logic threshold hysteresis Inputs Px_LS, SI, SCLK, CS, Px_HS, EN1, EN2                                                                    | 100                  | 250    | 450                    | mV    | (31)     |

| I <sub>INPD</sub>                  | Input pull-down current, (Px_LS, SI, SCLK, EN1, EN2)  • $0.3 V_{DD} \le V_{IN} \le V_{DD}$                                                      | 8.0                  | -      | 18                     | μΑ    |          |

#### Notes

- 29. This parameter is a design characteristic, not production tested.

- 30. Without considering any offsets such as input offset voltage, internal mismatch and assuming no tolerance error in external resistors.

- 31. This parameter is guaranteed by design, not production tested.

- 32. Logic threshold voltages derived relative to a 3.3 V 10% system.

#### 34GD3000

Characteristics noted under conditions 8.0 V  $\leq$  V<sub>PWR</sub> = V<sub>SUP</sub>  $\leq$  48 V, -20 °C  $\leq$  T<sub>A</sub>  $\leq$  105 °C, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Symbol                  | Characteristic                                                                               | Min.                 | Тур.     | Max.                | Unit | Notes     |

|-------------------------|----------------------------------------------------------------------------------------------|----------------------|----------|---------------------|------|-----------|

| pervisory and           | l control circuits (continued)                                                               |                      |          |                     |      |           |

| I <sub>INPU</sub>       | Input pull-up current, (CS, Px_HS) • $0 \le V_{IN} \le 0.7 V_{DD}$                           | 10                   | -        | 25                  | μΑ   | (34)      |

| C <sub>IN</sub>         | Input capacitance • $0.0 \text{ V} \le \text{V}_{\text{IN}} \le 5.5 \text{ V}$               | -                    | 15       | _                   | pF   | (33)      |

| V <sub>TH_RST</sub>     | RST threshold                                                                                | 1.0                  | _        | 2.1                 | V    | (35)      |

| R <sub>RST</sub>        | RST pull-down resistance<br>• $0.3 \text{ V}_{DD} \le \text{V}_{IN} \le \text{V}_{DD}$       | 40                   | 60       | 85                  | kΩ   |           |

| V <sub>POR</sub>        | Power-off rst threshold, (V <sub>DD</sub> falling)                                           | 3.4                  | 4.0      | 4.5                 | V    |           |

| $V_{SOH}$               | SO high level output voltage • I <sub>OH</sub> = 1.0 mA                                      | 0.9 V <sub>DD</sub>  | -        | _                   | V    |           |

| V <sub>SOL</sub>        | SO low level output voltage  • I <sub>OL</sub> = 1.0 mA                                      | -                    | -        | 0.1 V <sub>DD</sub> | V    |           |

| I <sub>SO_LEAK_</sub> T | SO tri-state leakage current<br>• CS = 0.7 $V_{DD}$ , 0.3 $V_{DD} \le V_{SO} \le 0.7 V_{DD}$ | -1.0                 | -        | 1.0                 | μΑ   |           |

| C <sub>SO_T</sub>       | SO tri-state capacitance<br>• $0.0 \text{ V} \le \text{V}_{\text{IN}} \le 5.5 \text{ V}$     | -                    | 15       | _                   | pF   | (33), (36 |

| V <sub>OH</sub>         | INT high level output voltage • I <sub>OH</sub> = -500 μA                                    | 0.85 V <sub>DD</sub> | -        | V <sub>DD</sub>     | V    |           |

| V <sub>OL</sub>         | INT low level output voltage • I <sub>OL</sub> = 500 μA                                      | -                    | -        | 0.5                 | V    |           |

| ermal warning           |                                                                                              | l .                  | <u> </u> | <u>I</u>            |      | 1         |

| T <sub>WARN</sub>       | Thermal warning temperature                                                                  | 150                  | 170      | 185                 | °C   | (33), (37 |

| T <sub>HYST</sub>       | Thermal hysteresis                                                                           | 8.0                  | 10       | 12                  | °C   | (33)      |

#### Notes

- 33. This parameter is guaranteed by design, not production tested.

- 34. Pull-up circuits does not allow back biasing of V<sub>DD</sub>.

- 35. There are two elements in the RST circuit: 1) one generally lower threshold enables the internal regulator; 2) the second removes the reset from the internal logic.

- 36. This parameter applies to the OFF state (tri-stated) condition of SO is guaranteed by design but is not production tested.

- 37. The thermal warning circuit does not force IC shutdown above this temperature. It is possible to set a bit in the MASK register to generate an interrupt when overtemperature is detected, and the status bit always indicates if any of the three individual thermal warning circuits in the IC sense a fault.

## 4.3 Dynamic electrical characteristics

#### Table 5. Dynamic electrical characteristics

Characteristics noted under conditions 8.0 V  $\leq$  V<sub>PWR</sub> = V<sub>SUP</sub>  $\leq$  48 V, -20 °C  $\leq$  T<sub>A</sub>  $\leq$  105 °C, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Symbol              | Characteristic                                                                                                  | Min. | Тур. | Max. | Unit | Notes      |

|---------------------|-----------------------------------------------------------------------------------------------------------------|------|------|------|------|------------|

| nternal regulato    | ors                                                                                                             |      |      | 1    |      |            |

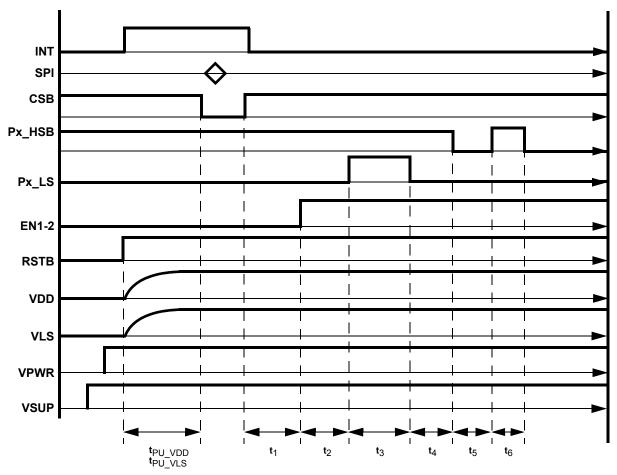

| t <sub>PU_VDD</sub> | $V_{DD}$ power-up time (until INT high) • 8.0 V $\leq$ V <sub>PWR</sub>                                         | _    | _    | 2.0  | ms   | (38), (45) |

| t <sub>PU_VLS</sub> | VLS power-up time • 16 V $\leq$ V <sub>PWR</sub>                                                                | _    | _    | 2.0  | ms   | (39), (45) |

| Charge pump         |                                                                                                                 |      |      |      |      | -1         |

| Fosc                | Charge pump oscillator frequency                                                                                | 90   | 125  | 190  | kHz  |            |

| SR <sub>CP</sub>    | Charge pump slew rate                                                                                           | _    | 100  | _    | V/µs | (40)       |

| Gate drive          |                                                                                                                 |      |      |      |      | 1          |

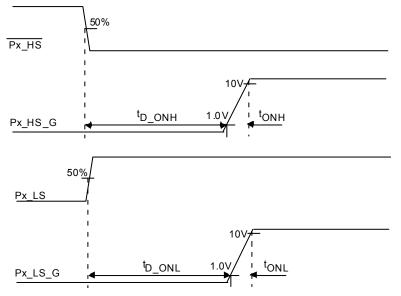

| t <sub>ONH</sub>    | High-side turn on time  • Transition time from 1.0 V to 10 V, load: C = 500 pF, R <sub>G</sub> = 0, (Figure 7)  | -    | 20   | 35   | ns   | (41)       |

| t <sub>D_ONH</sub>  | High-side turn on delay  • Delay from command to 1.0 V, (Figure 7)                                              | 130  | 265  | 386  | ns   | (42)       |

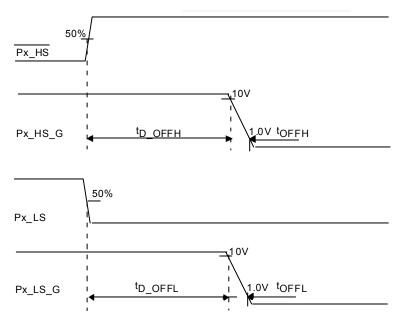

| <sup>t</sup> offh   | High-side turn off time  • Transition time from 10 V to 1.0 V, load: C = 500 pF, R <sub>G</sub> = 0, (Figure 8) | -    | 20   | 35   | ns   | (41)       |

| t <sub>D_OFFH</sub> | High-side turn off delay  • Delay from command to 10 V, (Figure 8)                                              | 130  | 265  | 386  | ns   | (42)       |

| t <sub>ONL</sub>    | Low-side turn on time  • Transition time from 1.0 V to 10 V, load: C = 500 pF, R <sub>G</sub> = 0, (Figure 7)   | -    | 20   | 35   | ns   | (41)       |

| t <sub>D_ONL</sub>  | Low-side turn on delay  • Delay from command to 1.0 V, (Figure 7)                                               | 130  | 265  | 386  | ns   | (42)       |

| t <sub>OFFL</sub>   | Low-side turn off time  • Transition time from 10 V to 1.0 V, load: C = 500 pF, R <sub>G</sub> = 0, (Figure 8)  | -    | 20   | 35   | ns   | (41)       |

| t <sub>D_OFFL</sub> | Low-side turn off delay  • Delay from command to 10 V, (Figure 8)                                               | 130  | 265  | 386  | ns   | (42)       |

| t <sub>D_DIFF</sub> | Same phase command delay match                                                                                  | -20  | 0.0  | +20  | ns   | (43)       |

| t <sub>DUR</sub>    | Thermal filter duration                                                                                         | 8.0  | _    | 30   | μs   | (44)       |

#### Notes

- 38. The power-up time of the IC depends in part on the time required for this regulator to charge up the external filter capacitor on V<sub>DD</sub>.

- 39. The power-up time of the IC depends in part on the time required for this regulator to charge up the external filter capacitors on VLS and VLS\_CAP. This delay includes the expected time for V<sub>DD</sub> to rise.

- 40. The charge pump operating at 12 V  $V_{SYS}$ , 1.0  $\mu F$  pump capacitor, MUR120 diodes and 47  $\mu F$  filter capacitor.

- 41. This parameter is guaranteed by characterization, not production tested.

- 42. These delays include all logic delays except deadtime. All internal logic is synchronous with the internal clock. The total delay includes one clock period for state machine decision block, an additional clock period for fullon mux logic, input synchronization time and output driver propagation delay. Subtract one clock period for operation in fullon mode which bypasses the state machine decision block. Synchronization time accounts for up to one clock period of variation. See Figure 6.

- 43. The maximum separation or overlap of the high and low-side gate drives, due to propagation delays when commanding one on and the other off simultaneously, is guaranteed by design.

- 44. The output of the overtemperature comparator goes through a digital filter before generating a warning or interrupt.

- 45. This specification is based on capacitance of 0.47 μF on VDD, 2.2 μF on VLS and 2.2 μF on VLS\_CAP.

#### 34GD3000

Characteristics noted under conditions 8.0 V  $\leq$  V<sub>PWR</sub> = V<sub>SUP</sub>  $\leq$  48 V, -20 °C  $\leq$  T<sub>A</sub>  $\leq$  105 °C, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Symbol                           | Characteristic                                                                                                                        | Min.   | Тур.   | Max.       | Unit | Notes      |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--------|--------|------------|------|------------|

| Gate drive (cont                 | inued)                                                                                                                                |        |        | ]          |      | 1          |

| t <sub>DC</sub>                  | Duty cycle                                                                                                                            | 0.0    | _      | 96         | %    | (46), (47) |

| t <sub>DC</sub>                  | 100% duty cycle duration                                                                                                              | _      | _      | Unlimited  | s    | (46), (47) |

| t <sub>MAX</sub>                 | Maximum programmable deadtime                                                                                                         | 10.2   | 15     | 19.6       | μs   | (48)       |

| Overcurrent con                  | nparator                                                                                                                              |        |        |            |      |            |

| t <sub>OC</sub>                  | Overcurrent protection filter time                                                                                                    | 0.9    | _      | 3.5        | μs   |            |

| t <sub>ROC</sub>                 | Rise time (OC_OUT)  • 10% - 90%  • C <sub>L</sub> = 100 pF                                                                            | 10     | _      | 240        | ns   |            |

| t <sub>FOC</sub>                 | Fall time (OC_OUT)  • 90% - 10%  • C <sub>L</sub> = 100 pF                                                                            | 10     | -      | 200        | ns   |            |

| Desaturation de                  | tector and phase comparator                                                                                                           |        |        |            |      | •          |

| t <sub>R</sub><br>t <sub>F</sub> | Phase comparator propagation delay time to 50% of $V_{DD}$ ; $C_L \le 100~pF$ • Rising Edge Delay • Falling Edge Delay                | -<br>- | _<br>_ | 200<br>350 | ns   |            |

| t <sub>MATCH</sub>               | Phase comparator match (prop delay mismatch of three phases) • C <sub>L</sub> = 100 pF                                                | -      | _      | 100        | ns   | (46)       |

| t <sub>BLANK</sub>               | Desaturation and phase error blanking time                                                                                            | 4.7    | 7.1    | 9.1        | μs   | (49)       |

| t <sub>FILT</sub>                | Desaturation filter time (filter time is digital)  • Fault must be present for this time to trigger                                   | 640    | 937    | 1231       | ns   | (46)       |

| Current sense a                  | mplifier                                                                                                                              |        |        |            |      |            |

| t <sub>SETTLE</sub>              | Output settle time to 99% • $R_L = 1.0 \text{ k}\Omega$ , $C_L = 500 \text{ pF}$ , 0.3 V < $V_O$ < 4.8 V, Gain = 5 to 15              | -      | 1.0    | 2.0        | μs   | (46), (50) |

| t <sub>IS_RISE</sub>             | Output rise time to 90% • R <sub>L</sub> = 1.0 k $\Omega$ , C <sub>L</sub> = 500 pF, 0.3 V < V <sub>O</sub> < 4.8 V, Gain = 5.0 to 15 | -      | _      | 1.0        | μs   | (51)       |

| t <sub>IS_FALL</sub>             | Output fall time to 10% • R <sub>L</sub> = 1.0 k $\Omega$ , C <sub>L</sub> = 500 pF, 0.3 V < V <sub>O</sub> < 4.8 V, Gain = 5.0 to 15 | -      | _      | 1.0        | μs   | (51)       |

| SR <sub>5</sub>                  | Slew rate at gain = 5.0<br>• $R_L$ = 1.0 $k\Omega$ , $C_L$ = 20 pF                                                                    | 5.0    | _      | -          | V/µs | (46)       |

| f <sub>M</sub>                   | Phase margin at gain = 5.0                                                                                                            | _      | 30     | _          | 0    | (46)       |

| $G_BW$                           | Unity gain bandwidth<br>• $R_L = 1.0 \text{ k}\Omega$ , $C_L = 100 \text{ pF}$                                                        | -      | 20     | _          | MHz  | (46)       |

#### Notes

- 46. This parameter is guaranteed by design, not production tested.

- 47. As duty cycle approaches the limit of 100% or 0% there is a maximum and minimum which is not achievable due to deadtime, propagation delays, switching times and charge time of the bootstrap capacitor (for the high-side FET). 0% is available by definition (FET always off) and unlimited on (100%) is possible as long as gate charge maintenance current is within the trickle charge pump capacity.

- 48. A minimum deadtime of 0.0 can be set via an SPI command. When deadtime is set via a deadtime command, a minimum of 1 clock cycle duration and a maximum of 255 clock cycles is set using the internal time base clock as a reference. Commands exceeding this value limits at this value.

- 49. Blanking time, t<sub>BLANK</sub>, is applied to all phases simultaneously when switching on any output FET. This precludes false errors due to system noise during the switching event.

- 50. Without considering any offsets such as input offset voltage, internal mismatch and assuming no tolerance error in external resistors.

- 51. Rise and fall times are measured from the transition of a step function on the input to 90% of the change in output voltage.

Characteristics noted under conditions 8.0 V  $\leq$  V<sub>PWR</sub> = V<sub>SUP</sub>  $\leq$  48 V, -20 °C  $\leq$  T<sub>A</sub>  $\leq$  105 °C, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Symbol               | Characteristic                                                  | Min.     | Тур. | Max. | Unit  | Notes      |

|----------------------|-----------------------------------------------------------------|----------|------|------|-------|------------|

| Current sense am     | plifier (continued)                                             | <u>"</u> |      | ·    |       |            |

| DW                   | Bandwidth at gain = 15                                          | 2.0      |      |      | NALI- | (52)       |

| $BW_G$               | • $R_L = 1.0 \text{ k}\Omega$ , $C_L = 50 \text{ pF}$           | 2.0      | _    | _    | MHz   | (/         |

|                      | Common mode rejection (CMR) with V <sub>IN</sub>                |          |      |      |       |            |

|                      | • $V_{IN\_CM} = 400 \text{ mV*sin}(2^*\pi^*\text{freq*t})$      |          |      |      |       |            |

|                      | • $V_{IN\_DIF} = 0.0 \text{ V}$ , RS = 1.0 k $\Omega$           |          |      |      |       |            |

| CMR                  | • $R_{FB} = 15 \text{ k}\Omega$ , $V_{REFIN} = 0.0 \text{ V}$   |          |      |      | dB    | (52)       |

|                      | $CMR = 20*log(V_{OUT}/V_{IN\_CM})$                              | 50       |      |      |       |            |

|                      | • Freq = 100 kHz                                                | 50       | _    | _    |       |            |

|                      | • Freq = 1.0 MHz                                                | 40<br>30 | _    | _    |       |            |

|                      | • Freq = 10 MHz                                                 | 30       |      |      |       |            |

| Supervisory and o    |                                                                 |          | ı    | 1    | T     |            |

| t <sub>PROP</sub>    | EN1 and EN2 propagation delay                                   | _        | -    | 280  | ns    |            |

| t <sub>RINT</sub>    | INT rise time CL = 100 pF                                       | 10       | _    | 250  | ns    |            |

| t <sub>FINT</sub>    | INT fall time CL = 100 pF                                       | 10       | _    | 200  | ns    |            |

| t <sub>PROPINT</sub> | INT propagation time                                            | -        | _    | 250  | ns    |            |

| t <sub>TRRST</sub>   | RST transition time (rise and fall)                             | -        | _    | 1.25 | μs    | (52), (53) |

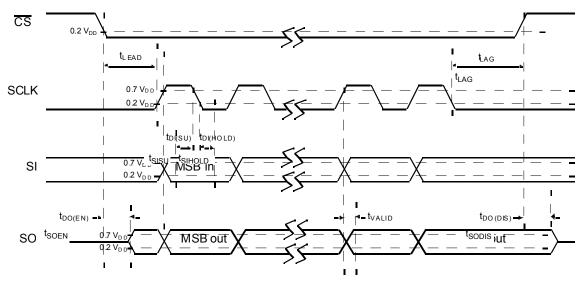

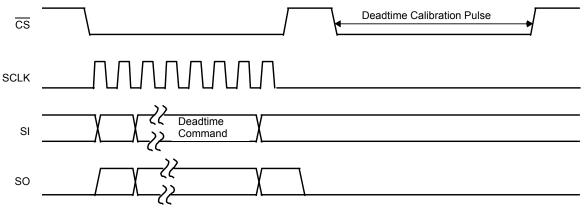

| SPI interface timir  | ng                                                              |          |      |      |       |            |

| f <sub>OP</sub>      | Maximum frequency of SPI operation                              | _        |      | 4.0  | MHz   |            |

| f <sub>TB</sub>      | Internal time base                                              | 13       | 17   | 25   | MHz   |            |

| TC <sub>TB</sub>     | Internal time base drift from value at 25 °C                    | -5.0     | _    | 5.0  | %     | (54)       |

| t <sub>LEAD</sub>    | Falling edge of CS to rising edge of SCLK (required setup time) | 100      | _    | -    | ns    | (54)       |

| t <sub>LAG</sub>     | Falling edge of SCLK to rising edge of CS (required setup time) | 100      | _    | -    | ns    | (54)       |

| t <sub>sısu</sub>    | SI to falling edge of SCLK (required setup time)                | 25       | _    | -    | ns    | (54)       |

| t <sub>SIHOLD</sub>  | Falling edge of SCLK to SI (required setup time)                | 25       | _    | -    | ns    | (54)       |

| t <sub>RSI</sub>     | SI, CS, SCLK signal rise time                                   | -        | 5.0  | -    | ns    | (54), (55) |

| t <sub>FSI</sub>     | SI, CS, SCLK signal fall time                                   | -        | 5.0  | -    | ns    | (54), (55) |

| t <sub>SOEN</sub>    | Time from falling edge of CS to SO low-impedance                | -        | 55   | 100  | ns    | (54), (56) |

| t <sub>SODIS</sub>   | Time from rising edge of CS to SO high-impedance                | _        | 100  | 125  | ns    | (54), (57) |

| t <sub>VALID</sub>   | Time from rising edge of SCLK to SO data valid                  | -        | 80   | 125  | ns    | (54), (58) |

| t <sub>DT</sub>      | Time from rising edge of CS to falling edge of the next CS      | 200      | _    | _    | ns    | (54)       |

#### Notes

- 52. This parameter is guaranteed by design, not production tested.

- 53.  $t_{TRRST}$  is given as a design guideline. The bounds for this specification are VPWR  $\leq$  58 V, total capacitance on VLS > 1.0  $\mu$ F.

- 54. This parameter is guaranteed by design, not production tested.

- 55. Rise and Fall time of incoming SI, CS, and SCLK signals suggested for design consideration to prevent the occurrence of double pulsing.

- $\,$  56.  $\,$  Time required for valid output status data to be available on SO pin.

- 57. Time required for output states data to be terminated at SO pin.

- $58. \quad \text{Time required to obtain valid data out from SO following the rise of SCLK with 200 pF load. } \\$

#### 34GD3000

# 4.4 Timing diagrams

Figure 4. SPI interface timing

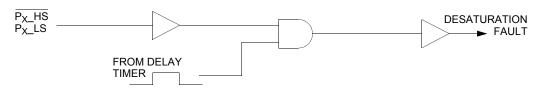

Figure 5. Desaturation blanking and filtering detail

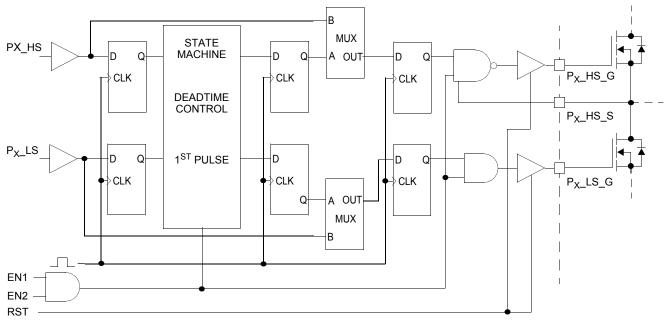

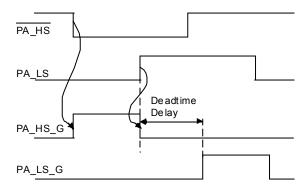

Figure 6. Deadtime control delays

Figure 7. Driver turn-on time and turn-on delay

Figure 8. Driver turn-off time and turn-off delay

18

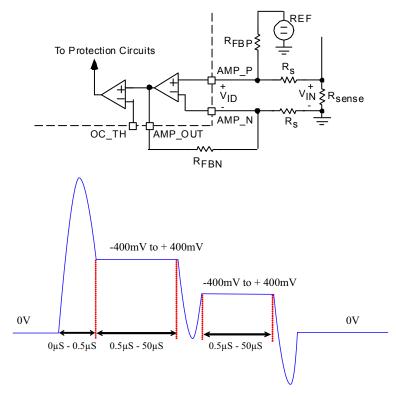

Figure 9. Current amplifier and input waveform (V $_{\rm IN}$  voltage across R $_{\rm SENSE}$ )

Figure 10. Typical amplifier open-loop gain and phase vs. frequency

### 5 Functional descriptions

#### 5.1 Introduction

The 34GD3000 provides an interface between an MCU and the external FETs used to drive three phase motors. A typical external FET may have an on resistance of 4.0 m $\Omega$  or less and could require a gate charge of over 400 nC to fully turn on. The IC can operate in 12 V to 48 V environments.

There are many methods for controlling three phase motor systems, so the IC enforces few constraints in driving the FETs. The 34GD3000 does however provide deadtime (cross-over) blanking and logic in order to protect the external FETs. Under special configurations, both of these features can be overridden, allowing both FETs in a phase to be simultaneously enabled.

An SPI port is used to configure the 34GD3000's modes.

### 5.2 Functional pin description

#### 5.2.1 Phase A (PHASEA)

This pin is the totem pole output of the Phase A comparator. This output is low when the voltage on Phase A high-side source (source of the high-side load FET) is less than 50 percent of  $V_{SUP}$ .

#### 5.2.2 Power ground (PGND)

This pin is power ground for the charge pump. It should be connected to VSS, however routing to a single point ground on the PCB may help to isolate charge pump noise.

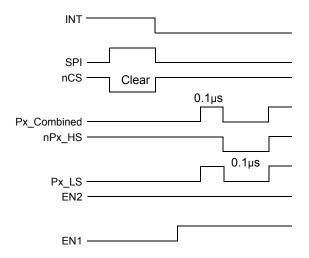

### **5.2.3 Enable 1 and Enable 2 (EN1, EN2)**

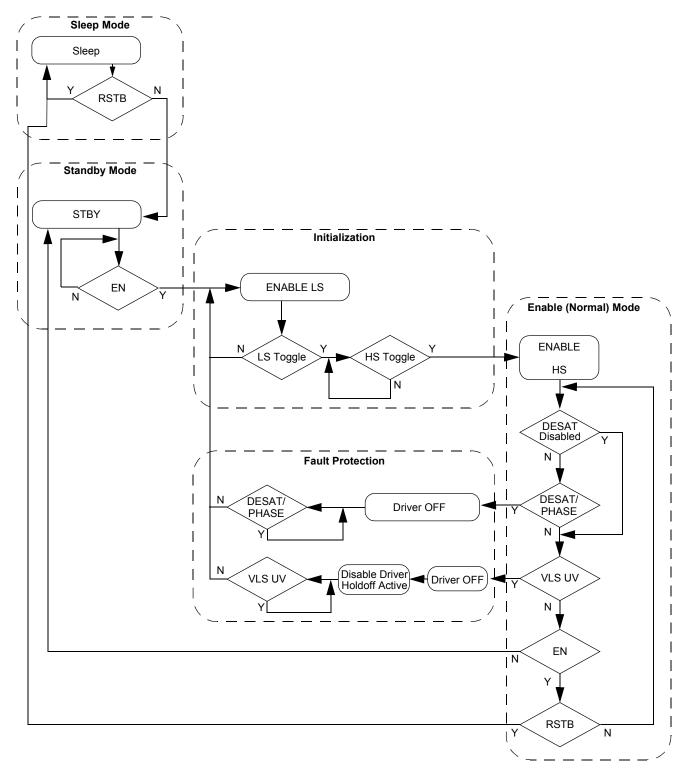

Both of these logic signal inputs must be high to enable any gate drive output. When either or both are low, the internal logic (SPI port, etc.) still functions normally, but all gate drives are forced off (external power FET gates pulled low). The signal is asynchronous. When EN1 and EN2 return high to enable the outputs, each LS driver must be pulsed on before the corresponding HS driver can be commanded on. This ensures the bootstrap capacitors are charged. See Initialization requirements on page 39.

### 5.2.4 Reset (RST)

When the reset pin is low the integrated circuit (IC) is in a low-power state. In this mode all outputs are disabled, internal bias circuits are turned off, and a small pull-down current is applied to the output gate drives. The internal logic resets within 77 ns of RESET going low. When RST is low, the IC consumes minimal current.

### 5.2.5 Charge pump out (PUMP)

This pin is the switching node of the charge pump circuit. The output of the internal charge pump support circuit. When the charge pump is used, it is connected to the external pumping capacitor. This pin may be left floating if the charge pump is not required.

### 5.2.6 Charge pump input (VPUMP)

This pin is the input supply for the charge pump circuit. When the charge pump is required, this pin should be connected to a polarity protected supply. This input should never be connected to a supply greater than 40 V. If the charge pump is not required this pin may be left floating.

### 5.2.7 VSUP input (VSUP)

The supply voltage pin should be connected to the common connection of the high-side FETs. It is the reference bias for the phase comparators and desaturation comparator. It is also used to provide power to the internal steady state trickle charge pump and to energize the hold off circuit.

### 5.2.8 Phase B (PHASEB)

This pin is the totem pole output of the Phase B comparator. This output is low when the voltage on Phase B high-side source (source of the high-side load FET) is less than 50 percent of  $V_{SUP}$ .

#### 5.2.9 Phase C (PHASEC)

This pin is the totem pole output of the Phase C comparator. This output is low when the voltage on Phase C high-side source (source of the high-side load FET) is less than 50 percent of V<sub>SUP</sub>.

### 5.2.10 Phase A high-side input (PA\_HS)

This input logic signal pin enables the high-side driver for Phase A. The signal is active low and is pulled up by an internal current source.

### 5.2.11 Phase A low-side input (PA\_LS)

This input logic signal pin enables the low-side driver for Phase A. The signal is active high and is pulled down by an internal current sink.

#### 5.2.12 VDD voltage regulator (VDD)

VDD is an internally generated 5.0 V supply. The internal regulator provides continuous power to the IC and is a supply reference for the SPI port. A 0.47 µF (min) decoupling capacitor must be connected to this pin. This regulator is intended for internal IC use and can supply only a small (1.0 mA) external load current.

A power-on-reset (POR) circuit monitors this pin and until the voltage rises above the threshold, the internal logic is reset; driver outputs is tri-stated and SPI communication disabled. The VDD regulator can be disabled by asserting the RST signal low. The VDD regulator is powered from the VPWR pin.

### 5.2.13 Phase B high-side control input (PB\_HS)

This pin is the input logic signal, enabling the high-side driver for Phase B. The signal is active low, and is pulled up by an internal current source.

### 5.2.14 Phase B low-side input (PB\_LS)

This pin is the input logic signal, enabling the low-side driver for Phase B. The signal is active high, and is pulled down by an internal current sink.

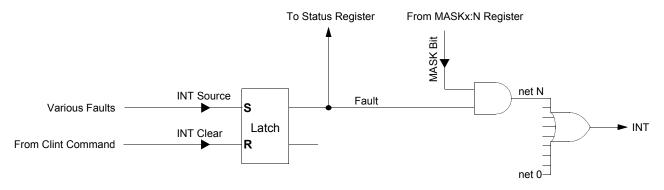

### 5.2.15 Interrupt (INT)

The INTERRUPT pin is a totem pole logic output. When a fault is detected, this pin pulls high until it is cleared by executing the clear interrupt command via the SPI port. The faults capable of causing an interrupt can be masked via the MASK0 and MASK1 SPI registers to customize the response.

### **5.2.16 Chip select (CS)**

Chip select is a logic input which frames the SPI commands and enables the SPI port. This signal is active low, and is pulled up by an internal current source.

### 5.2.17 **Serial in (SI)**

The SERIAL IN pin is used to input data to the SPI port. Clocked on the falling edge of SCLK, it is the most significant bit (MSB) first. This pin is pulled down by an internal current sink.

### 5.2.18 Serial clock (SCLK)

This logic input is the clock is used for the SPI port. The SCLK typically runs at 3.0 MHz (up to 5.0 MHz) and is pulled down by an internal current sink.

34GD3000

#### **5.2.19** Serial out (SO)

Output data for the SPI port streams from this pin. It is tri-stated until CS is low. New data appears on rising edges of SCLK in preparation for latching by the falling edge of SCLK on the master.

### 5.2.20 Phase C low-side input (PC\_LS)

This input logic pin enables the low-side driver for Phase C. This pin is an active high, and is pulled down by an internal current sink.

#### 5.2.21 Phase C high-side input (PC\_HS)

This input logic pin enables the high-side driver for Phase C. This signal is active low, and is pulled up by an internal current source.

### 5.2.22 Amplifier output (AMP\_OUT)

This pin is the output for the current sensing amplifier. It is also the sense input to the overcurrent comparator.

### 5.2.23 Amplifier inverting input (AMP\_N)

The inverting input to the current sensing amplifier.

### 5.2.24 Amplifier non-inverting input (AMP\_P)

The non-inverting input to the current sensing amplifier.

### 5.2.25 Overcurrent comparator output (OC\_OUT)

The overcurrent comparator output is a totem pole logic level output. A logic high indicates an overcurrent condition.

### 5.2.26 Overcurrent comparator threshold (OC\_TH)

This input sets the threshold level of the overcurrent comparator.

### 5.2.27 Voltage source supply (VSS)

VSS is the ground reference for the logic interface and power supplies.

### 5.2.28 **Ground (GND0,GND1)**

These two pins are connected internally to VSS by a 1.0  $\Omega$  resistor. They provide device substrate connections and the primary return path for ESD protection.

### 5.2.29 VLS regulator capacitor (VLS\_CAP)

This connection is for a capacitor which provides a low-impedance for switching currents on the gate drive. A low ESR decoupling capacitor, capable of sourcing the pulsed drive currents must be connected between this pin and VSS. This is the same DC node as VLS, but it is physically placed on the opposite end of the IC to minimize the source impedance to the gate drive circuits.

### 5.2.30 Phase C low-side source (PC\_LS\_S)

The phase C low-side source is the pin used to return the gate currents from the low-side FET. Best performance is realized by connecting this node directly to the source of the low-side FET for phase C.

### 5.2.31 Phase C low-side gate (PC\_LS\_G)

This is the gate drive for the Phase C low-side output FET. It provides high-current through a low-impedance to turn on and off the low-side FET. A low-impedance drive ensures transient currents do not overcome an off-state driver and allow pulses of current to flow in the external FET. This output has also been designed to resist the influence of negative currents.

#### 5.2.32 Phase C high-side source (PC\_HS\_S)

The source connection for the Phase C high-side output FET is the reference voltage for the gate drive on the high-side FET and also the low-voltage end of the bootstrap capacitor.

### 5.2.33 Phase C high-side gate (PC\_HS\_G)