# **R&E** INTERNATIONAL, INC.

#### **FEATURES**

- Serial data input

- Active parallel output

- Storage register capability

- Master clear

- Can function as demultiplexer

#### **APPLICATIONS**

- Multi-line decoders

- A/D converters

#### DESCRIPTION

The 4099B 8-bit addressable latch is a serial-input, paralleloutput storage register that can perform a variety of functions.

Data are inputted to a particular bit in the latch when that bit is addressed (by means of inputs A0, A1, A2) and when WRITE DISABLE is at a low level. When WRITE DISABLE is high, data entry is inhibited; however, all 8 outputs can be continuously read independent of WRITE DISABLE and address inputs.

A master RESET input is available, which resets all bits to a logic "0" level when RESET and WRITE DISABLE are at a high level. When RESET is at a high level, and WRITE DISABLE is at a low level, the latch acts as a 1-of-8 demultiplexer; the bit that is addressed has an active output which follows the data input, while all unaddressed bits are held to a logic "0" level.

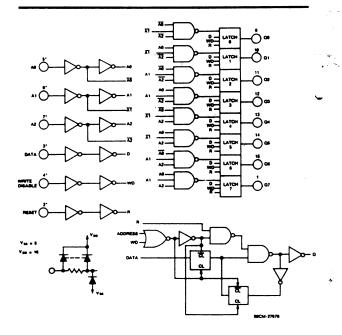

#### **LOGIC DIAGRAM**

# 8-BIT ADDRESSABLE LATCH

#### **TRUTH TABLE**

| WD | R | Addresse<br>Latch | d Unaddressed<br>Latch |

|----|---|-------------------|------------------------|

| 0  | 0 | D                 | Holds previous data    |

| 0  | 1 | D                 | 0                      |

| 1  | 0 | Holds previou     | s data                 |

| 1  | 1 | 0                 | 0                      |

## **TIMING DIAGRAMS**

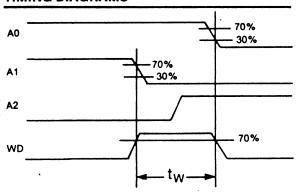

Fig.1 — Definition of WRITE DISABLE ON time.

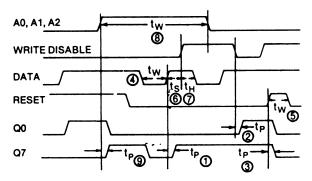

Fig. 2 — Master timing diagram.

# **ELECTRICAL CHARACTERISTICS**

# STATIC CHARACTERISTICS 1, 2

|                                 | V               | ILOW2 |         | + 25°C |              |         | Тнідн |            | 11-14- |

|---------------------------------|-----------------|-------|---------|--------|--------------|---------|-------|------------|--------|

| PARAMETER                       | V <sub>DD</sub> | Min.  | Max.    | Min.   | Тур.         | Max.    | Min.  | Max.       | Units  |

| QUIESCENT DEVICE IDD<br>CURRENT | 5<br>10         | _     | 5<br>10 | _      | 0.02<br>0.02 | 5<br>10 | _     | 150<br>300 | μΑ     |

|                                 | 15              | _     | 20      |        | 0.02         | 20      |       | 600        |        |

### DYNAMIC CHARACTERISTICS

$T_A = 25^{\circ} C$ ,  $C_L = 50 pF$ , Input  $t_r$ ,  $t_f = 20 ns$ ,  $R_L = 200 K$

| CHARACTERISTIC                                                             | SEE<br>FIG 2* | V <sub>DD</sub> | LIMI<br>ALL PACKA<br>TYP. | UNITS             |    |

|----------------------------------------------------------------------------|---------------|-----------------|---------------------------|-------------------|----|

| Propagation Delay: t <sub>PLH</sub> , t <sub>PHL</sub>                     | (1)           | 5<br>10<br>15   | 200<br>75<br>50           | 400<br>150<br>100 |    |

| Data to Output WRITE DISABLE to Output. t <sub>PLH,</sub> t <sub>PHL</sub> | 2             | 5<br>10<br>15   | 200<br>80<br>60           | 400<br>160<br>120 | ns |

| Reset to Output,                                                           | 3             | 5<br>10<br>15   | 175<br>80<br>65           | 350<br>160<br>130 |    |

| Address to Output,<br>t <sub>PLH,</sub><br>t <sub>PHL</sub>                | 9             | 5<br>10<br>15   | 225<br>100<br>75          | 450<br>200<br>150 |    |

| Transition Time, T <sub>THL,</sub><br>(Any Output) t <sub>TLH</sub>        |               | 5<br>10<br>15   | 100<br>50<br>40           | 200<br>100<br>80  | ns |

| Minimum Pulse<br>Width, t <sub>W</sub><br>Data                             | 4             | 5<br>10<br>15   | 100<br>50<br>40           | 200<br>100<br>80  | ns |

| Address                                                                    | 8             | 5<br>10<br>15   | 200<br>100<br>65          | 400<br>200<br>125 | ns |

| Reset                                                                      | 5             | 5<br>10<br>15   | . 75<br>40<br>25          | 150<br>75<br>50   | ns |

| Minimum Setup<br>Time, t <sub>S</sub><br>Data to WRITE DISABLE             | 6             | 5<br>10<br>15   | 50<br>25<br>20            | 100<br>50<br>35   | ns |

| Minimum Hold<br>Time, t <sub>H</sub><br>Data to WRITE DISABLE              | 7             | 5<br>10<br>15   | 75<br>40<br>25            | 150<br>75<br>50   | ns |

| Average Input Capacitano<br>C <sub>1</sub>                                 | e<br>Any In   | put             | 5                         |                   | pF |

<sup>\*</sup>Circled numbers refer to times indicated on master timing diagram.

Note: In addition to the above characteristics, a WRITE DISABLE ON time (the time that WRITE DISABLE is at a high level) must be observed during an address change for the total time that the external address lines A0, A1, and A2 are settling to a stable level, to prevent a wrong cell from being addressed (see Fig. 1).