PRODUCT PREVIEW - May 18, 2018

# **Features and Benefits**

- Supply voltage: 4.75 V to 5.25 V

- Supply and output protection: -18/+35 V

- Simultaneous signal processing for two sensors

- Fully digital calibration; no external trim components

- Tool set provided for application support

- Optimized for resistive sensor bridges

- Sensitivity range: 3 112 mV/V

- 10-step coarse gain trimming

- 31-step coarse offset trimming to  $\pm 4^*$  input span

- Low noise input with 15-bit ADC

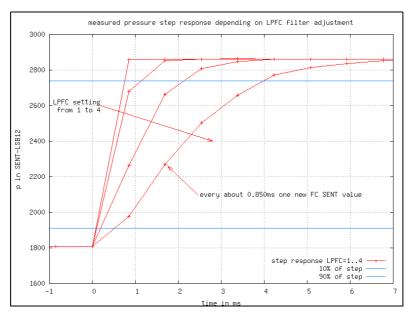

- Configurable digital low-pass: 13Hz ... 1.1kHz

- Additional NTC channel with on-chip linearization

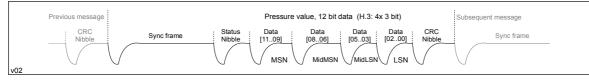

- 12-bit output via configurable SENT interface

- Configurable SENT output; same pin providing single-wire programming interface

- I<sup>2</sup>C interface for fast access to sensor/configuration/calibration data

- Developed acc. to ISO26262 with safety requirements rated up to ASIL C

# Applications

- Automotive sensor applications

- · Safety applications, e.g. braking systems

- General MEMS p-sensor applications

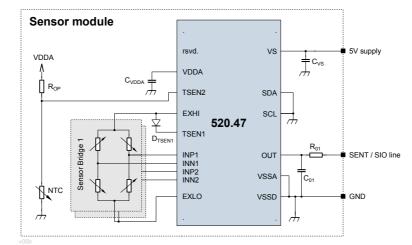

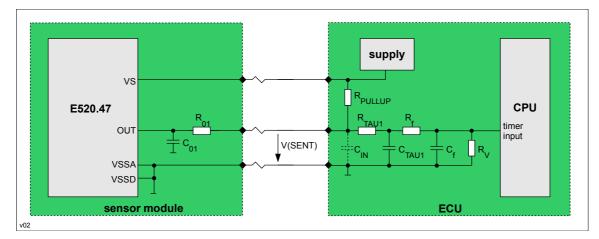

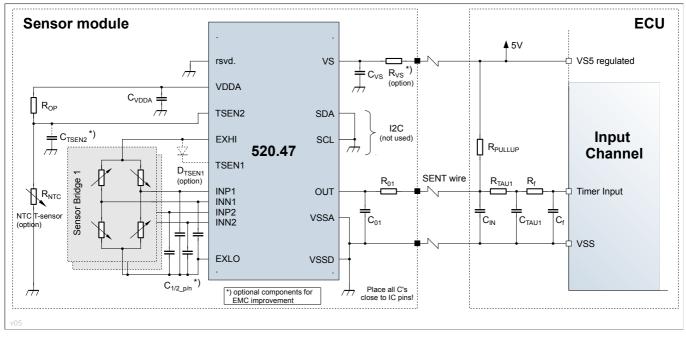

Typical Operating Circuit

· Conditioning of resistive bridge sensors

# **General Description**

This IC provides low-noise sensor signal conditioning with two individual 15-bit Delta-Sigma ADCs for two resistive bridge sensors, including compensation and linearization. Two additional temperature channels with a 14-bit Delta-Sigma ADC allow for precise acquisition and linearization of divers temperature sensors. Internal sensor- and self-diagnosis, particular safety requirements and the development compliant to ISO26262 enable the integration of this IC into safety applications.

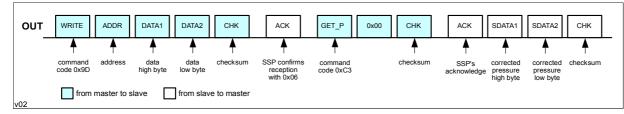

All compensated and linearized sensor data are available at the digital SENT interface output. The dual function SENT pin permits a serial I/O communication to enable real 3-wire end-of-line configuration and calibration.

Alternatively an additional I<sup>2</sup>C interface allows faster access to sensor, diagnosis, calibration and configuration data.

A calibration tool set including a bench top evaluation software is provided to facilitate sensor mass production.

# **Ordering Information**

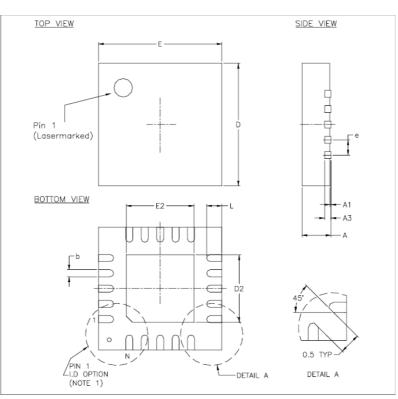

| Order Code                                    | Temperature Range | Package |  |  |  |  |

|-----------------------------------------------|-------------------|---------|--|--|--|--|

| E52047A52C                                    | -40°C to +140°C   | QFN20L4 |  |  |  |  |

| E52047A24Y                                    | -40°C to +150°C   | Die *   |  |  |  |  |

| * Contact factory for hare die specifications |                   |         |  |  |  |  |

Contact factory for bare die specifications

This document contains information on a product under development. Elmos Semiconductor AG reserves the right to change or discontinue this product without notice

# elmos"

compliant

PRODUCT PREVIEW - May 18, 2018

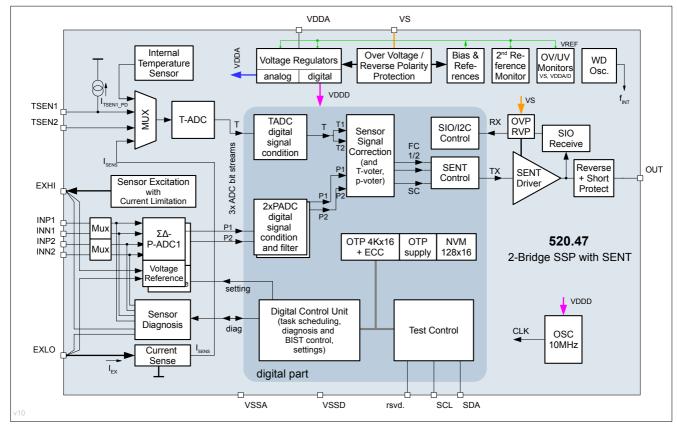

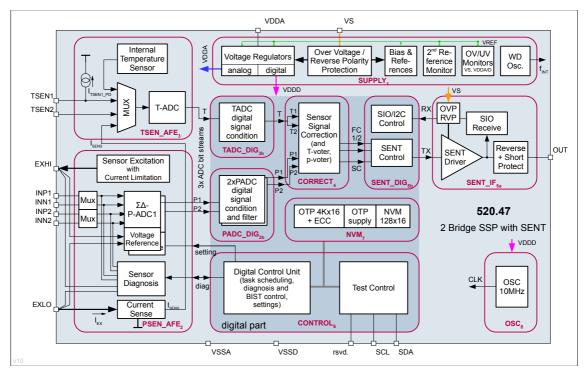

# **Functional Diagram**

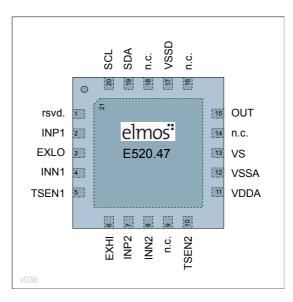

# **Pin Configuration**

PRODUCT PREVIEW – May 18, 2018

# **Pin Description**

|    | Name     | Туре    | Description                                                                                                    |

|----|----------|---------|----------------------------------------------------------------------------------------------------------------|

| 1  | reserved |         | Internally connected. Reserved for factory use, connect to VSSD.                                               |

| 2  | INP1     | A_I     | sensor voltage input 1, positive                                                                               |

| 3  | EXLO     | A_O     | sensor excitation voltage output, negative                                                                     |

| 4  | INN1     | A_I     | sensor voltage input 1, negative                                                                               |

| 5  | TSEN1    | A_I     | external diode type temperature sensor input 1, connect to EXHI if not used                                    |

| 6  | EXHI     | A_O     | sensor excitation voltage output, positive                                                                     |

| 7  | INP2     | A_I     | sensor voltage input 2, positive                                                                               |

| 8  | INN2     | A_I     | sensor voltage input 2, negative                                                                               |

| 9  | n.c.     |         | Not connected. Leave open.                                                                                     |

| 10 | TSEN2    | A_I     | external RTD type temperature sensor input 2,<br>leave pin open if not used                                    |

| 11 | VDDA     | A_0     | internal analogue voltage supply output,<br>external connections only acc. to recommended operating conditions |

| 12 | VSSA     | S       | supply ground, analogue                                                                                        |

| 13 | VS       | HV_S    | main supply input                                                                                              |

| 14 | n.c.     |         | Not connected. Leave open.                                                                                     |

| 15 | OUT      | HV_D_IO | SENT data output /<br>Serial IO programming interface                                                          |

| 16 | n.c.     |         | Not connected. Leave open.                                                                                     |

| 17 | VSSD     | S       | supply ground, digital                                                                                         |

| 18 | n.c.     |         | Not connected. Leave open.                                                                                     |

| 19 | SDA      | D_IO    | I2C data I/O,<br>connect to VSSD if not used                                                                   |

| 20 | SCL      | D_I     | I2C clock input,<br>connect to VSSD if not used                                                                |

| 21 | EP       | S       | exposed die pad; connect to VSSA on PCB                                                                        |

Note: A = Analogue, D = Digital, S = Supply, I = Input, O = Output, IO = Bidirectional, HV = High Voltage

PRODUCT PREVIEW - May 18, 2018

# **1 Absolute Maximum Ratings**

Stresses beyond these absolute maximum ratings listed below may cause permanent damage to the device. These are stress ratings only; operation of the device at these or any other conditions beyond those listed in the operational sections of this document is not implied. Exposure to absolute maximum rated conditions for extended periods may affect device reliability. All voltages referred to VSSA. Currents flowing into terminals are positive, those drawn out of a terminal are negative.

| No. | Description                                                              | Condition | Symbol               | Min  | Max  | Unit |

|-----|--------------------------------------------------------------------------|-----------|----------------------|------|------|------|

| 1   | supply voltage at pin VS                                                 |           | V <sub>VS</sub>      | -18  | +35  | V    |

| 2   | voltage at data output pin OUT                                           |           | V <sub>OUT</sub>     | -18  | +35  | V    |

| 3   | voltage at output pin VDDA                                               |           | V <sub>VDDA</sub>    | -0.3 | +5.5 | V    |

| 4   | voltage at sensor inputs pins INP1, INN1, INP2<br>and INN2 <sup>1)</sup> |           | V <sub>AIN</sub>     | -0.3 | +5.5 | V    |

| 5   | voltage at sensor excitation pin EXHI <sup>1)</sup>                      |           | V <sub>EXHI</sub>    | -0.3 | +5.5 | V    |

| 6   | voltage at sensor ground pin EXLO                                        |           | V <sub>EXLO</sub>    | -0.3 | +0.6 | V    |

| 7   | voltage at pin VSSD                                                      |           | V <sub>VSSD</sub>    | -0.3 | +0.3 | V    |

| 8   | voltage at temperature sensor inputs pins TSEN1 and TSEN2 <sup>1)</sup>  |           | V <sub>TSEN1,2</sub> | -0.3 | +5.5 | V    |

| 9   | voltage at digital input SCL, SDA                                        |           | V <sub>DIG_IO</sub>  | -0.3 | +5.5 | V    |

| 10  | current at output pin OUT                                                |           | I <sub>OUT</sub>     | -10  | +10  | mA   |

| 11  | current at pin VDDA                                                      |           | I <sub>VDDA</sub>    | -20  | +5   | mA   |

| 12  | current at sensor inputs pins INP1, INN1, INP2<br>and INN2               |           | I <sub>AIN</sub>     | -5   | +5   | mA   |

| 13  | current at pin EXHI                                                      |           | I <sub>EXHI</sub>    | -10  | +5   | mA   |

| 14  | current at pin EXLO                                                      |           | I <sub>EXLO</sub>    | -5   | +10  | mA   |

| 15  | current at pins TSEN1, TSEN2                                             |           | I <sub>TSEN1,2</sub> | -5   | +5   | mA   |

| 16  | current at digital IOs SCL, SDA                                          |           | I <sub>DIG_IO</sub>  | -10  | +5   | mA   |

| 17  | storage temperature <sup>2)</sup>                                        |           | T <sub>ST</sub>      | -40  | 150  | °C   |

| 18  | junction temperature <sup>3)</sup>                                       |           | TJ                   | -40  | 150  | °C   |

#### Table 1-1: Maximum Ratings

<sup>1)</sup> Maximum limit: Whatever voltage is lower: 5.5V or V<sub>VDDA</sub>+0.3V. <sup>2)</sup> See 4.7-1 for a permissible temperature profile to ensure NVM data retention.

For moisture sensitive devices refer to JEDEC standard J-STD-033 for details of handling and usage. Storage at temperatures > 90°C for more than 96 h may affect the solderability of the devices. Storage is not considering any packing materials such as tapes, reels, dry packs, foils etc. <sup>3)</sup> See 4.7-1 for a permissible temperature profile to ensure NVM data retention.

PRODUCT PREVIEW - May 18, 2018

# 2 ESD

Table 2-1: ESD Level Definition

| Description                                                             | Condition | Symbol                   | Min  | Мах | Unit |

|-------------------------------------------------------------------------|-----------|--------------------------|------|-----|------|

| ESD HBM protection<br>at system level pins only: OUT, VS,<br>VSSD, VSSA | 1)        | V <sub>ESD(HBM)SYS</sub> | -4   | 4   | kV   |

| ESD HBM protection at all pins                                          | 2)        | V <sub>ESD(HBM)</sub>    | -2   | 2   | kV   |

| ESD CDM protection at all pins                                          | 3)        | V <sub>ESD(CDM)</sub>    | -500 | 500 | V    |

| ESD CDM protection at edge pins                                         | 3)        | V <sub>ESD(CDM)C</sub>   | -750 | 750 | V    |

<sup>1)</sup>According to AEC-Q100-002 (HBM) chip level test; system level pins are OUT, VS, VSSD, VSSA <sup>2)</sup>According to AEC-Q100-002 (HBM) chip level test; all other pins <sup>3)</sup>According to AEC-Q100-011 (CDM) chip level test

PRODUCT PREVIEW - May 18, 2018

# **3 Recommended Operating Conditions**

Table 3-1: Recommended Operating Conditions

| No. | Description                                                                                                      | Condition                                                       | Symbol                     | Min   | Тур  | Max   | Unit                    |

|-----|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|----------------------------|-------|------|-------|-------------------------|

| 1   | supply voltage at pin VS                                                                                         |                                                                 | V <sub>vs</sub>            | 4.75  | 5.00 | 5.25  | V                       |

| 2   | input voltage range for pins EXHI, INN1,<br>INP1, INN2, INP2, TSEN1, TSEN2 <sup>1)</sup>                         |                                                                 | V <sub>SEN</sub>           | 0     | -    | 1     | V <sub>VDDA</sub>       |

| 3   | input voltage range for pin EXLO                                                                                 |                                                                 | V <sub>EXLO</sub>          | 0     | -    | 0.11  | V <sub>EXHI</sub>       |

| 4   | ambient temperature                                                                                              | in QFN20L4                                                      | T <sub>A</sub>             | -40   | -    | 140   | °C                      |

| 5   | external load at regulator at pin VDDA <sup>2)</sup>                                                             | at pin VDDA                                                     | IVDDA_EXT_LD               | -1.5  | -    | 0     | mA                      |

| 6   | DC current at pin OUT                                                                                            | DC                                                              | Ι <sub>ουτ</sub>           | -1.2  | -    | +1.2  | mA                      |

| 7   | buffer capacitor at VS                                                                                           | close to pin                                                    | C <sub>VS</sub>            | 80    | 100  | 250   | nF                      |

| 8   | bypass capacitor at VDDA                                                                                         | close to pin                                                    | C <sub>VDDA</sub>          | 80    | 100  | 120   | nF                      |

| 9   | diode sensor parameters                                                                                          |                                                                 |                            |       |      |       |                         |

| 10  | forward voltage of external temperature sensing diode at TSEN1(2)                                                | I <sub>F</sub> =20μΑ                                            | V <sub>F_DIO</sub>         | 0.2   | -    | 1.1   | V                       |

| 11  | linear TC of forward voltage of external diode at TSEN1                                                          | I <sub>F</sub> =20μΑ                                            | $TC_{VF}$                  | -2.3  | -2.0 | -1.7  | mV/K                    |

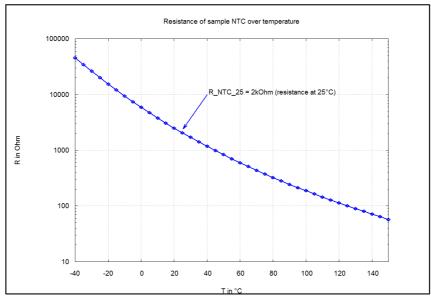

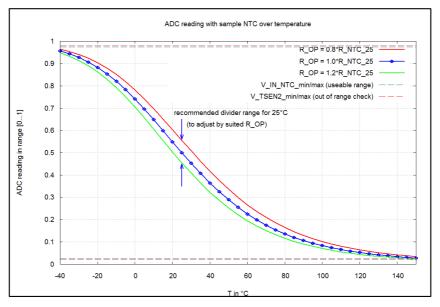

| 12  | NTC sensor parameters                                                                                            |                                                                 |                            |       |      |       |                         |

| 13  | optional filter capacitor at TSEN2 <sup>3)</sup>                                                                 | close to pin                                                    | C <sub>TSEN2</sub>         | -     | 10   | 13    | nF                      |

| 14  | load resistor for NTC resistor divider <sup>4)</sup>                                                             |                                                                 | R <sub>OP</sub>            | 0.8   | -    | 1.2   | R <sub>NTC_25</sub>     |

| 15  | NTC resistance at room temperature                                                                               | R <sub>NTC</sub> (T=25°C)                                       | R <sub>NTC_25</sub>        | 2     | -    | 10    | kΩ                      |

| 16  | usable input range for NTC divider at pin TSEN2 <sup>5)</sup>                                                    |                                                                 | V <sub>IN_NTC</sub>        | 2.5   | -    | 97.5  | %<br>VDDA               |

| 17  | sensor bridge parameters                                                                                         |                                                                 |                            |       |      |       |                         |

| 18  | capacitance from pins INP1, INN1, INP2 or INN2 to GND <sup>6)</sup>                                              |                                                                 | $C_{\text{IN}_{GND}}$      | -     | -    | 130   | pF                      |

| 19  | common mode input voltage at sensor<br>inputs INP1/INN1 and INP2/INN2 <sup>7)</sup>                              | 0.5*(V <sub>INP</sub> +V <sub>INN</sub> )-<br>V <sub>EXLO</sub> | V <sub>IN_CM</sub>         | 0.40  | 0.50 | 0.60  | V <sub>EX</sub>         |

| 20  | single ended input voltage at sensor inputs INP1/INN1 and INP2/INN2 to avoid dia-<br>gnosis errors <sup>8)</sup> |                                                                 | $V_{\text{IN}\_\text{BR}}$ | 0.35  | -    | 0.65  | V <sub>EX</sub>         |

| 21  | sensor bridge resistance (EXHI to EXLO) <sup>9)</sup>                                                            | bridges parallel                                                | R <sub>BR</sub>            | 0.9   | -    | 12    | kΩ                      |

| 22  | sensor bridge resistance of each of one or two bridges to avoid diagnosis errors <sup>10)</sup>                  | (each) single<br>bridge                                         | $R_{BR\_single}$           | 0.9   | -    | 12    | kΩ                      |

| 23  | linear TC of bridge resistance in case of temperature sensing via bridge current                                 |                                                                 |                            | 1600  | -    | 5000  | <sup>ppM</sup> /K       |

| 24  | 2nd order TC of bridge resistance in case of temperature sensing via bridge current                              |                                                                 | TCR <sub>BR_2nd</sub>      | 0     | -    | 1/300 | TCR <sub>BR</sub><br>/K |

| 25  | sensitivity of sensor bridge (including TC) <sup>11)</sup>                                                       | (full scale span)                                               | S <sub>IN</sub>            | 3     | -    | 84    | mV <sub>pp</sub> /V     |

| 26  | sensor bridge offset                                                                                             |                                                                 | OFF                        | -3.75 |      | +4.00 | SIN                     |

<sup>1)</sup> This condition includes already error conditions at listed pins. For proper sensor operation narrower ranges are necessary, see further operating conditions.

<sup>2)</sup> Higher current at VDDA pin possible, as long as sum  $|I_{VDDA\_EXT\_LD}| + |I_{EXHI\_pin}| < 5.5mA$ . <sup>3)</sup> C<sub>TSEN2</sub> for filtering and EMC reasons. Suited value has to be chosen depending on specific application conditions. In very disturbed environments more sophisticated EMC filter circuitry may be necessary.

Note: If a capacitor is used, the ADC input charging is incomplete and average input current at pin TSEN2 produces following voltage drop ITSEN2 RNTC ||ROP as input voltage error. This may cause at very low temperatures additional errors in temperature reading, especially with high NTC impedance values.

PRODUCT PREVIEW - May 18, 2018

<sup>4)</sup> Selection of R<sub>OP</sub> so that NTC resistor divider is at about 50% in the middle of temperature range is optimal for ADC resolution (for example R<sub>OP</sub>= R<sub>NTC</sub>(55°C)). Self-heating of NTC and current consumption should be considered too, so that higher R<sub>OP</sub> can be the better choice.

<sup>5)</sup> Range limited due to limits of "out of range" diagnosis and necessary precision for NTC formula linerization.

<sup>6)</sup> For EMC reasons a capacitance from input pins to ground may be necessary. For that case this limit should be fulfilled. It is necessary to ensure function of sensor open test. Care about symmetric capacitive load at corresponding input pins.

If larger EMC capacitors at these pins needed the sensor pin open test has to be disabled.

<sup>7)</sup> V<sub>EX</sub>=V<sub>EXH</sub>-V<sub>EXLO</sub> and V<sub>IN\_CM</sub> or V<sub>IN\_BR</sub> shall be related here not to VSS, but to V<sub>EXLO</sub>, which can be some 100mV higher then VSS.

<sup>8)</sup> Every bridge sensor output signal (without any load) shall be in this range under consideration of offset and any possible pressure signal. This demand together with bridge impedance range is necessary to avoid diagnostic errors.

(Definition of unit  $V_{EX}$  see footnote above.)

<sup>9)</sup> Resistivity of parallel circuit of both bridges (or one, if single bridge setup used). Each single bridge shall not exceed given resistance **maximum** limit because of noise performance and necessary timing for bridge open diagnostic.

<sup>10)</sup> There are two bridge operating conditions  $R_{BR}$  and  $R_{BR_single}$  because of different demands to the bridges. For both bridges in parallel it is to consider the maximal current capability of EXHI and, if used, the TADC range for bridge current sensing. For each single bridge the resistivity is defined by limits to ensure correct open bridge detection.

**Example**: Two bridges with  $3k\Omega$  and  $11k\Omega$  are possible, but not with  $1.5k\Omega$  together with  $2k\Omega$  or  $3k\Omega$  together with  $15k\Omega$ .

<sup>11)</sup> Nominal the maximum adjustable input range is up to  $112mV_{pp}V$ . But due to discrete offset setting in worst case only up to  $84mV_{pp}V$  sensor signals can be adjusted. Range could be extended by additional resistors in EXHI and EXLO bridge supply lines. See 4.2.2-1 for selection of an appropriate GAIN matching the input range.

PRODUCT PREVIEW - May 18, 2018

# **4 Electrical Characteristics**

$(V_{VS} = V_{VS\_LOW}$  to  $V_{VS\_HIGH}$ ,  $T_A$ =-40°C to + 140°C, unless otherwise noted. Typical values are at  $V_{VS}$ = 5.0V and  $T_A$  = +25°C. Positive currents flow into the device pins.)

## 4.1 SUPPLY - Power Supply and Reverse Polarity Protection

Table 4.1-1: Electrical Parameter Table SUPPLY

| No. | Description                                               | Condition                                                                | Symbol                        | Min | Тур | Мах | Unit |

|-----|-----------------------------------------------------------|--------------------------------------------------------------------------|-------------------------------|-----|-----|-----|------|

| 1   | supply current                                            | V <sub>vs</sub> =5V;                                                     | I <sub>VS</sub>               |     | 3.0 | 5.0 | mA   |

|     |                                                           | I <sub>EXHI</sub> =I <sub>OUT</sub> =0;<br>I <sub>VDDA</sub> =0;         |                               |     |     |     |      |

| 2   | analogue regulator output voltage, normal operation       | I <sub>VDDA</sub> =01mA<br>ext. load;<br>4.75 <v<sub>VS&lt;5.25V</v<sub> | $V_{VDDA}$                    | 3.8 | 4.0 | 4.2 | V    |

| 3   | analogue regulator output voltage in case of over-voltage | 5.25 <v<sub>vs&lt;35V</v<sub>                                            | $V_{\text{VDDA}_{\text{HV}}}$ | 3.8 | 4.0 | 4.2 | V    |

| 4   | current limit at VDDA                                     | V <sub>VDDA</sub> =3V;<br>I <sub>EXHI</sub> =0                           | I <sub>VDDA_LIM</sub>         | -28 | -   | -15 | mA   |

| 5   | threshold for $V_{VS}$ too low                            | $V_{vs}$ falling                                                         | $V_{VS\_LOW}$                 | 4.3 | 4.5 | 4.7 | V    |

| 6   | threshold for $V_{VS}$ too high                           | V <sub>vs</sub> rising                                                   | $V_{VS\_HIGH}$                | 5.4 | 5.7 | 6.0 | V    |

## 4.2 PSEN\_AFE / PADC\_DIG - Sensor Analogue Front-End

#### 4.2.1 Sensor Bridge Excitation and Current Sense

Table 4.2.1-1: Electrical Parameter Table PSEN\_AFE: Sensor Excitation

| No. | Description                                            | Condition                                        | Symbol                | Min  | Тур | Мах  | Unit |

|-----|--------------------------------------------------------|--------------------------------------------------|-----------------------|------|-----|------|------|

| 1   | excitation voltage drop from VDDA pin to EXHI pin      | I <sub>EXHI</sub> = -4mA;<br>V <sub>VS</sub> =5V | $\Delta V_{EXHI}$     | 0.00 | -   | 0.18 | V    |

| 2   | resistance from pin EXLO to VSSA, Mode 1 <sup>1)</sup> | I <sub>EXLO</sub> = +4mA;<br>RSENSE=1            | R <sub>EXLO_1</sub>   | 72   | 87  | 102  | Ω    |

| 3   | resistance from pin EXLO to VSSA, Mode $2^{2^{2}}$     | I <sub>EXLO</sub> = +2mA;<br>RSENSE=2            | R <sub>EXLO_2</sub>   | 144  | 174 | 204  | Ω    |

| 4   | resistance from pin EXLO to VSSA, Mode $3^{3)}$        | I <sub>EXLO</sub> = +1mA;<br>RSENSE=3            | R <sub>EXLO_3</sub>   | 250  | 300 | 350  | Ω    |

| 5   | short circuit current limit at pin EXHI                | V <sub>EXHI</sub> = 3.3V                         | I <sub>EXHI_LIM</sub> | -10  | _   | -5.5 | mA   |

<sup>1)</sup> Setting RSENSE=1 is recommended if bridge current sensing is not used (TCHANx<3), or for bridge resistances in range 0.9..4kΩ (when using bridge current sensing and PHALF1=PHALF2=0).

<sup>2)</sup> Setting RSENSE=2 is recommended if bridge current sensing is used **and** bridge resistances in range 1.9..8kΩ (if PHALF1=PHALF2=0).

<sup>3)</sup> Setting RSENSE=3 is recommended if bridge current sensing is used **and** bridge resistances in range 3.6..12kΩ (if PHALF1=PHALF2=0).

#### 4.2.2 Sensor Signal Acquisition and Pressure ADC

Table 4.2.2-1: Electrical Parameter Table PSEN\_AFE: Sensor Signal Acquisition

| No. | Description                                     | Condition | Symbol             | Min | Тур  | Мах | Unit |

|-----|-------------------------------------------------|-----------|--------------------|-----|------|-----|------|

| 1   | resolution for sensor bridge ADC*)              |           | RESPADC            | -   | 15   | -   | bit  |

| 2   | PADC update rate of 14 bit result <sup>1)</sup> |           | <b>f</b> PADC_UPDT | -   | 3.91 | -   | kHz  |

| 3   | 3dB signal bandwidth of PADC*)                  | LPFC=1    | BWPADC             | -   | 1    | -   | kHz  |

PRODUCT PREVIEW - May 18, 2018

| No. | Description                                                               | Condition                                                | Symbol                    | Min | Тур   | Max | Unit                |

|-----|---------------------------------------------------------------------------|----------------------------------------------------------|---------------------------|-----|-------|-----|---------------------|

| 4   | input range V <sub>INP</sub> -V <sub>INN</sub> for PGAIN=12 <sup>2)</sup> | PGAIN = 0xC                                              | Vs_IN,12                  |     | 7     |     | mV <sub>pp</sub> /V |

| 5   | input range V <sub>INP</sub> -V <sub>INN</sub> for PGAIN=11 <sup>2)</sup> | PGAIN = 0xB                                              | Vs_IN,11                  |     | 10    |     | mV <sub>pp</sub> /V |

| 6   | input range V <sub>INP</sub> -V <sub>INN</sub> for PGAIN=10 <sup>2)</sup> | PGAIN = 0xA                                              | V <sub>S_IN,10</sub>      |     | 14    |     | mV <sub>pp</sub> /V |

| 7   | input range V <sub>INP</sub> -V <sub>INN</sub> for PGAIN=9 <sup>2)</sup>  | PGAIN = 0x9                                              | V <sub>S_IN,9</sub>       |     | 20    |     | mV <sub>pp</sub> /V |

| 8   | input range V <sub>INP</sub> -V <sub>INN</sub> for PGAIN=8 <sup>2)</sup>  | PGAIN = 0x8                                              | V <sub>S_IN,8</sub>       |     | 28    |     | mV <sub>pp</sub> /V |

| 9   | input range V <sub>INP</sub> -V <sub>INN</sub> for PGAIN=4 <sup>2)</sup>  | PGAIN = 0x4                                              | V <sub>S_IN,4</sub>       |     | 28    |     | mV <sub>pp</sub> /V |

| 10  | input range V <sub>INP</sub> -V <sub>INN</sub> for PGAIN=3 <sup>2)</sup>  | PGAIN = 0x3                                              | V <sub>S_IN,3</sub>       |     | 40    |     | mV <sub>pp</sub> /V |

| 11  | input range V <sub>INP</sub> -V <sub>INN</sub> for PGAIN=2 <sup>2)</sup>  | PGAIN = 0x2                                              | V <sub>S_IN,2</sub>       |     | 56    |     | mV <sub>pp</sub> /V |

| 12  | input range V <sub>INP</sub> -V <sub>INN</sub> for PGAIN=1 <sup>2)</sup>  | PGAIN = 0x1                                              | Vs_IN,1                   |     | 80    |     | mV <sub>pp</sub> /V |

| 13  | input range V <sub>INP</sub> -V <sub>INN</sub> for PGAIN=0 <sup>2)</sup>  | PGAIN = 0x0                                              | V <sub>S_IN,0</sub>       |     | 112   |     | mV <sub>pp</sub> /V |

| 14  | minimum offset of PADCx input range <sup>3)</sup>                         | POFFS = 0x10<br>(-16)                                    | $V_{POFFS}$ min           |     | -4.00 |     | V <sub>S_IN,n</sub> |

| 15  | maximum offset of PADCx input range <sup>3)</sup>                         | POFFS = 0x0f<br>(+15)                                    | $V_{POFFS\_max}$          |     | +3.75 |     | V <sub>S_IN,n</sub> |

| 16  | offset adjustment average step size of PADCx input range <sup>4)</sup>    | (V <sub>POFFS_max</sub> -<br>V <sub>POFFS_min</sub> )/31 | $V_{POFFS_{step}}$        |     | 0.25  |     | V <sub>S_IN,n</sub> |

| 17  | ratio of internal half bridge resistor divider <sup>5)</sup>              | PHALFx=1,<br>POLx=0<br>meas. of V <sub>INNx</sub>        | Rat <sub>PHALF</sub>      | 48  | 50    | 52  | %V <sub>EX</sub>    |

| 18  | signal-to-noise ratio for maximum band width (LPFC=1) <sup>*) 6)</sup>    | PGAIN=0xA;<br>40mV span;<br>noise BW=1kHz                | SNR <sub>PADC</sub>       | -   | 65    | -   | dB                  |

| 19  | signal-to-noise ratio with medium band width (LPFC=3) <sup>*) 6)</sup>    | PGAIN=0xA ;<br>40mV span;<br>noise<br>BW=210Hz           | SNR <sub>PADC_250Hz</sub> | -   | 70    | -   | dB                  |

| 20  | input equivalent noise in base band*)                                     | PGAIN=0xA;<br>40mV span;<br>nois. BW=1kHz                | e <sub>iN</sub>           | -   | 7     | -   | μV <sub>rms</sub>   |

\*) Not tested in production

<sup>1)</sup> Derived from system clock oscillator. For timing tolerances see 4.8-1.

<sup>2)</sup> Usable input difference voltage range at pins INP and INN depending on programmed GAIN value in application. This includes voltage range for span and bridge offset combined. Indirect production test by measurement of PADC gain.

<sup>3)</sup> This means shift of center of input range related to this input range V<sub>S\_IN,n</sub> (see 6.3.2-2).

For lower gain settings not all offset settings are possible, see operating condition  $V_{IN\_BR}$ . <sup>4)</sup> This means shift of center of input range related to this input range  $V_{S\_IN,n}$  (see 6.3.2-2).

<sup>5)</sup> Ratio calculated from: (V<sub>INNx</sub>-V<sub>EXLO</sub>)/(V<sub>EXHI</sub>-V<sub>EXLO</sub>)\*100% 6) with:

$$SNR = 20 \cdot \log_{10} \left( \frac{V_{span}}{2 \cdot \sqrt{2} \cdot e_{IN}} \right)$$

# 4.3 TSEN\_AFE / TADC\_DIG - Temperature Sensor Analogue Front-End

Table 4.3-1: Electrical Parameter Table TSEN\_AFE: Temperature Signal ADC

| No. | Description                                                         | Condition | Symbol                 | Min | Тур | Мах | Unit |

|-----|---------------------------------------------------------------------|-----------|------------------------|-----|-----|-----|------|

| 1   | resolution for temperature ADC <sup>*)</sup>                        | TRES_LO=0 | RESTADC                | -   | 14  | -   | bit  |

|     | TADC update rate of 14 bit results for each T1 and T2 <sup>1)</sup> | TRES_LO=0 | f <sub>tadc_updt</sub> | -   | 60  | -   | Hz   |

PRODUCT PREVIEW - May 18, 2018

| No. | Description                                                        | Condition                                                                         | Symbol                 | Min  | Тур  | Max   | Unit                   |

|-----|--------------------------------------------------------------------|-----------------------------------------------------------------------------------|------------------------|------|------|-------|------------------------|

| 3   | TADC input range low limit <sup>2)</sup>                           | TCHAN=2;<br>TGAIN=2;<br>calibrated;                                               | $V_{T\_REFL}$          | -0.2 | -    | +0.2  | %<br>V <sub>vdda</sub> |

| 4   | TADC input range high limit <sup>2)</sup>                          | code=0x0000->0x0001<br>TCHAN=2;<br>TGAIN=2;<br>calibrated;<br>code=0x3FFE->0x3FFF | V <sub>T_REFH</sub>    | 99.8 | -    | 100.2 | %<br>V <sub>VDDA</sub> |

| 5   | pull-down operating current at pin TSEN1                           |                                                                                   | ITSEN1_PD              | 15   | 20   | 25    | μA                     |

| 6   | average input current at pin TSEN2 with TADC running <sup>1)</sup> | T <sub>SENS2</sub> =2V;<br>TCHAN=2;<br>TGAIN=2;<br>average                        | I <sub>TSEN2_IN</sub>  | -2.0 | -1.4 | -0.5  | μA                     |

| 7   | TADC conversion time for 14 bit result <sup>3)</sup>               | TRES_LO=0                                                                         | t <sub>tadc_conv</sub> | -    | 6.55 | -     | ms                     |

\*) Not tested in production

<sup>1)</sup> Derived from system clock oscillator. For timing tolerances see 4.8-1.

Defined by the scheduler cycle rate. In this frequency ADC conversion of 2 channels are possible.

<sup>2)</sup> Indirect measurement. Parameters V<sub>T\_REFL</sub> and V<sub>T\_REFH</sub> define together offset and gain of TADC for the specified channels.

<sup>3)</sup> Derived from system clock oscillator. For timing tolerances see 4.8-1.

## 4.4 CORRECT - Digital Sensor Signal Processing

#### 4.4.1 Pressure Sensor Signal Correction

Table 4.4.1-1: Electrical Parameter Table CORRECT: Bridge Sensor

| No. | Description                                              | Condition | Symbol             | Min | Тур  | Мах | Unit |

|-----|----------------------------------------------------------|-----------|--------------------|-----|------|-----|------|

| 1   | update rate of bridge sensor acquisition <sup>1)</sup>   |           | <b>f</b> psen_updt | -   | 3.91 | -   | kHz  |

|     | d from system clock oscillator. For timing tolerances se | 0/18-1    |                    |     |      |     |      |

<sup>1)</sup> Derived from system clock oscillator. For timing tolerances see 4.8-1.

#### 4.4.2 Sensor Temperature Signal Correction

| Table 4.4.2-1: Electrical Parameter | Table CORRECT: Temperature Sensor |

|-------------------------------------|-----------------------------------|

|-------------------------------------|-----------------------------------|

| No. | Description                                                                              | Condition                                                     | Symbol              | Min | Тур | Мах | Unit |

|-----|------------------------------------------------------------------------------------------|---------------------------------------------------------------|---------------------|-----|-----|-----|------|

| 1   | error of temperature using internal diode <sup>*) 1)</sup>                               | TCHAN=0                                                       | E <sub>T,INT</sub>  | -2  | -   | +2  | K    |

| 2   | error of temperature using external diode <sup>*</sup> )                                 | TCHAN=1                                                       | E <sub>T,EXT</sub>  | -2  | -   | +2  | K    |

|     | error of temperature using bridge resist-<br>ance as temperature sensor <sup>*) 2)</sup> | TCHAN=3<br>TCR <sub>BR_2nd</sub> =<br>TCR <sub>BR</sub> /1000 | E <sub>T,I_EX</sub> |     | 1   |     | К    |

\*) Not tested in production

<sup>1)</sup> Calibration at customer side together and during sensor calibration process.

At delivery not calibrated.

<sup>2)</sup> For temperature sensing using the bridge resistance of the sensor attached, only sensor as specified in the recommended operating (1 + 700) + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 700 + 7

conditions (ch. 3) are suitable. For the given conditions and  $R_{BR}$  behavior according  $R_{BR}(T) = R_{BR}(25^{\circ}C) \cdot (1 + TCR_{BR} \cdot (T-25^{\circ}C) + TCR_{BR_{2nd}} \cdot (T-25^{\circ}C)^{2})$  the given tolerance can be achieved.

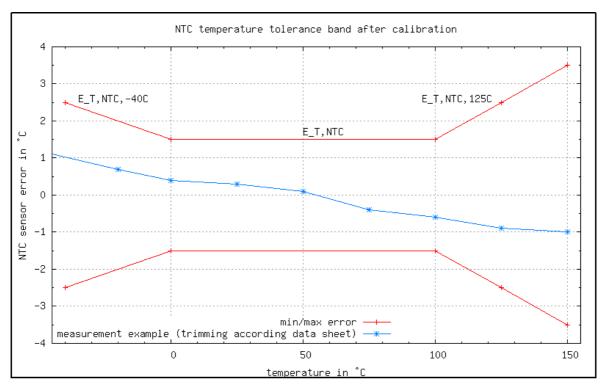

#### 4.4.3 NTC Temperature Processing

Table 4.4.3-1: Electrical Parameter Table CORRECT: NTC Sensor

| No. | Description                                         | Condition | Symbol             | Min  | Тур | Max  | Unit |

|-----|-----------------------------------------------------|-----------|--------------------|------|-----|------|------|

| 1   | error of corrected NTC temperature <sup>*) 1)</sup> | T=0100°C  | E <sub>T,NTC</sub> | -1.5 | -   | +1.5 | K    |

PRODUCT PREVIEW - May 18, 2018

| No. | Description                                                                       | Condition | Symbol                       | Min  | Тур   | Max  | Unit |

|-----|-----------------------------------------------------------------------------------|-----------|------------------------------|------|-------|------|------|

| 2   | error of corrected NTC temperature in extended temperature range <sup>*) 2)</sup> | T=125°C   | E <sub>T,NTC,125C</sub>      | -2.5 | -     | +2.5 | К    |

|     | error of corrected NTC temperature in extended temperature range <sup>*) 2)</sup> | T=-40°C   | E <sub>T,NTC,-40C</sub>      | -2.5 | -     | +2.5 | К    |

| 4   | update rate of NTC sensor evaluation <sup>3)</sup>                                |           | <b>f</b> <sub>NTC_UPDT</sub> | -    | 60    | -    | Hz   |

| 5   | NTC characteristic model parameter A <sup>*) 1)</sup>                             |           | 1/A                          | -    | 300   | -    | K    |

| 6   | NTC characteristic model parameter B <sup>*) 1)</sup>                             |           | 1/B                          | -    | 3400  | -    | К    |

| 7   | NTC characteristic model parameter C <sup>*) 1)</sup>                             |           | 1/C                          | -    | 250e3 | -    | K    |

\*) Not tested in production

<sup>1)</sup> It is assumed, the NTC characteristic fits the following formula:

$T_{NTC}(R) = \frac{1}{A + B \cdot \ln\left(\frac{R}{R_0}\right) + C \cdot \ln^2\left(\frac{R}{R_0}\right) + D \cdot \ln^3\left(\frac{R}{R_0}\right)} \quad \text{with:} \quad R_0 = R(T_0) \quad \text{and} \quad T_0 = \frac{1}{A}$

Operating point resistor set to  $R_{OP} = 0.8 \cdot R_{NTC_{25}}$ . <sup>2)</sup> Error limit line shows a linear behavior between -40°C and 0°C and between 100°C and 150°C (see 6.5.4-3). Assumed: Ideal NTC characteristic.

<sup>3)</sup> Derived from system clock oscillator. For timing tolerances see 4.8-1.

## 4.5 SENT\_DIG / SENT\_IF - SENT and Programming Interface

#### 4.5.1 SENT Mode

Table 4.5.1-1: Electrical Parameter Table SENT\_IF: SENT Mode

| No. | Description                                                                    | Condition                                                     | Symbol                       | Min  | Тур  | Мах  | Unit       |

|-----|--------------------------------------------------------------------------------|---------------------------------------------------------------|------------------------------|------|------|------|------------|

| 1   | low state output voltage                                                       | $I_{OUT} = 0.52 \text{ mA},$<br>measured at<br>SENT-wire      | Vout,ol                      | -    | -    | 0.5  | V          |

| 2   | high state output voltage                                                      | I <sub>ou⊤</sub> = -0.1 mA,<br>measured at<br>SENT-wire       | V <sub>OUT,OH</sub>          | 4.1  | -    | -    | V          |

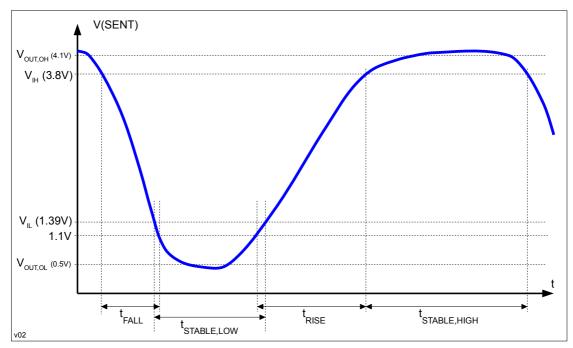

| 3   | signal fall time (see 6.6.1.1-2)                                               | clock tick=3µs;<br>from 3.8V->1.1V                            | t <sub>FALL</sub>            | -    | -    | 6.5  | μs         |

| 4   | signal rise time (see 6.6.1.1-2)                                               | clock tick=3µs;<br>from 1.1V->3.8V                            | t <sub>RISE</sub>            | -    | -    | 18   | μs         |

| 5   | edge to edge jitter with static environment for any pulse period <sup>*)</sup> |                                                               | $\Delta t_{FALL}$            | -    | -    | 0.1  | μs         |

| 6   | low state duration (see 6.6.1.1-2) <sup>*) 1)</sup>                            | clock tick=3µs,<br>pulse low for 5<br>clock ticks             | t <sub>stable,low</sub>      | 6    | -    | -    | μs         |

| 7   | high state duration (see 6.6.1.1-2) <sup>*) 1)</sup>                           | clock tick=3µs,<br>pulse high for 7<br>clock ticks            | t <sub>stable,high</sub>     | 6    | -    | -    | μs         |

| 8   | tick time for SENT per LSB in<br>TICKSEL[4:0] value <sup>2)</sup>              | TICKSEL[4:0]=n<br>t <sub>тіск,LSB</sub> =t <sub>тіск</sub> /n | $t_{\text{TICK},\text{LSB}}$ | 0.94 | 1.00 | 1.06 | μs/<br>LSB |

\*) Not tested in production

<sup>1)</sup> Measured at SENT-wire, receiver connected.

<sup>2)</sup> Derived from and checked with oscillator frequency.

PRODUCT PREVIEW - May 18, 2018

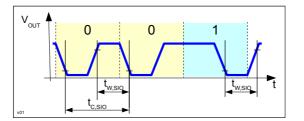

#### 4.5.2 SIO Mode (Serial Input Output)

| Table 4.5.2-1: Electrical Parameter T | Table SENT_ | IF: SIO Mode |

|---------------------------------------|-------------|--------------|

|---------------------------------------|-------------|--------------|

| No. | Description                                                                                   | Condition                           | Symbol                   | Min  | Тур   | Max  | Unit                  |

|-----|-----------------------------------------------------------------------------------------------|-------------------------------------|--------------------------|------|-------|------|-----------------------|

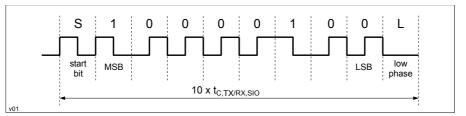

| 1   | data baud rate <sup>1)</sup>                                                                  |                                     | BR <sub>sio</sub>        | -    | 14400 | -    | bit/s                 |

| 2   | SIO bit cycle time, transmitting                                                              |                                     | t <sub>c,tx,sio</sub>    | 61.0 | 68.0  | 76.0 | μs                    |

| 3   | SIO bit low time, transmitting thresholds 40% $V_{\rm VS}$ falling to 60% $V_{\rm VS}$ rising | C <sub>out</sub> =2.2nF             | $t_{\text{W,TX,L,SIO}}$  | 0.45 | 0.50  | 0.55 | t <sub>c,tx.sio</sub> |

| 4   | SIO bit cycle time, receiving                                                                 |                                     | t <sub>C,RX,SIO</sub>    | 58.0 | 69.4  | 79.0 | μs                    |

| 5   | SIO bit low time, receiving                                                                   |                                     | t <sub>w,RX,L,SIO</sub>  | 0.45 | 0.5   | 0.55 | $t_{\text{C,RX,SIO}}$ |

| 6   | SIO input threshold at pin OUT (falling)                                                      | falling edge                        | $V_{\text{THf,SIO}}$     | 0.30 | -     | 0.60 | V <sub>vs</sub>       |

| 7   | SIO input threshold at pin OUT (rising)                                                       | rising edge                         | V <sub>THr,SIO</sub>     | 0.40 | -     | 0.70 | V <sub>vs</sub>       |

| 8   | SIO input hysteresis at pin OUT <sup>*)</sup>                                                 |                                     | V <sub>HYS,SIO</sub>     | 0.05 | 0.20  | 0.35 | V <sub>VS</sub>       |

| 9   | SIO output low level at pin OUT                                                               | $I_{OL,SIO} \le 0.5 \text{ mA}$     | V <sub>OL,SIO</sub>      | 0.10 | -     | 0.65 | V                     |

| 10  | SIO output high level at pin OUT                                                              | I <sub>OL,SIO</sub> ≥ -0.3 mA       | V <sub>OH,SIO</sub>      | 3.9  | -     | 5.5  | V                     |

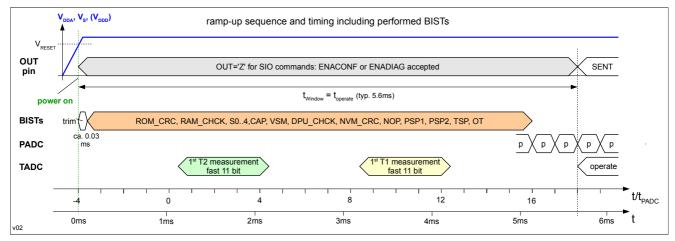

| 11  | Time window to enter configuration or dia-<br>gnostic mode <sup>1)</sup>                      |                                     | $\mathbf{t}_{Window}$    | 5.0  | 5.6   | 6.0  | ms                    |

| 12  | SIO command timeout <sup>1)</sup>                                                             | max. duration of <b>one</b> command | t <sub>timeout,SIO</sub> | 9    | 10    | 11   | ms                    |

\*) Not tested in production

<sup>1)</sup> Derived from and checked with system clock oscillator.

## 4.6 CONTROL - Digital Control, I2C Interface and Test Mode Logic

#### 4.6.1 Inter IC Interface (I2C)

Table 4.6.1-1: I2C Interface: Electrical Parameter Table

| No. | Description                                                           | Condition                                                | Symbol                | Min | Тур | Мах | Unit |

|-----|-----------------------------------------------------------------------|----------------------------------------------------------|-----------------------|-----|-----|-----|------|

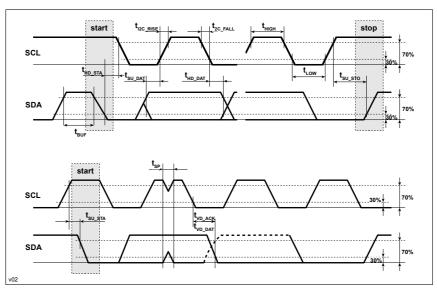

| 1   | SCL clock frequency<br>(Fast mode I <sup>2</sup> C bus) <sup>1)</sup> |                                                          | f <sub>SCL</sub>      | -   | -   | 400 | kHz  |

| 2   | logic input threshold for pins SDA, SCL (rising)                      | rising                                                   | V <sub>I2C_THr</sub>  | 50  | -   | 70  | %VS  |

| 3   | logic input threshold for pins SDA, SCL (falling)                     | falling                                                  | V <sub>I2C_THf</sub>  | 30  | -   | 50  | %VS  |

| 4   | hysteresis at inputs SDA, SCL*)                                       |                                                          | V <sub>I2C_HYS</sub>  | 10  | -   | 30  | %VS  |

| 5   | low level output voltage at SDA, SCL                                  | I <sub>pin</sub> = 3 mA                                  | V <sub>I2C_OL</sub>   | 0   | -   | 0.4 | V    |

| 6   | input leakage current at pins SDA, SCL                                | 0 < V <sub>PIN</sub> < V <sub>VS</sub><br>(SDA tristate) | I <sub>I2C_LK</sub>   | -1  | -   | 1   | μA   |

| 7   | input capacitance for pins SDA, SCL*)                                 |                                                          | C <sub>I2C_IN</sub>   | -   | -   | 10  | pF   |

| 8   | output fall time of SDA signal*)                                      | C <sub>LOAD</sub> < 400pF<br>s. 6.7.1-1                  | t <sub>I2C_FALL</sub> | 20  | -   | 120 | ns   |

\*) Not tested in production

<sup>1)</sup> checked with worst case pattern

PRODUCT PREVIEW - May 18, 2018

### 4.7 NVM - Non-Volatile Memory

#### Table 4.7-1: Electrical Parameter Table Memory

| No.       | Description                            | Condition     | Symbol               | Min  | Тур | Мах | Unit |

|-----------|----------------------------------------|---------------|----------------------|------|-----|-----|------|

| 1         | NVM array size x 16 bit <sup>*)</sup>  | for info only | N <sub>NVM</sub>     | -    | 128 | -   | Word |

| 2         | endurance (write cycles) <sup>*)</sup> |               | N <sub>PROG</sub>    | 1000 | -   | -   | 1    |

| 3         | data retention time <sup>*) 1)</sup>   |               | t <sub>NVM_ret</sub> | 15   |     | -   | year |

| *) Not te | sted in production                     |               | -                    |      |     | •   |      |

<sup>1)</sup> Permissible temperature profile as follows, e.g. Operating (12000h total), with:  $T_{j,op} = -40^{\circ}C$ , t < 720h -40 °C <  $T_{j,op} \le 25^{\circ}C$ , t < 2400h 25 °C <  $T_{j,op} \le 100^{\circ}C$ , t < 7800h 100 °C <  $T_{j,op} \le 150^{\circ}C$ , t < 1080h add 13.6 years non-operating within -40 < Tj  $\le 85^{\circ}C$

#### 4.8 OSC - Oscillator

Table 4.8-1: Electrical Parameter Table OSC

| No. | Description                           | Condition | Symbol           | Min | Тур  | Max  | Unit |

|-----|---------------------------------------|-----------|------------------|-----|------|------|------|

| 1   | core frequency of internal oscillator |           | f <sub>CLK</sub> | 9.5 | 10.0 | 10.5 | MHz  |

## 4.9 Functional Safety

#### 4.9.1 Safety Measures and Diagnosis

Table 4.9.1-1: Electrical Parameter Table: Safety Measures and Diagnosis

| No. | Description                                                                                   | Condition | Symbol                | Min | Тур | Мах | Unit |

|-----|-----------------------------------------------------------------------------------------------|-----------|-----------------------|-----|-----|-----|------|

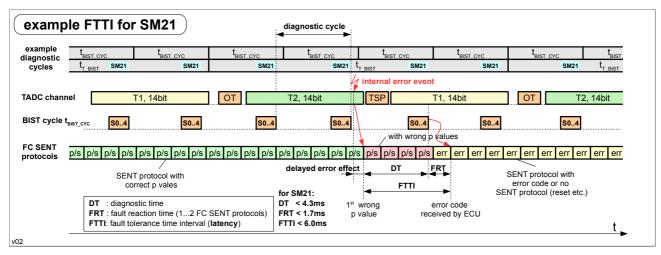

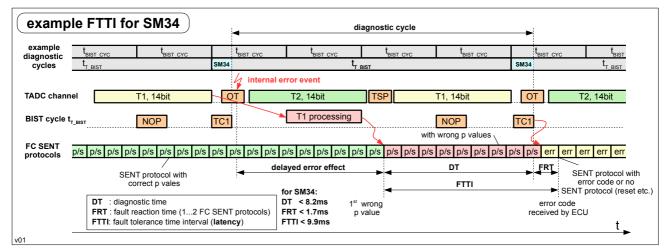

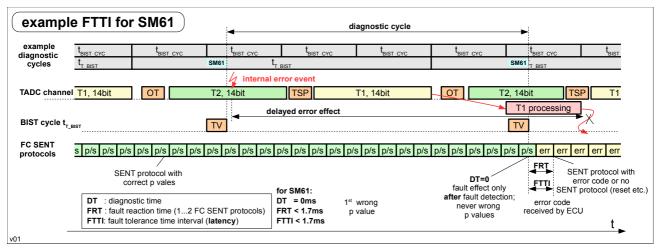

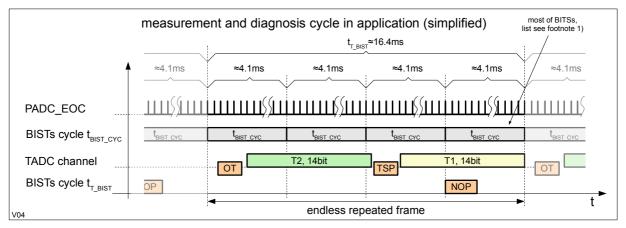

| 1   | period of BIST and diagnosis cycle includ-<br>ing BISTs according 6.10.1.2-1 <sup>°) 1)</sup> |           | t <sub>BIST_CYC</sub> | -   | 4.2 | -   | ms   |

|     | period of temperature related BISTs, see 6.10.1.2-1 (all BISTs enabled) <sup>*) 2)</sup>      |           | $t_{T\_BIST}$         | -   | 17  | -   | ms   |

|     | period of ROM (OTP) BIST <sup>*) 2)</sup>                                                     |           | t <sub>ROM_BIST</sub> | -   | 4.5 | -   | ms   |

\*) Not tested in production

<sup>1)</sup> Cycle time of most diagnostic and cyclical BIST checks. Details see in chapter 6.10. Derived from system clock oscillator. For timing tolerances see 4.8-1.

<sup>2)</sup> Derived from system clock oscillator. For timing tolerances see 4.8-1.

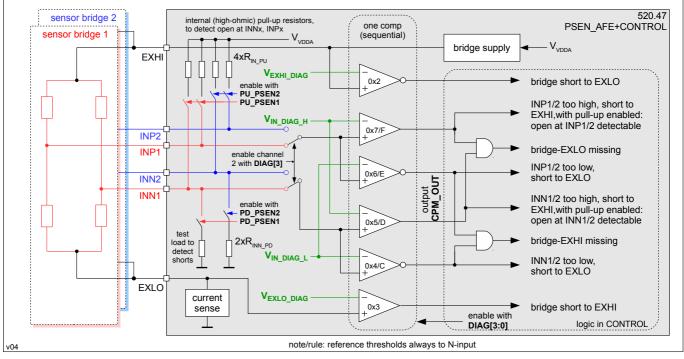

#### 4.9.2 Bridge Sensor Diagnosis - SM21

Table 4.9.2-1: Electrical Parameter Table: Bridge Diagnostics

| No. | Description                                                     | Condition      | Symbol                                 | Min  | Тур  | Мах  | Unit              |

|-----|-----------------------------------------------------------------|----------------|----------------------------------------|------|------|------|-------------------|

| 1   | diagnostic threshold "too low" at INP1/2, INN1/2 <sup>1)</sup>  | DIAG=0x4/6/C/E | $V_{\text{IN\_DIAG\_L}}$               | 0.17 | 0.20 | 0.23 | $V_{\text{EX}}$   |

| 2   | diagnostic threshold "too high" at INP1/2, INN1/2 <sup>1)</sup> | DIAG=0x5/7/D/F | $V_{\text{IN}\_\text{DIAG}\_\text{H}}$ | 0.77 | 0.80 | 0.83 | V <sub>EX</sub>   |

| 3   | threshold "short to higher voltage" at EXLO                     | DIAG=0x3/B     | V <sub>EXLO_DIAG</sub>                 | 0.17 | 0.20 | 0.23 | V <sub>VDDA</sub> |

| 4   | threshold "short to lower voltage" at EXHI                      | DIAG=0x2/A     | $V_{\text{EXHI}_{\text{DIAG}}}$        | 0.77 | 0.80 | 0.83 | $V_{\text{VDDA}}$ |

| 5   | switchable pull-up resistor at pins INN1/2, INP1/2 to VDDA      | PU_PSEN1/2=1   | $R_{IN_{PU}}$                          | 20   | 25   | 30   | kΩ                |

PRODUCT PREVIEW - May 18, 2018

| No. | Description                                          | Condition    | Symbol              | Min | Тур | Max | Unit |

|-----|------------------------------------------------------|--------------|---------------------|-----|-----|-----|------|

|     | switchable pull-down resistor at pins INN1/2 to VSSA | PD_PSEN1/2=1 | R <sub>INN_PD</sub> | 30  | 60  | 100 | Ω    |

<sup>1)</sup> V<sub>EX</sub> = V<sub>EXH</sub>-V<sub>EXLO</sub> are related to V<sub>EXLO</sub> (not VSSA). V<sub>EXLO</sub> can be several 100mV above VSSA.

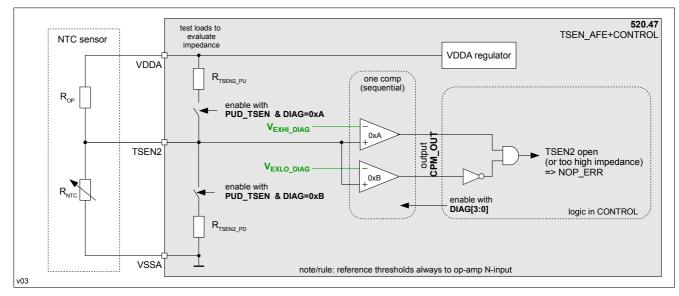

#### 4.9.3 NTC Sensor Diagnosis - SM22, SM23

Table 4.9.3-1: Electrical Parameter Table: NTC Sensor Diagnosis

| No. | Description                                                                    | Condition                 | Symbol                | Min | Тур  | Мах | Unit        |

|-----|--------------------------------------------------------------------------------|---------------------------|-----------------------|-----|------|-----|-------------|

| 1   | switchable pull-up resistor at pin TSEN2 to VDDA                               | PUD_TSEN=1;<br>DIAG[0]=0  | R <sub>TSEN2_PU</sub> | 15  | 20   | 25  | kΩ          |

|     | switchable pull-down resistor at pin TSEN2 to VSSA                             | PUD_TSEN=1;<br>DIAG[0]=1; | $R_{TSEN2_PD}$        | 15  | 20   | 25  | kΩ          |

| 3   | out-of-range indication of NTC input, recommended lower limit <sup>*) 1)</sup> | RTx_LIM[7:0]=<br>0x06     | V <sub>NTC_MIN</sub>  | -   | 2.3  | -   | %FS<br>TADC |

| 4   | out-of-range indication of NTC input, recommended upper limit <sup>*)</sup>    | RTx_LIM[15:8]=<br>0xFA    | V <sub>NTC_MAX</sub>  | -   | 97.7 | -   | %FS<br>TADC |

\*) Not tested in production

<sup>1)</sup> For NTC sensors a divider of R<sub>NTC</sub> and R<sub>OP</sub> between VSSA and VDDA is connected to TSEN2 (Parameter TGAIN2 = 2).

Example: If VDDA=4V and NTC-voltage out of range enabled (RT2\_ERR=1), input voltages below about 2.3% \* 4V = 92mV at TSEN2 are detected as range error (for instance due to short TSEN2 to VSS or divider open at VDDA).

#### 4.9.4 Diode Sensor Diagnosis - SM24

Table 4.9.4-1: Electrical Parameter Table: Diode Sensor Diagnosis

| No. | Description                                                                                                     | Condition                               | Symbol                 | Min | Тур | Max | Unit |

|-----|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------|------------------------|-----|-----|-----|------|

| 1   | threshold for temperature diode forward voltage for "diode shorted"; recommended limit <sup>*) 1)</sup>         | RTx_LIM[7:0]=<br>0x13<br>TGAINx=0 or 1  | V <sub>DIO_SHORT</sub> | -   | 0.1 | -   | V    |

|     | threshold for temperature diode forward voltage for "diode open" indication; recommended limit <sup>*) 1)</sup> | RTx_LIM[15:8]=<br>0xE6<br>TGAINx=0 or 1 | V <sub>DIO_OPEN</sub>  | -   | 1.2 | -   | V    |

| 3   | threshold for overtemperature error <sup>*) 2)</sup>                                                            |                                         | T <sub>OT_ERR</sub>    | 150 | 158 | 166 | °C   |

\*) Not tested in production

<sup>1)</sup> Applied TADC limits depending on NVM setting of RT1\_LIM or RT2\_LIM and selected TGAIN range. Only for information: Checked indirectly by TADC measurement.

<sup>2)</sup> Indirect measurement at lower temperature.

PRODUCT PREVIEW – May 18, 2018

# **5** Register Overview Table

| Addr | Name                  | Val  | Bit 7    | Bit 6      | Bit 5   | Bit 4                     | Bit 3       | Bit 2       | Bit 1    | Bit 0    |

|------|-----------------------|------|----------|------------|---------|---------------------------|-------------|-------------|----------|----------|

| 0x70 | DIAG_RES1             | 0x00 | OPINP1   | OPINN1     | SHBRL   | SHBRH                     | INP1EXHI    | INP1EXLO    | INN1EXHI | INN1EXLO |

| 0x71 | DIAG_RES2             | 0x00 | OPINP2   | OPINN2     | -       | -                         | INP2EXHI    | INP2EXLO    | INN2EXHI | INN2EXLO |

| 0x72 | ERRC1                 | 0x00 | PV_ERR   | TV_ERR     | V5H_ERR | V5L_ERR                   | -           | TSP_ERR     | PSP2_ERR | PSP1_ERR |

| 0x73 | ERRC2                 | 0x00 | S42_ERR  | S32_ERR    | S22_ERR | S02_ERR                   | S41_ERR     | S31_ERR     | S21_ERR  | S01_ERR  |

| 0x74 | ERRC3                 | 0x00 | -        | NOP_ERR    | RT2_ERR | RT1_ERR                   | T2_SAT      | T1_SAT      | P2_SAT   | P1_SAT   |

| 0x75 | ERRC4                 | 0x00 | OT_ERR   | VSM_ERR    | -       | -                         | S1_ERR      | TC1_ERR     | PC2_ERR  | PC1_ERR  |

| 0x76 | ERRC5                 | 0x00 | -        | NV3_ERR    | NV2_ERR | NV1_ERR                   | -           | -           | -        | -        |

| 0x77 | I2C_CTRL SFR and NVM  | 0x60 | -        | SCL_OUT    | SDA_OUT | CCP_LCK                   | I2C_AI      | DR[1:0]     | I2C_ENA  | I2C_MODE |

| 0x78 | PGAIN1 SFR and NVM    | 0x00 | POL1     | PHALF1     | RSEN    | SE[1:0]                   |             | PGAI        | V1[3:0]  |          |

| 0x79 | POFFS1 SFR and NVM    | 0x20 |          | LPFC[2:0]  |         |                           | POFFS1[4:0] |             |          |          |

| 0x7A | PGAIN2 SFR and NVM    | 0x00 | POL2     | PHALF2     | -       | P2OFF                     | PGAIN2[3:0] |             |          |          |

| 0x7B | POFFS2 SFR and NVM    | 0x00 | -        | -          | -       |                           | POFFS2[4:0] |             |          |          |

| 0x7C | SENTCONF1 SFR and     | 0x00 | F        | C_MODE[2:0 | )]      |                           | •           | TICKSEL[4:0 | ]        |          |

| 0x7D | SENTCONF2 SFR and     | 0x00 | SC_MODE  | SC_CONF    | NPP     | -                         | -           | -           | -        | -        |

| 0x7E | SENTCONF3 SFR and     | 0x00 |          |            |         | PP_LE                     | EN[7:0]     |             |          |          |

| -    | T1_MODE NVM           | 0x00 | IDIO_OFF | -          | -       | -                         | TCHA        | N1[1:0]     | TGAIN    | N1[1:0]  |

| -    | T2_MODE NVM           | 0x00 | -        | -          | -       | CORR2                     | TCHAI       | N2[1:0]     | TGAIN    | V2[1:0]  |

| -    | SENTCONF4 NVM         | 0x00 | -        | -          | F       | FC2_SRC[2:0] FC1_SRC[2:0] |             |             |          |          |

| -    | ERR_EN1 <sup>№™</sup> | 0x00 | PV_EN    | TV_EN      | V5H_EN  | V5L_EN                    | CAP_EN      | TSP_EN      | PSP2_EN  | PSP1_EN  |

| -    | ERR_EN2 <sup>№M</sup> | 0x00 | S42_EN   | S32_EN     | S22_EN  | S02_EN                    | S41_EN      | S31_EN      | S21_EN   | S01_EN   |

| -    | ERR_EN3 NVM           | 0x00 | -        | NOP_EN     | RT2_EN  | RT1_EN                    | T2SAT_EN    | T1SAT_EN    | P2SAT_EN | P1SAT_EN |

| -    | ERR_EN4 NVM           | 0x00 | OT_EN    | VSM_EN     | -       | -                         | S1_EN       | TC1_EN      | PC2_EN   | PC1_EN   |

PRODUCT PREVIEW - May 18, 2018

# **6** Functional Description

## 6.1 Overview

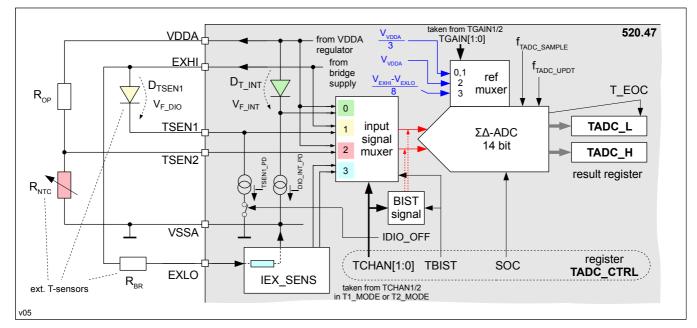

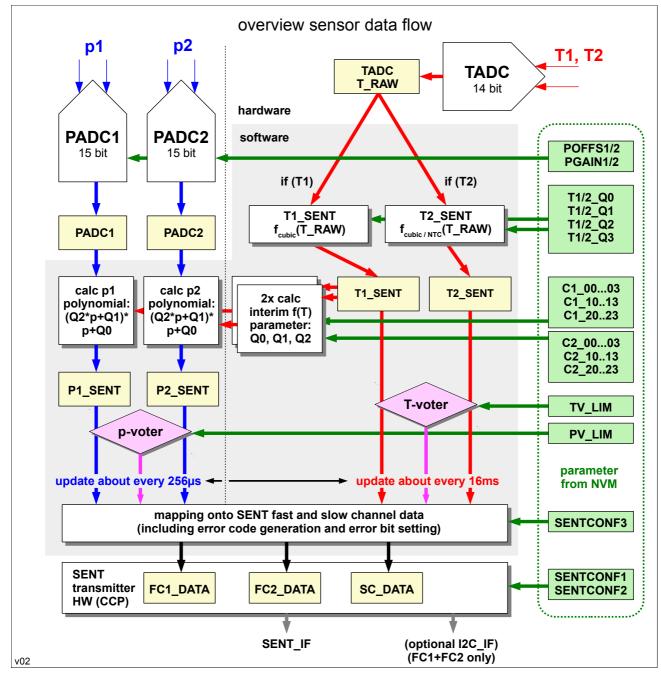

The sensor signal processor (SSP) 520.47 as shown in 6.1-1 contains an analogue front-end for the inputs of two differential resistive bridges and one or two out of 4 different temperature sensors, a digital compensation unit and a SENT data interface block. Supporting circuits are voltage regulators, overvoltage and reverse voltage protection and monitor hardware units and a non-volatile memory block (NVM) for storage of individual device settings (configuration and sensor calibration data, ID-code).

Primary inputs are the differential signals from two resistive pressure sensor bridges which are fed to two parallel high resolution AD-converter, called PADC1 and PADC2 (pressure ADC). These PADC input ranges are separately programmable in offset and gain (or input span). The excitation of the resistive sensor bridge is provided by a stabilized voltage output.

Temperature signals from an internal T-sensor, external diode, external NTC resistor divider or bridge current are fed via a multiplexer to a further AD-channel TADC (temperature ADC), which can convert one or two of these 4 temperature input sources to allow thermal calibration of the bridge sensor including optional 2nd redundant temperature value (for later comparison with the first one).

The one or two selected temperature sensors are processed by the same TADC in time multiplex.

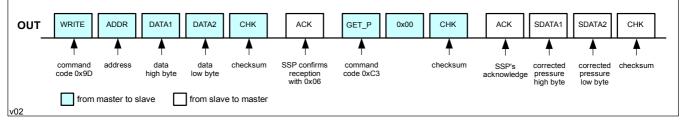

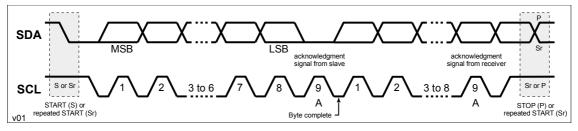

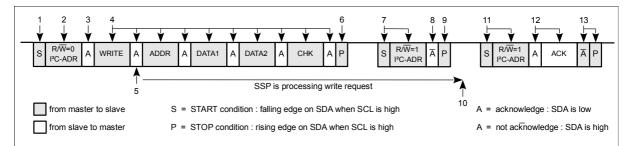

The subsequent compensation calculator engine applies a thermal correction and linearization algorithm to the acquired both bridge signals providing two temperature independent, highly linear outputs  $p_1$  and  $p_2$ . Sensor specific parameters of the correction algorithm from device or batch specific measurements are transferred to the embedded NVM of the IC via a serial data-I/O (SIO) sharing its pin with the SENT data output at pin OUT. Access to internal data registers and programming of configuration or calibration data is also possible through an I2C compatible interface at pins SDA and SCL.

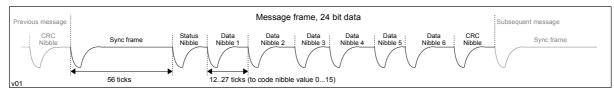

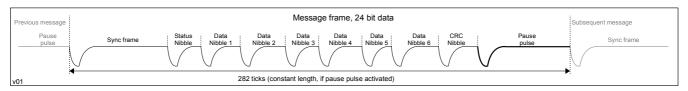

Output of the SSP is provided via SENT data interface according to the **standard SAE J2716**, APR2016. Here, different SENT sensor classes can be configured to provide output of pressure and temperature data in the fast message channel and supplementary data in the enhanced serial message channel.

Figure 6.1-1: SSP Simplified Block Schematic

PRODUCT PREVIEW - May 18, 2018

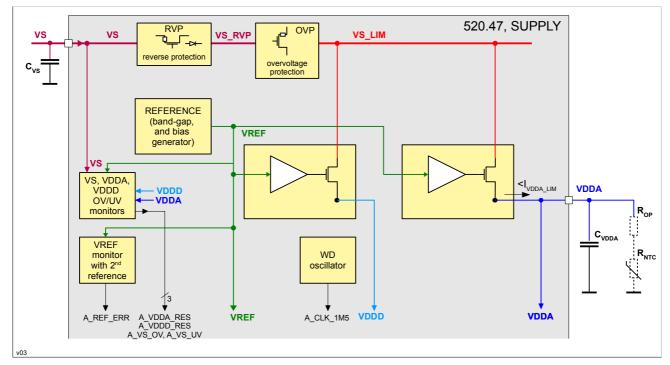

## 6.2 SUPPLY - Power Supply and Reverse Polarity Protection

The IC operates from a 5V-supply with internal over voltage protection (OVP) and reverse voltage protection (RVP). The protection circuitry prevents damage to the device in case of overvoltage at the supply input VS. Also a lowdrop reverse protection circuit is integrated which blocks negative voltages from the internal circuitry.

An integrated linear voltage regulator with output at pin VDDA generates a 4V stabilized voltage to supply the analogue precision circuitry including the sensor excitation unit. A current limitation with threshold  $I_{VDDA\_LIM}$  at the regulator output pin prevents destruction in case of short circuit to ground. This regulator requires an external bypass capacitor to ground for HF-rejection. The pin VDDA is intended to connect this capacitor  $C_{VDDA}$  and optionally a resistor divider with NTC temperature sensor. In sum maximal load current  $I_{VDDA\_EXT\_LD}$  can be drawn from VDDA pin.

An additional on-chip regulator for the digital circuit blocks is integrated (VDDD) but with internal connections only.

The external capacitor  $C_{VS}$  at the main supply input VS is recommended to block fast transients from the IC and for EMC requirements.

Figure 6.2-1: Simplified Schematic of SUPPLY Block

The SUPPLY block provides beside overvoltage (OVP) and reverse polarity protection (RVP):

- an internal reference and bias generation

- a 4.0V regulators for analogue VDD

- a 1.8V regulator for digital VDD

- overvoltage and undervoltage monitor circuits for V<sub>DDA</sub> and V<sub>DDD</sub> regulator outputs

- supply monitor for VS over- and undervoltage

- a monitor for the primary reference VREF against another 2nd reference regarding overvoltage and undervoltage

- an additional oscillator working as clock for watchdog for control logic

PRODUCT PREVIEW - May 18, 2018

#### **Supply Monitors**

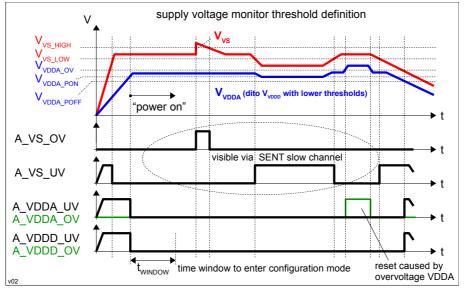

Next figure shows, how reset thresholds for rising and falling  $V_{VDDA}$  resp.  $V_{VDDD}$  and monitor thresholds for  $V_{VS}$  are defined.

Figure 6.2-2: Supply Monitor Threshold Definitions

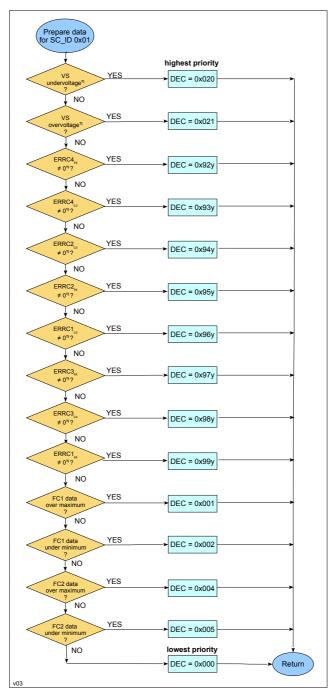

The overvoltage or undervoltage case at the supply VS is copied to the bits **V5H\_ERR** and **V5L\_ERR** of register ERRC1, if the corresponding enable bits **V5H\_EN** and **V5L\_EN** are set in NVM register ERR\_EN1. In the slow channel SENT message this information will be sent as diagnostic error code (VS overvoltage or undervoltage), see 6.6.1.4-1.

Undervoltage or overvoltage at the 4V-regulated V<sub>VDDA</sub> or internal 1.8V-regulated V<sub>VDDD</sub> will trigger a reset of the IC.

Beside the asynchronous monitor signals above there are further synchronous generated reset pulses caused by safety measures. For details see chapter 6.10.1.2.

#### **Reset State:**

The reset state is considered as safe state. The SENT output at pin OUT is tri-state (high-ohmic) during reset state.

PRODUCT PREVIEW - May 18, 2018

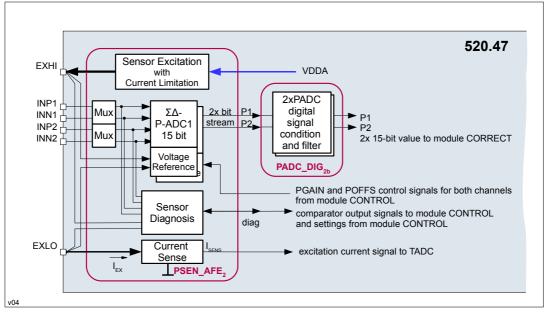

## 6.3 PSEN\_AFE / PADC\_DIG - Sensor Analogue Front-End

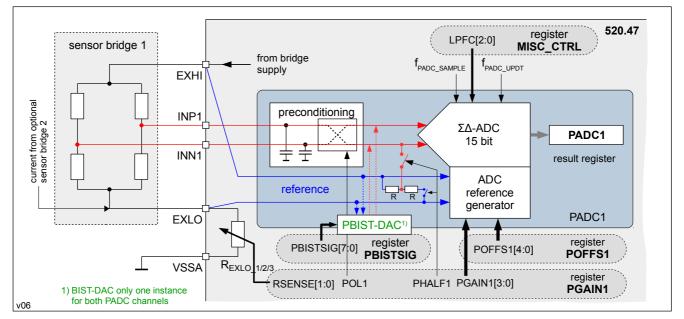

This chapter describes the pressure sensor analogue front-end named PSEN\_AFE. The main structure of the block is shown in following figure:

Figure 6.3-1: Overview Block PSEN\_AFE

The functions of the blocks are:

- supply of sensor bridge with current limitation

- 2x bridge differential signal pre-conditioning for ADC

- 2x 15-bit pressure signal ADC with adjustable input range and offset (PADC1 and PADC2)

- bridge and block function diagnostics

Details are described in following sub-chapters.

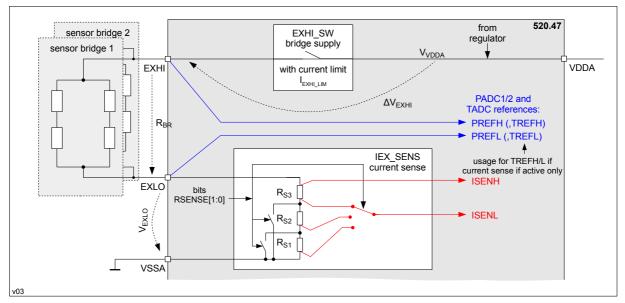

#### 6.3.1 Sensor Bridge Excitation and Current Sense

The sensor bridge is supplied with constant voltage between positive excitation EXHI and ground pin EXLO.

The voltage source at pin EXHI is derived from internal analogue regulator output voltage V<sub>VDDA</sub>. The bridge supply block EXHI\_SW basically forms a switch to VDDA with a low voltage drop  $\Delta V_{EXHI}$  and a current limitation at I<sub>EXHI\_LIM</sub>.

Voltage difference between pins EXHI and EXLO is used by both subsequent pressure signal ADCs (PADC1 and PADC2) as reference potentials as shown in 6.3.1-1. In case of temperature measurement selected by measuring the excitation current  $I_{EX}$  the same potentials are used as reference by the temperature signal ADC (TADC).

PRODUCT PREVIEW - May 18, 2018

Figure 6.3.1-1: Overview Sensor Bridge Excitation

On the lower side of the bridge low ohmic shunt resistors  $R_{S1}$ ,  $R_{S2}$  and  $R_{S3}$  to ground pin VSSA are placed. These are used to sense the excitation current, if used for TADC. To cover the wide range of possible effective bridge resistances (both bridges in parallel), there are two control bits **RSENSE[1:0**] to switch between three different shunt resistances  $R_{EXLO_1}$ ,  $R_{EXLO_2}$  and  $R_{EXLO_3}$ .

The bits **RSENSE[1:0**] has to be set to 0b01 (in NVM memory) at these conditions:

- for low bridge resistances

- if excitation current I<sub>EX</sub> is NOT used for temperature sensing (to minimize the drop at pin EXLO).

The voltage drop at the shunt is fed to the temperature converter TADC, if excitation current sensing is selected as temperature measurement channel.

If temperature measurement via sensing of bridge current at EXLO shall be used, the setting of suited sense resistance depends on minimum reached bridge resistance over temperature range and if optional internal half bridges are used, which would create additional EXLO current.

A recommendation for the proper setting of one out of three different sense resistors by RSENSE[1:0] is shown in the table below.

|             |         | •                                               |                                                       |                                                 |

|-------------|---------|-------------------------------------------------|-------------------------------------------------------|-------------------------------------------------|

| RSENSE[1:0] | typ. Rs | R <sub>BR,min</sub> for<br>PHALF1=0<br>PHALF2=0 | R <sub>BR,min</sub> for<br>PHALF1=0(1)<br>PHALF2=1(0) | R <sub>BR,min</sub> for<br>PHALF1=1<br>PHALF2=1 |

| 0,1         | 87 Ω    | > 0.9 kΩ                                        | > 0.95 kΩ                                             | > 1.0 kΩ                                        |

| 2           | 174 Ω   | > 1.9 kΩ                                        | > 2.2 kΩ                                              | > 2.5 kΩ                                        |

| 3           | 300 Ω   | > 3.6 kΩ                                        | > 4.6 kΩ                                              | > 6.3 kΩ                                        |

Table 6.3.1-1: Detailed Recommendations for RSENSE Setting

For the case PHALF1=PHALF2=0 (internal half bridges are not activated) see also recommendations in 4.2.1-1. There are recommended maximum bridge resistances too for the different ranges. This is because the largest sense resistor should be used to optimize the temperature measurement resolution.

PRODUCT PREVIEW - May 18, 2018

#### 6.3.2 Sensor Signal Acquisition and Pressure ADC

The data acquisition for pressure sensor bridge and signal flow for both PADCs is shown below.

Figure 6.3.2-1: Overview Pressure Sensor Signal Acquisition and PADC

PADC2 has the same structure as PADC1. Elements drawn with suffix "1" in name, identically exist with suffix "2".

The voltages at pins EXHI and EXLO are used to derive proportional references for Sigma-Delta ADC full scale. For flexibility the polarity of INN1/P1 and INN2/P2 inputs can be inverted by setting bit **POL1/2** in registers PGAIN1 or PGAIN2.

As depicted in the figure above, with the control bit **PHALF1/2** for each channel a "half bridge" operation mode can be selected. If enabled the single input INP1 and/or INP2 will be evaluated against internal provided 50% resistive divider between EXHI and EXLO. The corresponding negative input INN1 and/or INN2 shows the internal generated half bridge reference voltage and has to stay high ohmic in that mode.

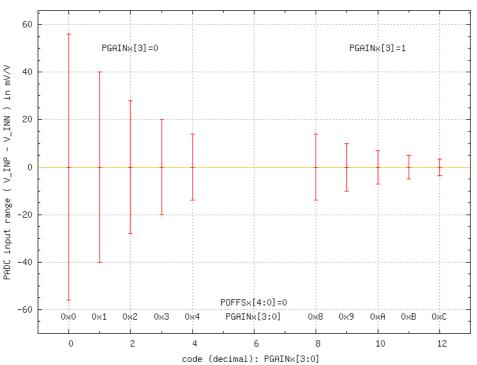

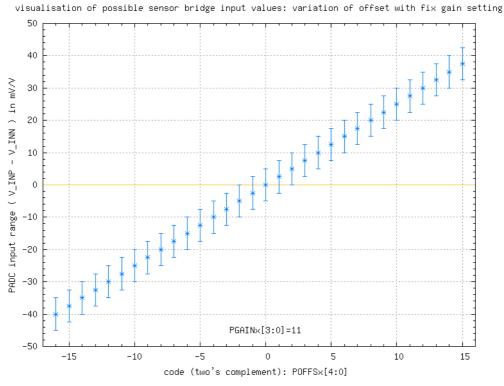

The input range regarding span and offset can be adjusted by setting bits **PGAIN1/2[3:0**] and **POFFS1/2[4:0**] from registers **PGAINx** and **POFFSx** defined in subsequent tables:

| Table 6.3.2-1: Gain and offset setup registers SFR | R and NVM |

|----------------------------------------------------|-----------|

|----------------------------------------------------|-----------|

| Register Name      | Address | Description                                                             |

|--------------------|---------|-------------------------------------------------------------------------|

| PGAIN1 SFR and NVM | 0x78    | gain control register for P1 sensor front-end (copied from <b>NVM</b> ) |

| POFFS1 SFR and NVM | 0x79    | offset control register for P1 sensor front-end (copied from NVM)       |

| PGAIN2 SFR and NVM | 0x7A    | gain control register for P2 sensor front-end (copied from <b>NVM</b> ) |

| POFFS2 SFR and NVM | 0x7B    | offset control register for P2 sensor front-end (copied from NVM)       |

PRODUCT PREVIEW - May 18, 2018

|                 | MSB                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                             |                                                                                                                                       |                                                                                       |                                                                                    |                                                                   | LSB                            |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------|--------------------------------|

| Content         | POL1                                                                                                                                                                                                                                                                                                                       | PHALF1                                                                                                                                                                                                                                                                                                                 | RSENSE[1:0]                                                                                                                                                 |                                                                                                                                       | PGAIN1[3:0                                                                            | )]                                                                                 |                                                                   |                                |