## Am53C94/Am53C96

### **High Performance SCSI Controller**

# Advanced Micro Devices

### DISTINCTIVE CHARACTERISTICS

- Pin/function compatible with NCR53C94/53C96

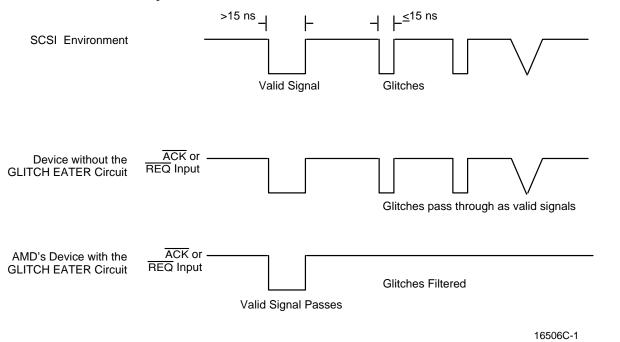

- AMD's Patented GLITCH EATER™ Circuitry on REQ and ACK inputs

- 5 Mbytes per second synchronous SCSI transfer rate

- 20 Mbytes per second DMA transfer rate

- 16-bit DMA Interface plus 2 bits of parity

- **■** Flexible three bus architecture

- Single ended SCSI bus supported by Am53C94

- Single ended and differential SCSI bus supported by Am53C96

- Selection of multiplexed or non-multiplexed address and data bus

- High current drivers (48 mA) for direct connection to the single ended SCSI bus

- Supports Disconnect and Reselect commands

- Supports burst mode DMA operation with a threshold of 8

- Supports 3-byte-tagged queuing as per the SCSI-2 specification

- Supports group 2 and 5 command recognition as per the SCSI-2 specification

- Advanced CMOS process for low power consumption

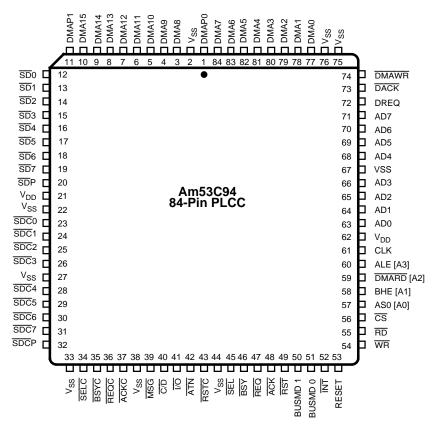

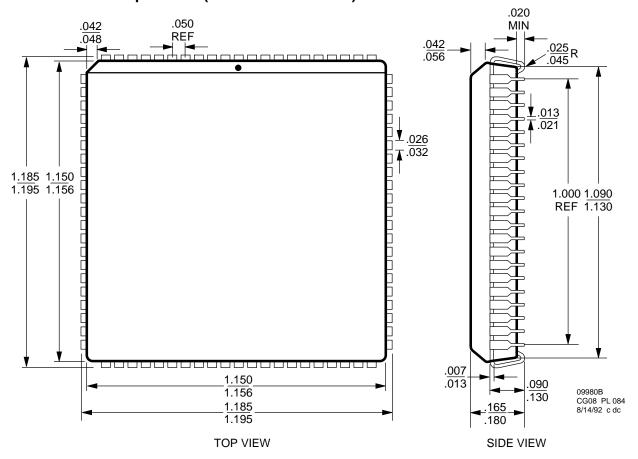

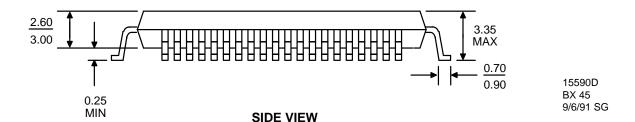

- Am53C94 available in 84-pin PLCC package

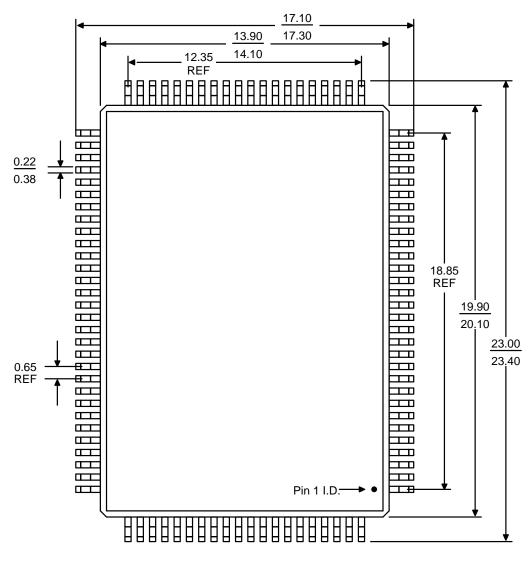

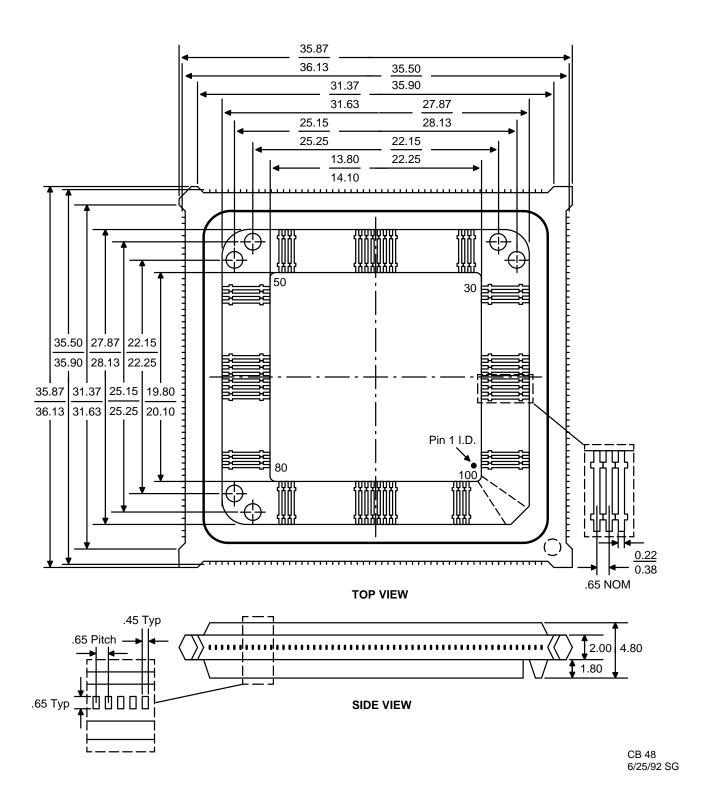

- Am53C96 available in 100-pin PQFP package

### **GENERAL DESCRIPTION**

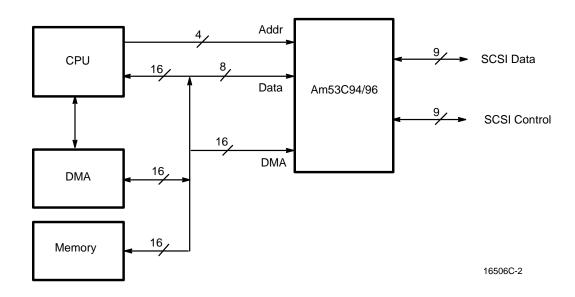

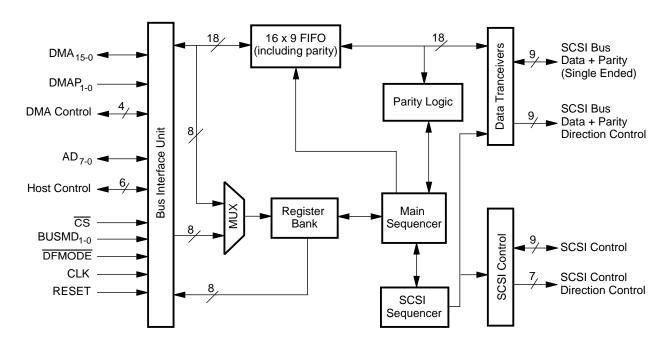

The High Performance SCSI Controller (HPSC) has a flexible three bus architecture. The HPSC has a 16-bit DMA interface, an 8 bit host data interface and an 8-bit SCSI data interface. The HPSC is designed to minimize host intervention by implementing common SCSI sequences in hardware. An on-chip state machine reduces protocol overheads by performing the required sequences in response to a single command from the host. Selection, reselection, information transfer and disconnection commands are directly supported.

The 16-byte-internal FIFO further assists in minimizing host involvement. The FIFO provides a temporary storage for all command, data, status and message bytes as they are transferred between the 16 bit host data bus and the 8 bit SCSI data bus. During DMA operations the FIFO acts as a buffer to allow greater latency in the DMA channel. This permits the DMA channel to be suspended for higher priority operations such as DRAM refresh or reception of an ISDN packet.

Parity on the DMA bus is optional. Parity can either be generated and checked or it can be simply passed through.

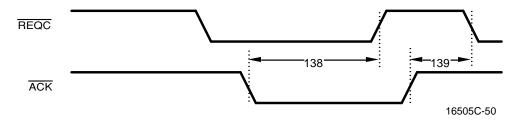

The patented GLITCH EATER Circuitry in the High Performance SCSI Controller detects signal changes that are less than or equal to 15 ns and filters them out. It is designed to dramatically increase system performance and reliability by detecting and filtering glitches that can cause system failure.

The GLITCH EATER Circuitry is implemented on the ACK and REQ lines only. These lines often encounter many electrical anomalies which degrade system performance and reliability. The two most common are Reflections and Voltage Spikes. Reflections are a result of high current SCSI signals that are mismatched by stubs, cables and terminators. These reflections vary from application to application and can trigger false handshake signals on the ACK and REQ lines if the voltage amplitude is at the TTL threshold levels. Spikes are generated by high current SCSI signals switching concurrently. On the control signals (ACK and REQ) they can trigger false data transfers which result in loss of data, addition of random data, double clocking and reduced system reliability. AMD's GLITCH EATER Circuitry helps maintain excellent system performance by treating the glitches. Refer to the diagram on the next page.

### **GLITCH EATER Circuitry in SCSI Environment**

### SYSTEM BLOCK DIAGRAM

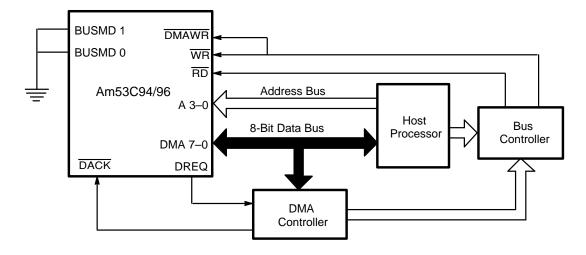

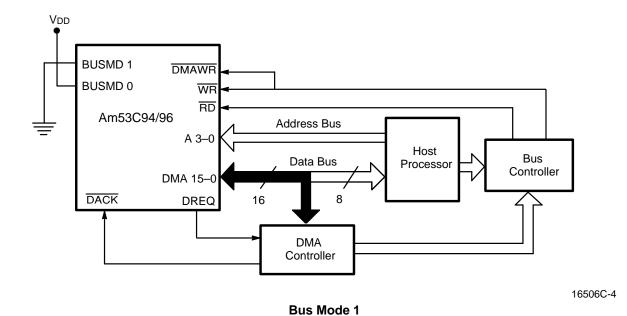

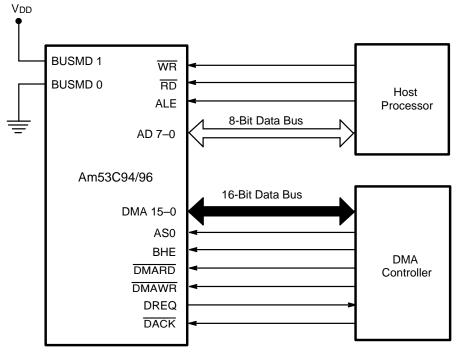

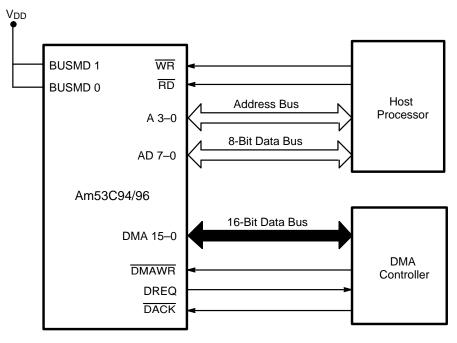

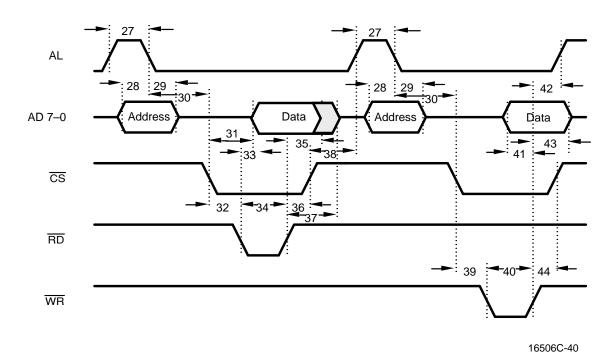

### SYSTEM BUS MODE DIAGRAMS

Bus Mode 0 16506C-3

### **SYSTEM BUS MODE DIAGRAMS**

16506C-5

**Bus Mode 2**

**Bus Mode 3**

### **BLOCK DIAGRAM**

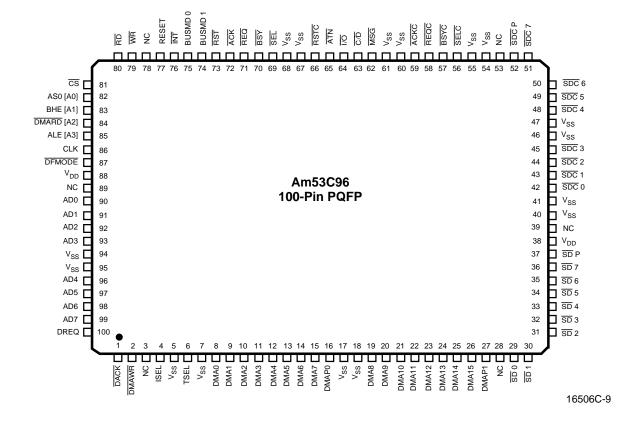

### CONNECTION DIAGRAMS

**Top View**

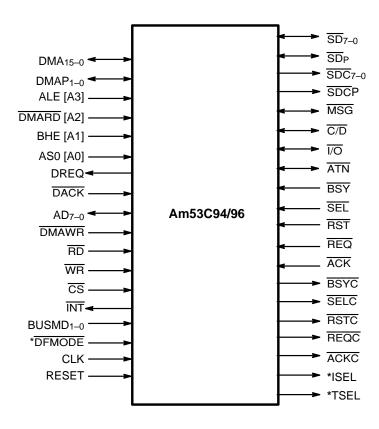

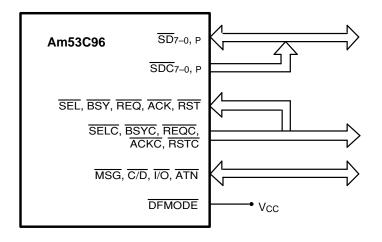

### **LOGIC SYMBOL**

Note:

\*Pins available on the Am53C96 only.

16506C-10

### **RELATED AMD PRODUCTS**

| Part Number     | Description                               | Part Number | Description                               |

|-----------------|-------------------------------------------|-------------|-------------------------------------------|

| 85C30           | Enhanced Serial Communcaiton Controller   | Am386™      | High-Performance 32-Bit<br>Microprocessor |

| 26LSXX          | Line Drivers/Receivers                    | 80188       | Highly Integrated 8-Bit Microprocessor    |

| 33C93A          | Enhanced CMOS SCSI Bus                    | 53C80A      | SCSI Bus Controller                       |

|                 | Interface Controller                      | 85C80       | Combination 53C80A SCSI and               |

| 80C186          | Highly Integrated 16-Bit                  |             | 85C30 ESCC                                |

|                 | Microprocessor                            | 53C94LV     | Low Voltage, High Performance             |

| 80C286<br>80286 | High-Performance 16-Bit<br>Microprocessor |             | SCSI Controller                           |

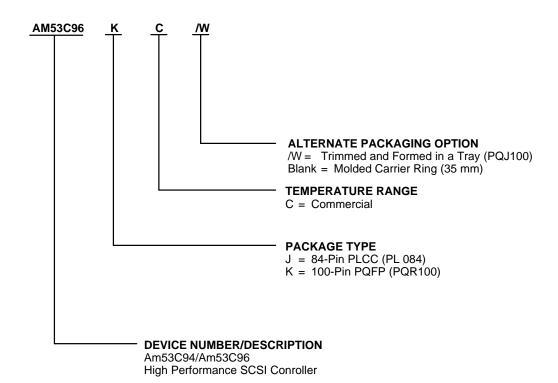

# ORDERING INFORMATION Standard Products

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of:

| Valid Combinations |          |  |  |  |  |  |

|--------------------|----------|--|--|--|--|--|

| AM53C94 JC         |          |  |  |  |  |  |

| AM53C96            | KC, KC/W |  |  |  |  |  |

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check on newly released combinations.

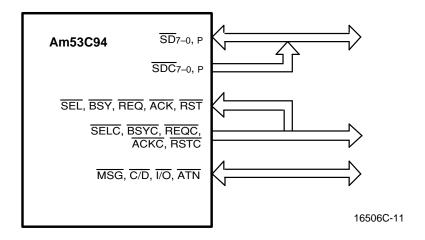

### **SCSI OUTPUT CONNECTIONS**

Am53C94 Single Ended SCSI Bus Configuration

### **SCSI OUTPUT CONNECTIONS**

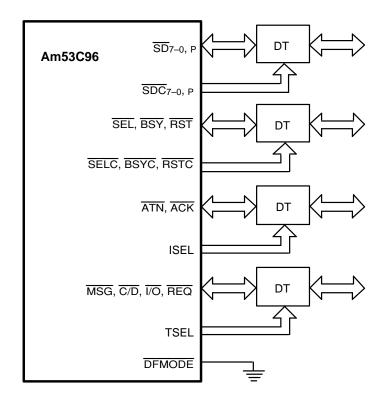

### Am53C96 Single Ended SCSI Bus Configuration

16506C-12

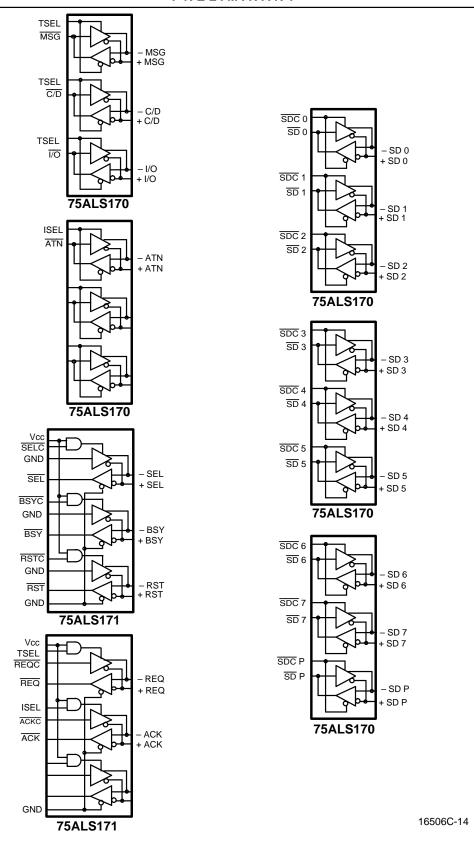

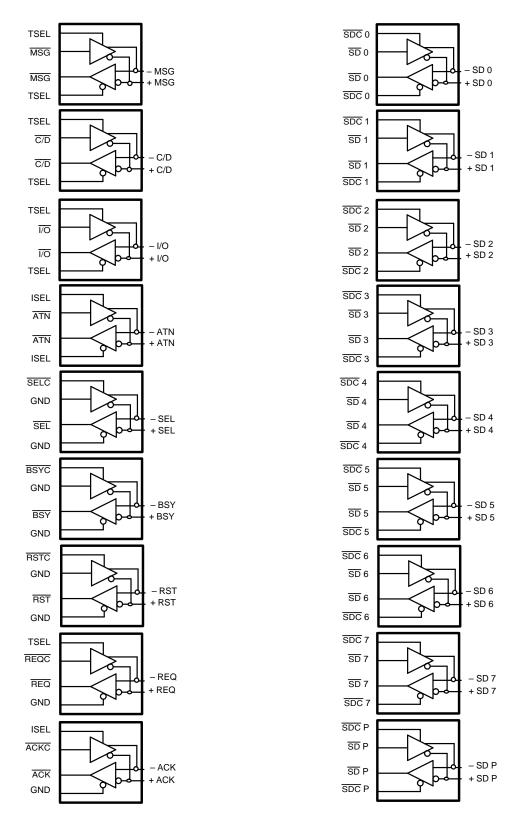

Am53C96 Differential SCSI Bus Configuration

Differential Transceiver Connections for the Differential SCSI Bus Configuration Using 75ALS170 and 75ALS171 Transceivers

16506C-15

Differential Transceiver Connections for the Differential SCSI Bus Configuration Using 75176A Transceiver

# PIN DESCRIPTION Host Interface Signals

### **DMA 15-0**

## Data/DMA Bus (Input/Output, Active High, Internal Pull-up)

The configuration of this bus depends on the Bus Mode 1–0 (BUSMD 1–0) inputs. When the device is configured for a single bus operation, the host can access the internal register set on the lower eight lines and the DMA accesses can be made to the FIFO using entire bus. When using the Byte Mode via the BHE and A0 inputs the data can be transferred on either the upper or lower half of the DMA 15–0 bus.

#### **DMAP 1-0**

### Data/DMA Parity Bus (Input/Output, Active High, Internal Pull-up)

These lines are odd parity for the DMA 15–0 bus. DMAP 1 is the parity for the upper half of the bus DMA 15–8 and DMAP 0 is the parity for the lower half of the bus DMA 7–0.

### ALE [A3]

## Address Latch Enable [Address 3] (Input, Active High)

This is a dual function input. When the device is configured for the dual bus mode (two buses, multiplexed and byte control), this input acts as ALE. As ALE, this input latches the address on the AD 7–0 bus on its Low going edge. When the device is configured for all other bus modes, this input acts as A3. As A3, this input is the third bit of the address bus.

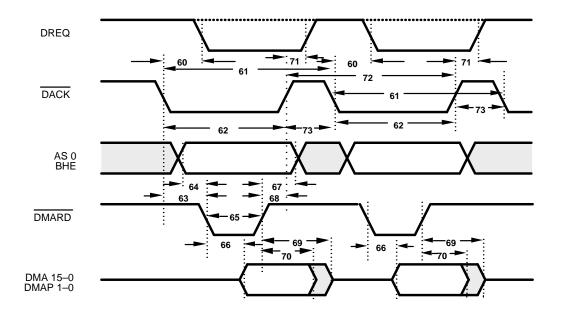

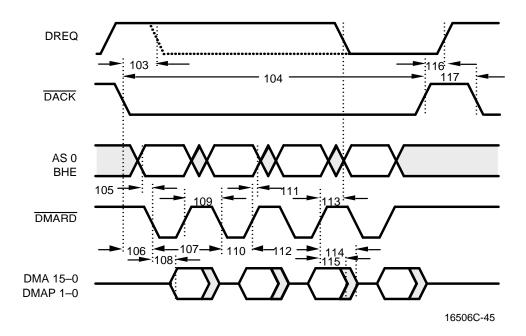

### DMARD [A2]

### DMA Read [Address 2] (Input, Active Low [Active High])

This is a dual function input. When the device is configured for the dual bus mode (two buses, multiplexed and byte control), this input acts as  $\overline{DMARD}$ . As  $\overline{DMARD}$ , this input is the read signal for the DMA 15–0 bus. When the device is configured for all other bus modes, this input acts as A2. As A2, this input is the second bit of the address bus.

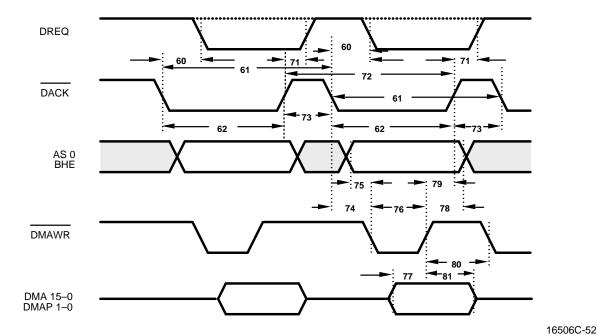

### **BHE** [A1]

## Bus High Enable [Address 1] (Input, Active High)

This is a dual function input. When the device is configured for the dual bus mode (two buses, multiplexed and byte control), this input acts as BHE. As BHE, this input works in conjunction with AS0 to indicate the lines on which data transfer will take place. When the device is configured for all other bus modes this input acts as A1. As A1, this input is the first bit of the address bus.

### AS0 [A0]

## Address Status [Address 0] (Input, Active High)

This is a dual function input. When the device is configured for the dual bus mode (two buses, multiplexed and byte control), this input acts as ASO. As ASO, this input works in conjunction with BHE to indicate the lines on which data transfer will take place. When the device is configured for all other bus modes, this input acts as AO. As AO, this input is the zeroth bit of the address bus.

The following is the decoding for the BHE and AS0 inputs:

| BHE | AS0 | Bus Used                      |

|-----|-----|-------------------------------|

| 1   | 1   | Upper Bus – DMA 15–8, DMAP 1  |

| 1   | 0   | Full Bus – DMA 15–0, DMAP 1–0 |

| 0   | 1   | Reserved                      |

| 0   | 0   | Lower Bus – DMA 7–0, DMAP 0   |

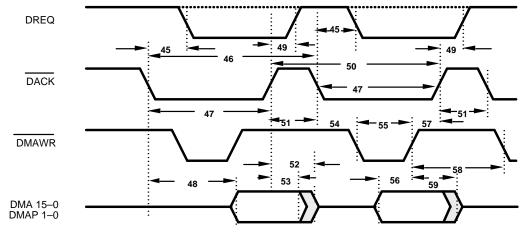

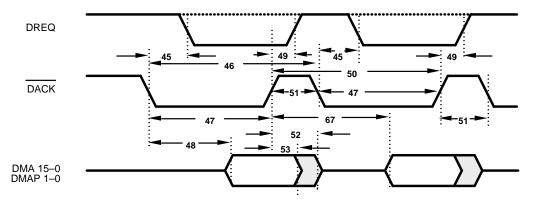

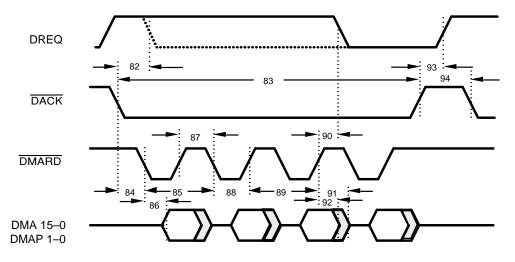

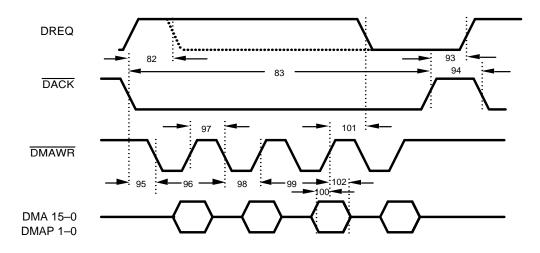

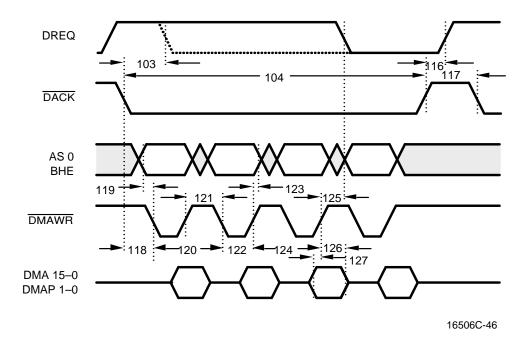

### **DREQ**

### DMA Request (Output, Active High, Hi-Z)

This output signal to the DMA controller will be active during DMA read and write cycles. During a DMA read cycle it will be active as long as there is a word (or a byte in the byte mode) in the FIFO to be transferred to memory. During a DMA write cycle it will be active as long as there is an empty space for a word (or a byte in the byte mode) in the FIFO.

### **DACK**

## DMA Acknowledge (Input, Active Low)

This input signal from the DMA controller will be active during DMA read and write cycles. The DACK signal is used to access the DMA FIFO only and should never be active simultaneously with the CS signal, which accesses the registers only.

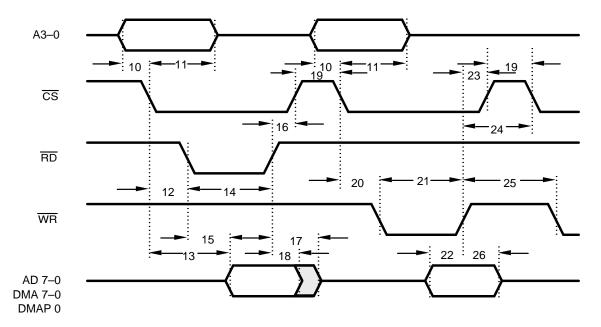

#### AD 7-0

## Host Address Data Bus (Input/Output, Active High, Internal Pull-up)

This bus is used only in the dual bus mode. This bus allows the host processor to access the device's internal registers while the DMA bus is transferring data. When using multiplexed bus, these lines can be used for address and data. When using non multiplexed bus these lines can be used for the data only.

#### **DMAWR**

### **DMA Write**

### (Input, Active Low)

This signal writes the data on the DMA 15–0 bus into the internal FIFO when  $\overline{D}ACK$  is also active. When in the single bus mode this signal must be tied to the  $\overline{W}R$  signal.

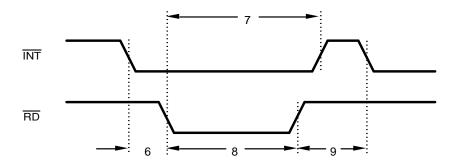

#### $\overline{RD}$

### Read

#### (Input Active Low)

This signal reads the internal device registers and places their contents on the data bus, when either  $\overline{\text{CS}}$  signal or  $\overline{\text{DACK}}$  signal is active.

#### $\overline{\mathsf{WR}}$

#### Write

### (Input Active Low)

This signal writes the internal device registers with the value present on the data bus, when the  $\overline{CS}$  signal is also active.

### $\overline{CS}$

## Chip Select (Input Active Low)

This signal enables the read and write of the device registers.  $\overline{CS}$  enables access to any register (including the FIFO) while the  $\overline{DACK}$  enables access only to the FIFO.  $\overline{CS}$  and  $\overline{DACK}$  should never be active simultaneously in the single bus mode, they may however be active simultaneously in the dual bus mode provided the  $\overline{CS}$  signal is not enabling access to the FIFO.

### **INT**

### Interrupt

### (Output, Active Low, Open Drain)

This signal is a non maskable interrupt flag to the host processor. This signal is latched on the output on the high going edge of the clock. This flag may be cleared by reading the Interrupt Status Register (ISTAT) or by performing a device reset (hard or soft). This flag is not cleared by a SCSI reset.

### **DFMODE**

## Differential Mode (Input, Active Low)

This input is available only on the Am53C96. This input configures the SCSI bus to either single ended or differential mode. When this input is active, the device operates in the differential SCSI mode. The SCSI data is available on the  $\overline{\text{SD}}$  7–0 lines and the high active transceiver enables on the  $\overline{\text{SDC}}$  7–0 outputs. When this input is inactive, the device operates in the single ended SCSI mode. The SCSI input data is available on  $\overline{\text{SD}}$  7–0 lines and the output data is available on  $\overline{\text{SDC}}$  7–0 lines. In the single ended SCSI mode, the  $\overline{\text{SD}}$  7–0 and the  $\overline{\text{SDC}}$  7–0 buses can be tied together externally.

#### BUSMD 1-0

### **Bus Mode**

### (Input, Active High)

These inputs configure the device for single bus or dual bus operation and the DMA width.

| BUSMD1 | BUSMD0 | Bus Configuration                                                                                    |

|--------|--------|------------------------------------------------------------------------------------------------------|

| 1      | 1      | Two buses: 8-bit Host Bus<br>and 16-bit DMA Bus<br>Register Address on A 3–0<br>and Data on AD Bus   |

| 1      | 0      | Two buses: Multiplexed<br>and byte control<br>Register Address on AD 3–0<br>and Data on AD Bus       |

| 0      | 1      | Single bus: 8-bit Host Bus<br>and 16-bit DMA Bus<br>Register Address on A 3–0<br>and Data on DMA Bus |

| 0      | 0      | Single bus: 8-bit Host Bus<br>and 8-bit DMA Bus<br>Register Address on A 3–0<br>and Data on DMA Bus  |

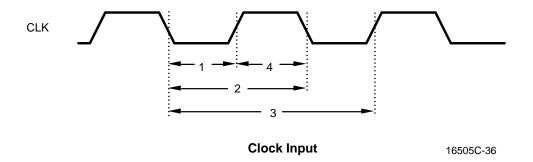

### CLK

### Clock

### (Input)

Clock input used to generate all the internal device timings. The maximum frequency of this input is 25 MHz. and a minimum of 10 MHz to maintain the SCSI bus timings.

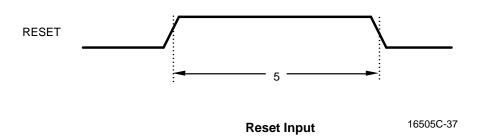

### **RESET**

#### Reset

### (Input, Active High)

This input when active resets the device. The RESET input must be active for at least two CLK periods after the voltage on the power inputs have reached Vcc minimum.

### **SCSI Interface Signals**

### SD 7-0

### **SCSI Data**

### (Input/Output, Active Low, Schmitt Trigger)

When the device is configured in the Single Ended SCSI Mode (DFMODE inactive) these pins are defined as inputs for the SCSI data bus. When the device is configured in the Differential SCSI Mode (DFMODE active) these pins are defined as bidirectional SCSI data bus.

#### **SD**<sub>P</sub>

### **SCSI Data Parity**

### (Input/Output, Active Low, Schmitt Trigger)

When the device is configured in the Single Ended SCSI Mode (DFMODE inactive) this pin is defined as the input for the SCSI data parity. When the device is configured in the Differential SCSI Mode (DFMODE active) this pin is defined as bidirectional SCSI data parity.

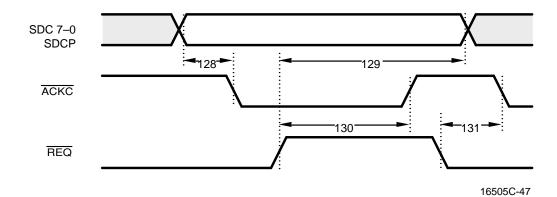

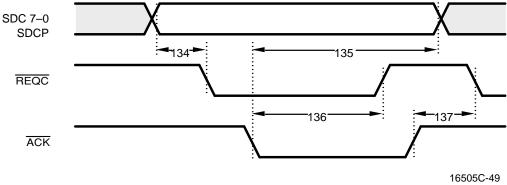

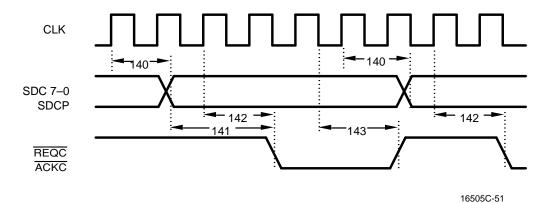

#### **SDC** 7-0

## SCSI Data Control (Output, Active Low, Open Drain)

When the device is configured in the Single Ended SCSI Mode (DFMODE inactive) these pins are defined as outputs for the SCSI data bus. When the device is configured in the Differential SCSI Mode (DFMODE active) these pins are defined as direction controls for the external differential transceivers. In this mode, a signal high state corresponds to an output to the SCSI bus and a low state corresponds to an input from the SCSI bus.

#### **SDC**<sub>P</sub>

## SCSI Data Control Parity (Output, Active Low, Open Drain)

When the device is configured in the Single Ended SCSI Mode (DFMODE inactive) this pin is defined as an output for the SCSI data parity. When the device is configured in the Differential SCSI Mode (DFMODE active) this pin is defined as the direction control for the external differential transceiver. In this mode, a signal high state corresponds to an output to the SCSI bus and a low state corresponds to an input from the SCSI bus.

### **MSG**

### Message

### (Input/Output, Active Low, Schmitt Trigger)

This is a bidirectional signal with 48 mA output driver. It is an output in the target mode and a Schmitt trigger input in the initiator mode.

### C/D

## Command/Data (Input/Output, Schmitt Trigger)

This is a bidirectional signal with 48 mA output driver. It is an output in the target mode and a Schmitt trigger input in the initiator mode.

#### **1/0**

## Input/Output (Input/Output, Schmitt Trigger)

This is a bidirectional signal with 48 mA output driver. It is an output in the target mode and a Schmitt trigger input in the initiator mode.

#### ATN

#### Attention

### (Input/Output, Active Low, Schmitt Trigger)

This signal is a 48 mA output in the initiator mode and a Schmitt trigger input in the target mode. This signal will be asserted when the initiator detects a parity error or it can be asserted via certain initiator commands.

#### **BSY**

### **Busy**

### (Input, Active Low, Schmitt Trigger)

This is a SCSI input signal with a Schmitt trigger.

### **SEL**

#### Select

### (Input, Active Low, Schmitt Trigger)

This is a SCSI input signal with a Schmitt trigger.

### **RST**

#### Reset

### (Input, Active Low, Schmitt Trigger)

This is a SCSI input signal with a Schmitt trigger.

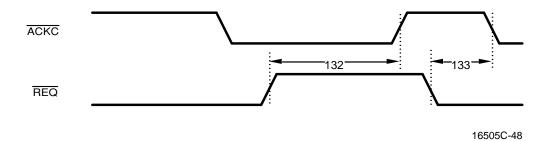

#### REQ

#### Request

### (Input, Active Low, Schmitt Trigger)

This is a SCSI input signal with a Schmitt trigger.

#### **ACK**

### Acknowledge

### (Input, Active Low, Schmitt Trigger)

This is a SCSI input signal with a Schmitt trigger.

#### **BSYC**

### **Busy Control**

### (Output, Active Low, Open Drain)

This is a SCSI output with 48 mA drive. When the device is configured in the Single Ended SCSI Mode (DFMODE inactive) this pin is defined as a BSY output for the SCSI bus. When the device is configured in the Differential SCSI Mode (DFMODE active) this pin is defined as the direction control for the external differential transceiver. In this mode, a signal high state corresponds to an output to the SCSI bus and a low state corresponds to an input from the SCSI bus.

#### **SELC**

## Select Control (Output, Active Low, Open Drain)

This is a SCSI output with 48 mA drive. When the device is configured in the Single Ended SCSI Mode (DFMODE inactive) this pin is defined as a SEL output for the SCSI bus. When the device is configured in the Differential SCSI Mode (DFMODE active) this pin is defined as the direction control for the external differential transceiver. In this mode, a signal high state corresponds to an output to the SCSI bus and a low state corresponds to an input from the SCSI bus.

### **RSTC**

## Reset Control (Output, Active Low, Open Drain)

This is a SCSI output with 48 mA drive. The Reset SCSI command will cause the device to drive  $\overline{\text{RSTC}}$  active for 25 ms–40 ms, which will depend on the CLK frequency and the conversion factor. When the device is configured in the Single Ended SCSI Mode ( $\overline{\text{DFMODE}}$  inactive) this pin is defined as a RST output for the SCSI bus. When the device is configured in the Differential SCSI Mode ( $\overline{\text{DFMODE}}$  active) this pin is defined as the direction control for the external differential transceiver. In this mode, a signal high state corresponds to an output to the SCSI bus and a low state corresponds to an input from the SCSI bus.

#### REQC

## Request Control (Output, Active Low, Open Drain)

This is a SCSI output with 48 mA drive. This signal is activated only in the target mode.

#### **ACKC**

## Acknowledge Control (Output, Active Low, Open Drain)

This is a SCSI output with 48 mA drive. This signal is activated only in the initiator mode.

#### **ISEL**

## Initiator Select (Output, Active High)

This signal is available on the Am53C96 only. This signal is active whenever the device is in the initiator mode. In the differential mode this signal is used to enable the initiator signals  $\overline{ACKC}$  and  $\overline{ATN}$  and the device also drives these signals.

#### **TSEL**

## Target Select (Output, Active High)

This signal is available on the Am53C96 only. This signal is active whenever the device is in the target mode. In the differential mode this signal is used to enable the target signals  $\overline{REQC}$ ,  $\overline{MSG}$ ,  $\overline{C/D}$  and  $\overline{I/O}$  and the device also drives these signals.

### **FUNCTIONAL DESCRIPTION**

### **Register Map**

| Address<br>(Hex.) | Operation  | Register                               | Address<br>(Hex.) | Operation  | Register                                |

|-------------------|------------|----------------------------------------|-------------------|------------|-----------------------------------------|

| 00                | Read       | Current Transfer Count<br>Register LSB | 06                | Read       | Internal State Register                 |

| 00                | Write      | Start Transfer Count Register LSB      | 06                | Write      | Synchronous Transfer Period<br>Register |

| 01                | Read       | Current Transfer Count<br>Register MSB | 07                | Read       | Current FIFO/Internal State<br>Register |

| 01                | Write      | Start Transfer Count Register          | 07                | Write      | Synchronous Offset Register             |

|                   |            | MSB                                    | 08                | Read/Write | Control Register 1                      |

| 02                | Read/Write | FIFO Register                          | 09                | Write      | Clock Factor Register                   |

| 03                | Read/Write | Command Register                       | 0A                | Write      | Forced Test Mode Register               |

| 04                | Read       | Status Register                        | 0B                | Read/Write | Control Register 2                      |

| 04                | Write      | SCSI Destination ID Register           | 0C                | Read/Write | Control Register 3                      |

| 05                | Read       | Interrupt Status Register              |                   |            | 3                                       |

| 05                | Write      | SCSI Timeout Register                  | 0F                | Write      | Data Alignment Register                 |

#### Note:

Not all registers in this device are both readable and writable. Some read only registers share the same address with write only registers. The registers can be accessed by asserting the  $\overline{CS}$  signal and then asserting either  $\overline{RD}$  or  $\overline{WR}$  signal depending on the operation to be performed. Only the FIFO Register can be accessed by asserting either  $\overline{CS}$  or  $\overline{DACK}$  in conjunction with  $\overline{RD}$  and  $\overline{WR}$  signals or  $\overline{DMARD}$  and  $\overline{DMAWR}$  signals. The register address inputs are ignored when  $\overline{DACK}$  is used but must be valid when  $\overline{CS}$  is used.

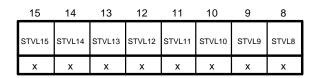

## Current Transfer Count Register (00H–01H) Read Only

Current Transfer Count Register Address: 00H-01H CTCREG Type: Read

| 15     | 14     | 13     | 12     | 11 10  |        | 9     | 8     |

|--------|--------|--------|--------|--------|--------|-------|-------|

| CRVL15 | CRVL14 | CRVL13 | CRVL12 | CRVL11 | CRVL10 | CRVL9 | CRVL8 |

| Х      | х      | Х      | Х      | х      | Х      | Х     | х     |

| 7      | 6      | 5      | 4      | 3      | 2      | 1     | 0     |

| CRVL7  | CRVL6  | CRVL5  | CRVL4  | CRVL3  | CRVL2  | CRVL1 | CRVL0 |

| Х      | х      | Х      | х      | Х      | Х      | Х     | Х     |

16506C-16

## CTCREG - Bits 15:0 - CRVL 15:0 - Current Value 15:0

This is a two-byte register. It counts down to keep track of the number of DMA transfers. Reading this registers will return the current value of the counter. The counter will decrement by one for every byte transferred and two for every word transferred over the SCSI bus. The transaction is complete when the count reaches zero. These registers are automatically loaded with the values in the Start Transfer Count Register every time a DMA command is issued.

In the target mode, this counter is decremented by the active edge of  $\overline{DACK}$  during the Data-In phase and by  $\overline{REQC}$  during the Data-Out phase.

In the initiator mode, the counter is decremented by the active edge of  $\overline{DACK}$  during the Synchronous Data-In phase or by  $\overline{ACKC}$  during the Asynchronous Data-In phase and by  $\overline{DACK}$  during the Data-Out phase.

# Start Transfer Count Register (00H–01H) Write Only

Start Transfer Count Register Address: 00H-01H STCREG Type: Write

|       | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|

| STVL7 | STVL6 | STVL5 | STVL4 | STVL3 | STVL2 | STVL1 | STVL0 |

| Х     | х     | Х     | Х     | Х     | Х     | Х     | Х     |

16506C-017

### STCREG - Bits 15:0 - STVL 15:0 - Start Value 15:0

This is a two-byte register. It contains the number of bytes to be transferred during a DMA operation. The value of this register is set to the number of bytes to be transferred prior to a DMA transfer command. This register retains its programmed value until it is overwritten and is not affected by hardware or software reset. Therefore, it is not necessary to reprogram the count for subsequent DMA transfers of the same size. Writing a zero to this register sets a maximum transfer count of 65536 bytes. The value in this register is undefined at power-up.

### FIFO Register (02H) Read/Write

| FIFO Register Address: 02: FFREG Type: Read/Write |     |     |     |     |     |     |     |   |  |  |

|---------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|---|--|--|

| 7                                                 | 6   | 5   | 4   | 3   | 2   | 1   | 0   | _ |  |  |

| FF7                                               | FF6 | FF5 | FF4 | FF3 | FF2 | FF1 | FF0 |   |  |  |

| 0                                                 | 0   | 0   | 0   | 0   | 0   | 0   | 0   |   |  |  |

16506C-18

#### FFREG - Bits 7:0 - FF 7:0 - FIFO 7:0

The bottom of the 16x9 FIFO is mapped into the FIFO Register address. By reading and writing this register the bottom of the FIFO can be read or written. This is the only register that can also be accessed by DACK along with DMARD or DMAWR. This register is reset to zero by hardware or software reset and also at the start of a selection or reselection sequence.

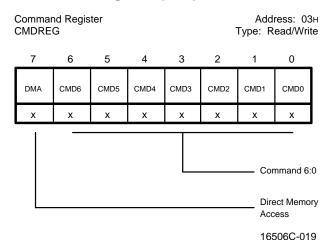

### Command Register (03H) Read/Write

Commands to the device are issued by writing to this register. This register is two deep which allows for command queuing. The second command can be issued before the first one is completed. The Reset command and the Stop DMA command are not queued and are executed immediately. Reading this register will return the command currently being executed (or the last command executed if there are no pending commands).

### CMDREG - Bit 7 - DMA - Direct Memory Access

The DMA bit when set notifies the device that the command is a DMA instruction, when reset it is a non-DMA instruction. For DMA instructions the Current Transfer Count Register (CTCREG) will be loaded with the contents of the Start Transfer Count Register (STCREG). The data is then transferred and the CTCREG is decremented for each byte until it reaches zero.

### CMDREG - Bits 6:0 - CMD 6:0 - Command 6:0

These command bits decode the commands that the device needs to perform. There are a total of 29 commands grouped into four categories. The groups are Initiator Commands, Target Commands, Selection/Reselection Commands and General Purpose Commands.

### **Initiator Commands**

| CMD6 | CMD5 | CMD4 | CMD3 | CMD2 | CMD1 | CMD0 | Command                          |

|------|------|------|------|------|------|------|----------------------------------|

| 0    | 0    | 1    | 0    | 0    | 0    | 0    | Information Transfer             |

| 0    | 0    | 1    | 0    | 0    | 0    | 1    | Initiator Command Complete Steps |

| 0    | 0    | 1    | 0    | 0    | 1    | 0    | Message Accepted                 |

| 0    | 0    | 1    | 1    | 0    | 0    | 0    | Transfer Pad Bytes               |

| 0    | 0    | 1    | 1    | 0    | 1    | 0    | Set ATN                          |

| 0    | 0    | 1    | 1    | 0    | 1    | 1    | Reset ATN                        |

### **Target Commands**

| CMD6 | CMD5 | CMD4 | CMD3 | CMD2 | CMD1 | CMD0 | Command                       |

|------|------|------|------|------|------|------|-------------------------------|

| 0    | 1    | 0    | 0    | 0    | 0    | 0    | Send Message                  |

| 0    | 1    | 0    | 0    | 0    | 0    | 1    | Send Status                   |

| 0    | 1    | 0    | 0    | 0    | 1    | 0    | Send Data                     |

| 0    | 1    | 0    | 0    | 0    | 1    | 1    | Disconnect Steps              |

| 0    | 1    | 0    | 0    | 1    | 0    | 0    | Terminate Steps               |

| 0    | 1    | 0    | 0    | 1    | 0    | 1    | Target Command Complete Steps |

| 0    | 1    | 0    | 0    | 1    | 1    | 1    | Disconnect                    |

| 0    | 1    | 0    | 1    | 0    | 0    | 0    | Receive Message Steps         |

| 0    | 1    | 0    | 1    | 0    | 0    | 1    | Receive Command               |

| 0    | 1    | 0    | 1    | 0    | 1    | 0    | Receive Data                  |

| 0    | 1    | 0    | 1    | 0    | 1    | 1    | Receive Command Steps         |

| 0    | 0    | 0    | 0    | 1    | 0    | 0    | DMA Stop                      |

### **Idle Commands**

| idic ooi | iiiiaiias |      |      |      |      |      |                                |

|----------|-----------|------|------|------|------|------|--------------------------------|

| CMD6     | CMD5      | CMD4 | CMD3 | CMD2 | CMD1 | CMD0 | Command                        |

| 1        | 0         | 0    | 0    | 0    | 0    | 0    | Reselect Steps                 |

| 1        | 0         | 0    | 0    | 0    | 0    | 1    | Select without ATN Steps       |

| 1        | 0         | 0    | 0    | 0    | 1    | 0    | Select with ATN Steps          |

| 1        | 0         | 0    | 0    | 0    | 1    | 1    | Select with ATN and Stop Steps |

| 1        | 0         | 0    | 0    | 1    | 0    | 0    | Enable Selection/Reselection   |

| 1        | 0         | 0    | 0    | 1    | 0    | 1    | Disable Selection/Reselection  |

| 1        | 0         | 0    | 0    | 1    | 1    | 0    | Select with ATN3 Steps         |

| 1        |           | I    | I    | ı    | I    | ı    |                                |

#### **General Commands**

| CMD6 | CMD5 | CMD4 | CMD3 | CMD2 | CMD1 | CMD0 | Command        |

|------|------|------|------|------|------|------|----------------|

| 0    | 0    | 0    | 0    | 0    | 0    | 0    | No Operation   |

| 0    | 0    | 0    | 0    | 0    | 0    | 1    | Clear FIFO     |

| 0    | 0    | 0    | 0    | 0    | 1    | 0    | Reset Device   |

| 0    | 0    | 0    | 0    | 0    | 1    | 1    | Reset SCSI Bus |

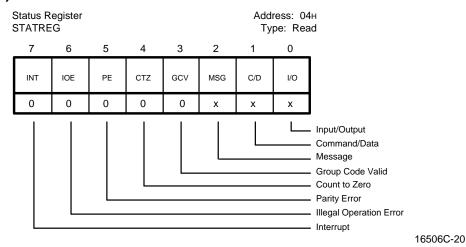

### Status Register (04H) Read

This read only register contains flags to indicate the status and phase of the SCSI transactions. It indicates whether an interrupt or error condition exists. It should be read every time the host is interrupted to determine which device is asserting an interrupt. The data is latched until the Interrupt Status Register is read. The phase bits will be latched only if latching is enabled in the Control Register 2, otherwise, it will indicate the current SCSI phase. If command stacking is used, two interrupts might occur. Reading this register will clear the status information for the first interrupt and update the Status Register for the second interrupt.

### STATREG - Bit 7 - INT - Interrupt

The INT bit is set when the device asserts the interrupt output. This bit will be cleared by a hardware or software reset. Reading the Interrupt Status Register will deassert the interrupt output and also clear this bit.

### STATREG - Bit 6 - IOE - Illegal Operation Error

The IOE bit is set when an illegal operation is attempted. This condition will not cause an interrupt, it will be detected by reading the status register while servicing another interrupt. The following conditions will cause the IOE bit to be set:

- DMA and SCSI transfer directions are opposite.

- FIFO overflows.

- In initiator mode an unexpected phase change detected during synchronous data transfer.

- Command Register overwritten.

This bit will be cleared by reading the Interrupt Status Register or by a hard or soft reset.

#### STATREG - Bit 5 - PE - Parity Error

The PE bit is set if the parity checking option is enabled in Control Register 1 and the device detects a parity error on incoming SCSI data, command, status or message bytes. Detection of a parity error condition will not cause an interrupt but will be reported with other interrupt causing conditions. When a parity error is detected in the information phase of the initiator mode  $\overline{\text{ATN}}$  is asserted on the SCSI bus.

This bit will be cleared by reading the Interrupt Status Register or by a hard or soft reset.

### STATREG - Bit 4 - CTZ - Count To Zero

The CTZ bit is set when the Current Transfer Count Register (CTCREG) has counted down to zero. This bit will be reset when the CTCREG is written.

Reading the Interrupt Status Register will not affect this bit. This bit will however be cleared by a hard or soft reset.

#### Note:

A non-DMA NOP will not reset the CTZ bit since it does not load the CTCREG but a DMA NOP will reset this bit since it loads the CTCREG.

### STATREG - Bit 3 - GCV - Group Code Valid

The GCV bit is set if the group code field in the Command Descriptor Block (CDB) is one that is defined by the ANSI Committee in their document X3.131 – 1986. If the SCSI-2 Feature Enable (S2FE) bit in the Control Register 2 (CNTLREG2) is set, Group 2 commands will be treated as ten byte commands and the GCV bit will be set. If S2FE is reset then Group 2 commands will be treated as reserved commands. Group 3 and 4 command will always be considered as reserved commands. The device will treat all reserved commands as six byte commands. Group 6 commands will always be treated as vendor unique six byte commands and Group 7 commands will always be treated as vendor unique ten byte commands.

The GCV bit is cleared by reading the Interrupt Status Register (INSTREG) or by a hard or soft reset.

STATREG - Bit 2 - MSG - Message

STATREG - Bit 1 - C/D - Command/Data

STATREG - Bit 0 - I/O - Input/Output

| Bit2<br>MSG | Bit1<br>C/D | Bit0<br>I/O | SCSI Phase  |

|-------------|-------------|-------------|-------------|

| 1           | 1           | 1           | Message In  |

| 1           | 1           | 0           | Message Out |

| 1           | 0           | 1           | Reserved    |

| 1           | 0           | 0           | Reserved    |

| 0           | 1           | 1           | Status      |

| 0           | 1           | 0           | Command     |

| 0           | 0           | 1           | Data_In     |

| 0           | 0           | 0           | Data_Out    |

|             |             |             |             |

The MSG, C/D and I/O bits together can be referred to as the SCSI Phase bits. They indicate the phase of the SCSI bus. These bits may be latched or unlatched depending on the option selected in Control Register 2 (CNTLREG2) by the Latch SCSI Phase (LSP) bit.

In the latched mode the SCSI phase bits are latched at the end of a command and the latch is opened when the Interrupt Status Register (INSTREG) is read. In the unlatched mode, they indicate the phase of the SCSI bus when this register is read.

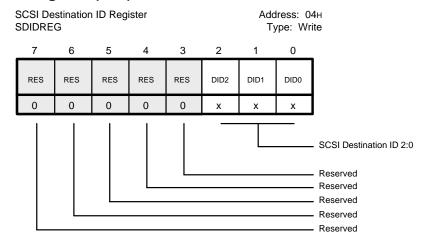

### SCSI Destination ID Register (04H) Write

16506C-21

SDIDREG - Bits 7:3 - RES - Reserved

### SDIDREG - Bits 2:0 - DID 2:0 - Destination ID 2:0

The DID 2:0 bits are the encoded SCSI ID of the device on the SCSI bus which needs to be selected or reselected.

| DID2 | DID1 | DID0 | SCSI ID |

|------|------|------|---------|

| 1    | 1    | 1    | 7       |

| 1    | 1    | 0    | 6       |

| 1    | 0    | 1    | 5       |

| 1    | 0    | 0    | 4       |

| 0    | 1    | 1    | 3       |

| 0    | 1    | 0    | 2       |

| 0    | 0    | 1    | 1       |

| 0    | 0    | 0    | 0       |

At power-up the state of these bits is undefined. The DID 2:0 bits are not affected by reset.

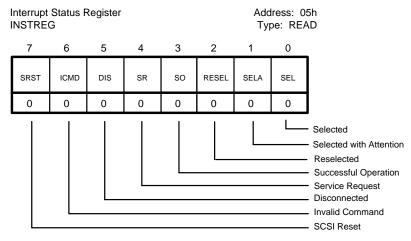

### Interrupt Status Register (05H) Read

16506C-22

The Interrupt Status Register (INSTREG) will indicate the reason for the interrupt. This register is used with the Status Register (STATREG) and Internal Status Register (ISREG) to determine the reason for the interrupt. Reading the INSTREG will clear all three registers.

#### INSTREG - Bit 7 - SRST - SCSI Reset

The SRST bit will be set if a SCSI Reset is detected and SCSI reset reporting is enabled via the DISR (bit 6) of the CNTLREG1.

### INSTREG - Bit 6 - ICMD - Invalid Command

The ICMD bit will be set if the device detects an illegal command code. This bit is also set if a command code from a different mode is detected than the mode the device is currently in.

### INSTREG - Bit 5 - DIS - Disconnected

The DIS bit can be set in the target or the initiator mode when the device disconnects from the SCSI bus. In the target mode this bit will be set if a terminate or a command complete sequence causes the device to disconnect from the SCSI bus. In the Initiator mode this bit will be set if the target disconnects or a selection or reselection timeout occurs.

### INSTREG - Bit 4 - SR - Service Request

The SR bit can be set in the target or the initiator mode when another device on the SCSI bus has a service re-

quest. In the target mode this bit will be set when the initiator asserts the  $\overline{\text{ATN}}$  signal. In the Initiator mode this bit is set whenever the target requests an information transfer phase.

### INSTREG - Bit 3 - SO - Successful Operation

The SO bit can be set in the target or the initiator mode when an operation is successfully complete. In the target mode this bit will be set when any target mode command is completed. In the initiator mode this bit is set after a target has been successfully selected, after a command is successfully completed and after an information transfer command when the target requests a message in phase.

### INSTREG - Bit 2 - RESEL - Reselected

The RESEL bit is set at the end of the reselection phase indicating that the device has been reselected as an initiator.

#### INSTREG - Bit 1 - SELA - Selected with Attention

The SELA bit is set at the end of the selection phase indicating that the device has been selected and that the ATN signal was active during the selection.

### INSTREG - Bit 0 - SEL - Selected

The SEL bit is set at the end of the selection phase indicating that the device has been selected and that the ATN signal was inactive during the selection.

### SCSI Timeout Register (05H) Write

| SCSI Timeout Register Address: 05i<br>STIMREG Type: Write |       |       |       |       |       |       |       |   |

|-----------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|---|

| 7                                                         | 6     | 5     | 4     | 3     | 2     | 1     | 0     | _ |

| STIM7                                                     | STIM6 | STIM5 | STIM4 | STIM3 | STIM2 | STIM1 | STIM0 |   |

| Х                                                         | х     | Х     | х     | Х     | Х     | х     | х     |   |

16506C-23

This register determines how long the initiator (target) will wait for a target to respond to a selection (reselection) before timing out. It should be set to yield 250 ms to comply with ANSI standards for SCSI.

### STIMREG - Bits 7:0 - STIM 7:0 - SCSI Timer 7:0

The value loaded in STIM 7:0 can be calculated from the following formula:

STIM 7:0 =

[(SCSI Time Out) (Clock Frequency) / (8192 (Clock Factor))]

Example:

SCSI Time Out (in seconds): 250 ms. (Recommended by the ANSI Standard) = 250 x 10–3 s.

Clock Frequency: 20 MHz. (assume) = 20 x 106 Hz.

Clock Factor: CLKF 2:0 from Clock Conversion Register (09H) = 5

STIM 7:0 =  $(250 \times 10-3) \times (20 \times 106) / (8192 (5)) = 122$  decimal

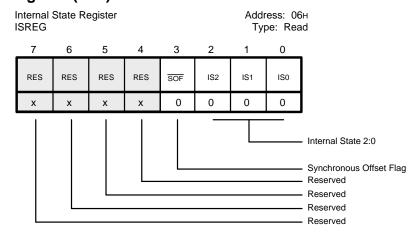

### Internal State Register (06H) Read

16506C-24

The Internal State Register (ISREG) tracks the progress of a sequence-type command. It is updated after each successful completion of an intermediate operation. If an error occurs, the host can read this register to determined at where the command failed and take the necessary procedure for recovery. Reading the Interrupt Status Register will clear this register.

ISREG - Bits 7:4 - RES - Reserved

### ISREG - Bit 3 - SOF - Synchronous Offset Flag

The SOF is reset when the Synchronous Offset Register (SOFREG) has reached its maximum value.

### Note:

The SOF bit is active Low.

#### ISREG - Bits 2:0 - IS 2:0 - Internal State 2:0

The IS 2:0 bits along with the Interrupt Status Register (INSTREG) indicates the status of the successfully completed intermediate operation. Refer to the Status Decode section for more details.

| Initiator Select                 | without ATN Steps                  |                                                                                                                                                                                                                            |

|----------------------------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Internal State<br>Register (06H) | Interrupt Status<br>Register (05H) | Explanation                                                                                                                                                                                                                |

| Bits 2:0 (Hex)                   | Bits 7:0 (Hex)                     |                                                                                                                                                                                                                            |

| 0                                | 20                                 | Arbitration steps completed or disconnected or selection time-out                                                                                                                                                          |

| 4                                | 18                                 | Selection with ATN steps fully executed                                                                                                                                                                                    |

| 3                                | 18                                 | Sequence halted during command transfer due to premature phase change (target)                                                                                                                                             |

| 2                                | 18                                 | Arbitration and selection completed; sequence halted because target failed to assert command phase                                                                                                                         |

| Initiator Select                 | with ATN Steps                     |                                                                                                                                                                                                                            |

| Internal State<br>Register (06H) | Interrupt Status<br>Register (05H) | Explanation                                                                                                                                                                                                                |

| Bits 2:0 (Hex)                   | Bits 7:0 (Hex)                     |                                                                                                                                                                                                                            |

| 4                                | 18                                 | Selection with ATN steps fully executed                                                                                                                                                                                    |

| 3                                | 18                                 | Sequence halted during command transfer due to premature phase change; some CDB bytes may not have been sent; check FIFO flags                                                                                             |

| 2                                | 18                                 | Message out completed; sent one message byte with ATN true, then released ATN; sequence halted because target failed to assert command phase after message byte was sent                                                   |

| 0                                | 18                                 | Arbitration and selection completed; sequence halted because target did not assert message out phase; ATN still driven by HPSC                                                                                             |

| Initiator Select                 | with ATN3 Steps                    |                                                                                                                                                                                                                            |

| Internal State<br>Register (06H) | Interrupt Status<br>Register (05H) | Explanation                                                                                                                                                                                                                |

| Bits 2:0 (Hex)                   | Bits 7:0 (Hex)                     |                                                                                                                                                                                                                            |

| 0                                | 20                                 | Arbitration steps completed or disconnected or selection time—out                                                                                                                                                          |

| 4                                | 18                                 | Selection with ATN3 steps fully executed                                                                                                                                                                                   |

| 3                                | 18                                 | Sequence halted during command transfer due to premature phase change; some CDB bytes may not have been sent; check FIFO flags                                                                                             |

| 2                                | 18                                 | One, two, or three message bytes sent; sequence halted because target failed to assert command phase after third message byte, or prematurely released message out phase; ATN released only if third message byte was sent |

| 0                                | 18                                 | Arbitration and selection completed; sequence halted because target failed to assert message out phase; ATN still driven by HPSC                                                                                           |

| Initiator Select                 | with ATN and Stop                  | Steps                                                                                                                                                                                                                      |

| Internal State<br>Register (06H) | Interrupt Status<br>Register (05H) | Explanation                                                                                                                                                                                                                |

| Bits 2:0 (Hex)                   | Bits 7:0 (Hex)                     |                                                                                                                                                                                                                            |

| 0                                | 20                                 | Arbitration steps completed or disconnected or selection time-out                                                                                                                                                          |

| 0                                | 18                                 | Arbitration and selection completed; sequence halted because target failed to assert message out phase; ATN still asserted by HPSC                                                                                         |

| 1                                | 18                                 | Message out completed; one message byte sent; ATN on                                                                                                                                                                       |

| <b>↓</b> AMD                     |                                    | PRELIMINARY                                                                                                                                                |

|----------------------------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Target Selected                  | I without ATN Step                 | s                                                                                                                                                          |

| Internal State<br>Register (06H) | Interrupt Status<br>Register (05H) | Explanation                                                                                                                                                |

| Bits 2:0 (Hex)                   | Bits 7:0 (Hex)                     | •                                                                                                                                                          |

| 2                                | 11                                 | Selected; received entire CDB; check group code valid bit; initiator asserted ATI in command phase                                                         |

| 1                                | 11                                 | Sequence halted in command phase due to parity error; some CDB bytes may not have been received; check FIFO flags; initiator asserted ATN in command phase |

| 2                                | 01                                 | Selected; received entire CDB; check group code valid bit                                                                                                  |

| 1                                | 01                                 | Sequence halted in command phase because of parity error; some CDB bytes may not have been received; check FIFO flags                                      |

| 0                                | 01                                 | Selected; loaded bus ID into FIFO; null-byte message loaded into FIFO                                                                                      |

| Target Select w                  | ith ATN Steps, SC                  | SI–2 Bit NOT SET                                                                                                                                           |

| Internal State<br>Register (06H) | Interrupt Status<br>Register (05H) | Explanation                                                                                                                                                |

| Bits 2:0 (Hex)                   | Bits 7:0 (Hex)                     | Explanation                                                                                                                                                |

| 2 (Hex)                          | 12                                 | Coloction complete: received and managed buts and entire CDP: initiator as                                                                                 |

| 2                                | 12                                 | Selection complete; received one message byte and entire CDB; initiator asserted ATN during command phase                                                  |

| 1                                | 12                                 | Halted in command phase; parity error and ATN true                                                                                                         |

| 0                                | 12                                 | Selected with ATN; stored bus ID and one message byte; sequence halted because ATN remained true after first message byte                                  |

| 2                                | 02                                 | Selection completed; received one message byte and the entire CDB                                                                                          |

| 1                                | 02                                 | Sequence halted in command phase because of parity error; some CDB bytes not received; check group code valid bit and FIFO flags                           |

| 0                                | 02                                 | Selected with ATN; stored bus ID and one message byte; sequence halted because of parity error or invalid ID message                                       |

| Target Select w                  | ith ATN Steps, SC                  | SI–2 Bit SET                                                                                                                                               |

| Internal State<br>Register (06H) | Interrupt Status<br>Register (05H) | Explanation                                                                                                                                                |

| Bits 2:0 (Hex)                   | Bits 7:0 (Hex)                     |                                                                                                                                                            |

| 5                                | 12                                 | Halted in command phase; parity error and ATN true                                                                                                         |

| 4                                | 12                                 | ATN remained true after third message byte                                                                                                                 |

| 0                                | 02                                 | Selected with ATN; stored bus ID and one message byte; sequence halted because of parity error or invalid ID message                                       |

| 6                                | 02                                 | Selection completed; received three message bytes and the entire CDB                                                                                       |

| 5                                | 02                                 | Received three message bytes then halted in command phase because of parit error; some CDB bytes not received; check group code valid bit and FIFO flags   |

| <u> </u>                         | error during second o              | r third message byte                                                                                                                                       |

| Internal State                   | Command Steps Interrupt Status     |                                                                                                                                                            |

| Register (06H)                   | Register (05H)                     | Explanation                                                                                                                                                |

| Bits 2:0 (Hex)                   | Bits 7:0 (Hex)                     |                                                                                                                                                            |

| 2                                | 18                                 | Received entire CDB; initiator asserted ATN                                                                                                                |

| 1                                | 18                                 | Sequence halted during command transfer due to parity error; ATN asserted by initiator                                                                     |

| 2                                | 08                                 | Received entire CDB                                                                                                                                        |

| 1                                | 08                                 | Sequence halted during command transfer due to parity error; check FIFO flags                                                                              |

| Target Disconn                   | <u>-</u>                           |                                                                                                                                                            |

| Internal State<br>Register (06H) | Interrupt Status<br>Register (05H) | Explanation                                                                                                                                                |

| Bits 2:0 (Hex)                   | Bits 7:0 (Hex)                     |                                                                                                                                                            |

| 2                                | 28                                 | Disconnect steps fully executed; disconnected; bus is free                                                                                                 |

| 1                                | 18                                 | Two message bytes sent; sequence halted because initiator asserted ATN                                                                                     |

| n                                | 18                                 | One message byte seet; sequence halted because initiator asserted ATN                                                                                      |

One message byte sent; sequence halted because initiator asserted ATN

0

18

### PRELIMINARY

| Target Terminate Steps                           |                                                      |                                                                               |  |  |  |

|--------------------------------------------------|------------------------------------------------------|-------------------------------------------------------------------------------|--|--|--|

| Internal State<br>Register (06H)                 | Interrupt Status<br>Register (05H)                   | Explanation                                                                   |  |  |  |

| Bits 2:0 (Hex)                                   | Bits 7:0 (Hex)                                       |                                                                               |  |  |  |

| 2                                                | 28                                                   | Terminate steps fully executed; disconnected; bus is free                     |  |  |  |

| 1                                                | 18                                                   | Status and message bytes sent; sequence halted because initiator asserted ATN |  |  |  |

| 0                                                | 18                                                   | Status byte sent; sequence halted because initiator asserted ATN              |  |  |  |

|                                                  |                                                      |                                                                               |  |  |  |

| arget Commar                                     | nd Complete Steps                                    |                                                                               |  |  |  |

| arget Commar<br>Internal State<br>Register (06H) | nd Complete Steps Interrupt Status Register (05H)    | Explanation                                                                   |  |  |  |

| Internal State                                   | Interrupt Status                                     |                                                                               |  |  |  |

| Internal State<br>Register (06H)                 | Interrupt Status<br>Register (05H)                   |                                                                               |  |  |  |

| Internal State<br>Register (06H)                 | Interrupt Status<br>Register (05H)<br>Bits 7:0 (Hex) | Explanation                                                                   |  |  |  |

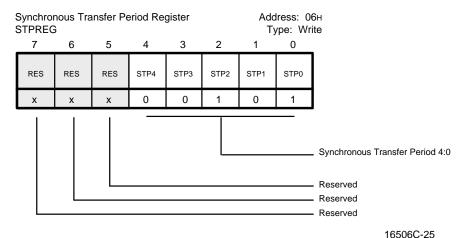

### Synchronous Transfer Period Register (06H) Write

The Synchronous Transfer Period Register (STPREG) contains a 5-bit value indicating the number of clock cycles each byte will take to be transferred over the SCSI bus in synchronous mode. The minimum value allowed is 5. The STPREG defaults to five after a hard or soft reset.

STPREG - Bits 7:5 - RES - Reserved

## STPREG – Bits 4:0 – STP 4:0 – Synchronous Transfer Period 4:0

The STP 4:0 bits are programmed to specify the synchronous transfer period or the number of clock cycles for each byte transfer in the synchronous mode. The minimum value for STP 4:0 is five. Missing table entries follow the binary code.

| STP4 | STP3 | STP2 | STP1 | STP0 | Clocks/<br>Byte |

|------|------|------|------|------|-----------------|

| 0    | 0    | 1    | 0    | 0    | 5               |

| 0    | 0    | 1    | 0    | 1    | 5               |

| 0    | 0    | 1    | 1    | 0    | 6               |

| 0    | 0    | 1    | 1    | 1    | 7               |

| •    | •    | •    | •    | •    | •               |

| •    | •    | •    | •    | •    | •               |

| 1    | 1    | 1    | 1    | 1    | 31              |

| 0    | 0    | 0    | 0    | 0    | 32              |

| 0    | 0    | 0    | 0    | 1    | 33              |

| 0    | 0    | 0    | 1    | 0    | 34              |

| 0    | 0    | 0    | 1    | 1    | 35              |

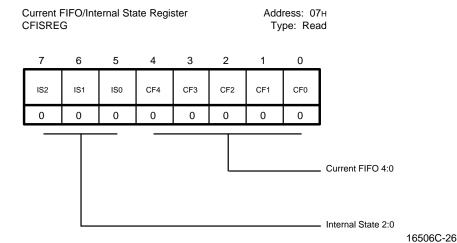

### Current FIFO/Internal State Register (07H) Read

This register has two fields, the Current FIFO field and the Internal State field.

#### CFISREG - Bits 7:5 - IS 2:0 - Internal State 2:0

The Internal State Register (ISREG) tracks the progress of a sequence-type command.

The IS 2:0 bits are duplicated from the IS 2:0 field in the Internal State Register (ISREG) in the normal mode. If the device is in the test mode, IS 0 is set to indicate that the offset value is non zero. A non zero value indicates

that synchronous data transfer can continue. A zero value indicates that the synchronous offset count has been reached and no more data can be transferred until an acknowledge is received.

#### CFISREG - Bits 4:0 - CF 4:0 - Current FIFO 4:0

The CF 4:0 bits are the binary coded value of the number of bytes in the FIFO. These bits should not be read when the device is transferring data since this count may not be stable.

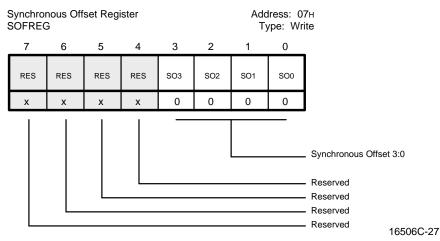

### Synchronous Offset Register (07H) Write

The Synchronous Offset Register (SOFREG) contains a 4-bit count of the number of bytes that can be sent to (or received from) the SCSI bus without an  $\overline{ACK}$  (or  $\overline{REQ}$ ). Bytes exceeding the threshold will be sent one byte at a time (asynchronously). That is, each byte will require an  $\overline{ACK/REQ}$  handshake. To set up an asynchronous transfer, the SOFREG is set to zero. The SOFREG is set to zero after a hard or soft reset.

### SOFREG - Bits 7:4 - RES - Reserved

## SOFREG – Bits 3:0 – SO 3:0 – Synchronous Offset 3:0

The SO 4:0 bits are the binary coded value of the number of bytes that can be sent to (or received from) the SCSI bus without an ACK (or REQ) signal.

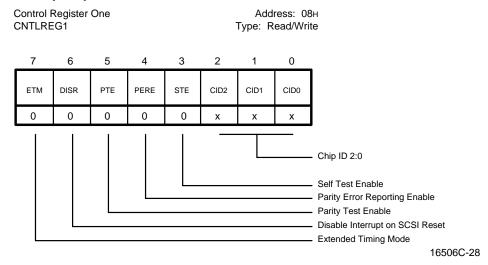

### Control Register One (08H) Read/Write

The Control Register 1 (CNTLREG1) sets up the device with various operating parameters.

### CNTLREG1 - Bit 7 - ETM - Extended Timing Mode

The ETM bit is set if an extra clock period is required between the data being driven on the bus and the REQ or ACK being asserted. This is some times necessary in high capacitive loading environments. The ETM bit is reset to zero by a hard or soft reset.

## CNTLREG1 – Bit 6 – DISR – Disable Interrupt on SCSI Reset

The DISR bit masks the reporting of the SCSI reset. When the DISR bit is set and a SCSI reset is asserted, the device will disconnect from the SCSI bus and remain idle without interrupting the host processor. When the DISR bit is reset and a SCSI reset is asserted the device will respond by interrupting the host processor. The DISR bit is reset to zero by a hard or soft reset.

### CNTLREG1 - Bit 5 - PTE - Parity Test Enable

The PTE bit is for test use only. When the PTE bit is set the parity on the output (SCSI or host processor) bus is forced to the value of the MSB (bit 7) of the output data from the internal FIFO. This allows parity errors to be created to test the hardware and software. The PTE bit is reset to zero by a hard or soft reset.

## **CNTLREG1 – Bit 4 – PERE – Parity Error Reporting Enable**

The PERE bit enables the checking and reporting of parity errors on incoming SCSI bytes during the information transfer phase. When the PERE bit set and a bad parity is detected, the PE bit in the STATREG is will be set but an interrupt will not be generated. In the initiator mode the ATN signal will also be asserted on the SCSI bus. When the PERE bit is reset and a bad parity occurs it is not detected and no action is taken.

### CNTLREG1 - Bit 3 - STE - Self Test Enable

The STE bit is for test use only. When the STE bit is set the device is placed in a test mode which enables the device to access the test register at address 0AH. To reset this bit and to resume normal operation the device must be issued a hard or soft reset.

### CNTLREG1 - Bit 2:0 - CID 2:0 - Chip ID 2:0

The Chip ID 2:0 bits specify the binary coded value of the device ID on the SCSI bus. The device will arbitrate with this ID and will respond to selection or reselection to this ID. At power-up the state of these bit are undefined. These bits are not affected by hard or soft reset.

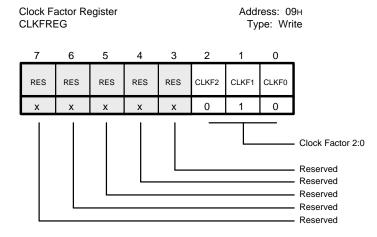

### Clock Factor Register (09H) Write

16506C-29

The Clock Factor Register (CLKFREG) must be set to indicate the input frequency range of the device. This value is crucial for controlling various timings to meet the SCSI specification. The selector can be calculated by rounding off the quotient of (Input Clock Frequency in MHz)/(5 MHz). The device has a frequency range of 10 to 25 MHz.

CLKFREG - Bits 7:3 - RES - Reserved

#### CLKFREG - Bits 2:0 - CLKF 2:0 - Clock Factor 2:0

The CLKF 2:0 bits specify the binary coded value of the clock factor. The CLKF 2:0 bits will default to a value of 2 by a hard or soft reset.

| CLKF2 | CLKF1 | CLKF0 | Input Clock<br>Frequency in MHz |

|-------|-------|-------|---------------------------------|

| 0     | 1     | 0     | 10                              |

| 0     | 1     | 1     | 10.01 to 15                     |

| 1     | 0     | 0     | 15.01 to 20                     |

| 1     | 0     | 1     | 20.01 to 25                     |

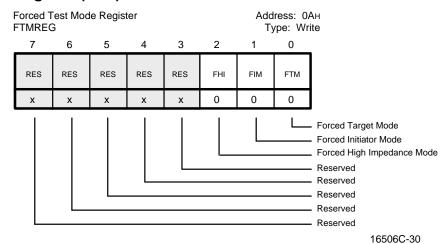

### Forced Test Mode Register (0AH) Write

The Forced Test Mode Register (FTMREG) is for test use only. The STE bit in the CNTLREG1 must be set for the FTMREG to operate.

FTMREG - Bits 7:3 - RES - Reserved

### FTMREG – Bit 2 – FHI – Forced High Impedance Mode

The FHI bit when set places all the output and bidirectional pins into a high impedance state.

### FTMREG - Bit 1 - FIM - Forced Initiator Mode

The FIM bit when set forces the device into the initiator mode. The device will then execute all initiator commands irrespective of the SCSI bus status.

### FTMREG - Bit 0 - FTM - Forced Target Mode

The FTM bit when set forces the device into the target mode. The device will then execute all target commands irrespective of the SCSI bus status.

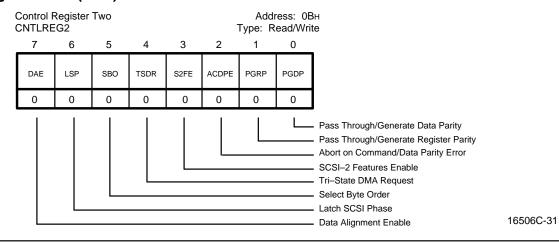

### Control Register Two (0BH) Read/Write

The Control Register 2 (CNTLREG2) sets up the device with various operating parameters.

### CNTLREG2 - Bit 7 - DAE - Data Alignment Enable

The DAE bit is used in the initiator Synchronous Data-In phase only. When the DAE bit is set one byte is reserved at the end of the FIFO when the phase changes to the Synchronous Data-In phase. The contents of this byte will become the lower byte of the DMA word (16-bit) transfer to the memory, the upper byte being the first byte of the first word received from the SCSI bus.

### Note:

If an interrupt is received for a misaligned boundary on a phase change to synchronous data the following recovery procedure may be followed. The host processor should copy the byte at the start address in the host memory to the Data Alignment Register 0FH (DALREG) and then issue an information transfer command. The first word the device will write to the memory (via DMA) will consists of the lower byte from the DALREG and the upper byte from the first byte received from the SCSI bus.

The DAE bit must be set before the phase changes to the Synchronous Data-In. The DAE bit is reset to zero by a hard or soft reset or by writing the DALREG when interrupted in the Synchronous Data-In phase.

#### CNTLREG2 - Bit 6 - LSP - Latch SCSI Phase

The LSP bit is used to enable or disable the latching of the SCSI phase bits (MSG, C/D and I/O) in the Status Register (STATREG) 04H.

When the LSP bit is set the phase bits STSTREG – Bits 2:0 are latched at the end of each command. This simplifies software for stacked commands. When the LSP bit is reset the phase bits STATREG – Bits 2:0 reflect the

actual state of the SCSI phase lines at any instant of time. The LSP bit is reset by a hard or soft reset.

### CNTLREG2 - Bit 5 - SBO - Select Byte Order

The SBO bit is used only when the BUSMD 1:0 = 10 to enable or disable the byte control on the DMA interface. When SBO is set and the BUSMD 1:0 = 10, the byte control inputs BHE and AS0 control the byte positions. When SBO is reset the byte control inputs BHE and AS0 are ignored.

## CNTLREG2 – Bit 4 – TSDR – Tri-State DMA Request

The TSDR bit when set sends the DREQ output signal to high impedance state and the device ignores all activity on the DMA request (DREQ) input. This is useful for wiring-OR several devices that share a common DMA request line. When the TSDR bit is reset the DREQ output is driven to TTL levels.

### CNTLREG2 – Bit 3 – S2FE – SCSI–2 Features Enable

The S2FE bit allows the device to recognize two SCSI-2 features. The two features are extended message feature and the Group 2 command recognition.

Extended Message Feature: When the S2FE bit is set and the device is selected with attention, the device will monitor the  $\overline{\text{ATN}}$  signal at the end of the first message byte. If the  $\overline{\text{ATN}}$  signal is active, the device will request two more message bytes before switching to the command phase. If the  $\overline{\text{ATN}}$  signal is inactive the device will switch to the command phase. When the S2FE bit is reset the device as a target will request a single message byte. As an initiator, the device will abort the selection sequence if the target does not switch to the command phase after receiving a single message byte.

Group 2 Command Recognition: When the S2FE bit is set the group 2 commands are recognized as 10 byte commands. The GCV (Group Code Valid) bit in the STATREG (04H) is set. When the S2FE bit is reset, the device will interpret the group 2 commands as reserved commands and will request 6 byte commands. The GCV bit in the STATREG will not be set in this case.

### CNTLREG2 – Bit 2 – ACDPE – Abort on Command/ Data Parity Error

The ACDPE bit when set allows the device to abort a command or data transfer when a parity error is detected. When the ACDPE bit is reset parity error is ignored.

## CNTLREG2 – Bit 1 – PGRP – Pass Through/Generate Register Parity

The PGRP bit when set causes the data along with the parity from the host to pass through to the FIFO under the control of the  $\overline{\text{CS}}$  and the  $\overline{\text{WR}}$  signals. When the

PGRP bit is reset, the device generates the parity on the data from the host before writing it to the FIFO.

When the device is placing the data on the SCSI bus, it will check for an outgoing parity error if either the PGRP bit is set or the PGDP (Pass Through/Generate Data Parity) bit is set.

## CNTLREG2 – Bit 0 – PGDP – Pass Through/Generate Data Parity

The PGDP bit when set causes the data along with the parity from the host to pass through to the FIFO under the control of the  $\overline{DACK}$  and the  $\overline{WR}$  signals. When the PGDP bit is reset, the device generates the parity on the data from the host before writing it to the FIFO.

When the device is placing the data on the SCSI bus, it will check for an outgoing parity error if either the PGDP bit is set or the PGRP (Pass Through/Generate Register Parity) bit is set.

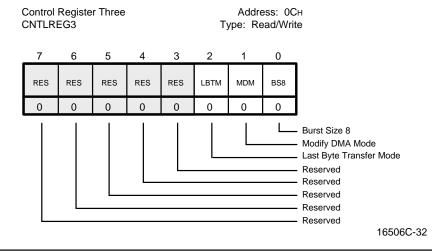

### Control Register Three (0CH) Read/Write

### CNTLREG3 - Bits 7:3 - RES - Reserved

### CNTLREG3 – Bit 2 – LBTM – Last Byte Transfer Mode

The LBTM bit specifies how the last byte in an odd byte transfer is handled during 16-bit DMA transfers. This mode is not used if byte control is selected via BUSMD 1:0 inputs and BSO (Byte Select Order) bit in the CNTLREG2. This mode has no affect during 8-bit DMA transfers and on transfers on the SCSI bus.

When the LBTM bit is set the DREQ signal will not be asserted for the last byte, instead the host will read or write the last byte from or to the FIFO. When the LBTM bit is reset the DREQ signal will be asserted for the last byte and the following 16-bit DMA transfer will contain the last byte on the lower bus. If the transfer is a DMA read the upper bus will be all ones.

The LBTM bit is reset by hard or soft reset.

### CNTLREG3 - Bit 1 - MDM - Modify DMA Mode

The MDM bit is used to modify the timing of the DACK signal with respect to the DMARD and DMAWR signals. The MDM bit is used in conjunction with the Burst Size 8 (BS8) bit in the CNTLREG3. Both bits have to be set for proper operation.

When the MDM bit is set and the device is in a DMA read or write mode the DACK signal will remain asserted while the data is strobed by the DMARD or DMAWR signals. In the DMA read mode when BUSMD 1:0 = 11 the DACK signal will toggle for every DMA read.

When the MDM bit is reset and the device is in a DMA read or write mode the DACK signal will toggle every time the data is strobed by the DMARD or DMAWR signals.

### CNTLREG3 - Bit 0 - BS8 - Burst Size 8

The BS8 bit is used to modify the timing of the DREQ signal with respect to the DMARD and DMAWR signals. The BS8 bit is used in conjunction with the Modify DMA Mode (MDM) bit in the CNTLREG3. Both bits have to be set for proper operation.

When the BS8 bit is set the device delays the assertion of the DREQ signal until 8 bytes or 4 words transfer is possible.

When the BS8 bit is set and the device is in a DMA write mode the DREQ signal will be asserted only when 8 byte locations are available for writing. In the DMA read mode the DREQ signal will go active under the following circumstances:

At the end of a transfer,

- In the target mode,

- when the transfer is complete

or

- when the ATN signal is active

- In the initiator mode.

- when the Current Transfer Register is decremented to zero

or

- after any phase change

In the middle of a transfer

- In the initiator mode,

- when the last 8 bytes of the FIFO are full

- during Synchronous Data-In transfer when the Event Transfer Count Register is greater than 7 and the last 8 bytes of the FIFO are full.