## **DSP56F800**

**User Manual**

56F800 16-bit Digital Signal Controllers

DSP56F801-7UM Rev. 8 03/2007

freescale.com

This manual is one of a set of three documents. You need the following manuals to have complete product information: Family Manual, User's Manual, and Technical Data Sheet.

Note:

With the exception of errata documents, if any other Freescale document contains information that conflicts with the information in the device data sheet, the data sheet should be considered to have the most current and correct data.

Order this document by **DSP56F801-7UM/D - Rev. 8**March 2007

#### **Summary of Changes and Updates:**

Added "List of Figures" and "List of Tables" sections after the Table of Contents.

See the "Document Revision History" section of each chapter for chapter-specific changes.

### TABLE OF CONTENTS

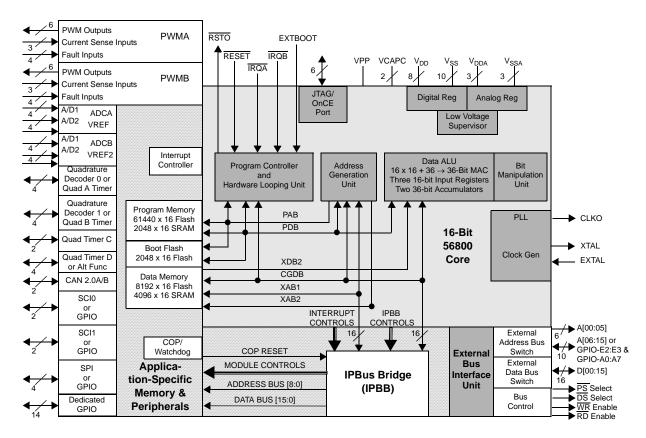

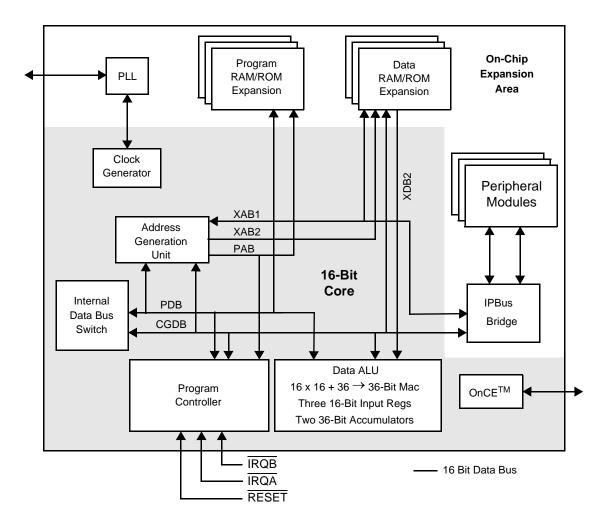

# Chapter 1 56F800 Family

| 1.1              | Introduction                                 | 1-1           |

|------------------|----------------------------------------------|---------------|

| 1.2              | DSP56800 Family Description                  | 1-4           |

| 1.3              | Manual Organization                          | 1-5           |

| 1.4              | Additional information:                      | 1-7           |

| 1.5              | Manual Conventions                           | 1-7           |

| 1.6              | Architectural Overview                       | 1-9           |

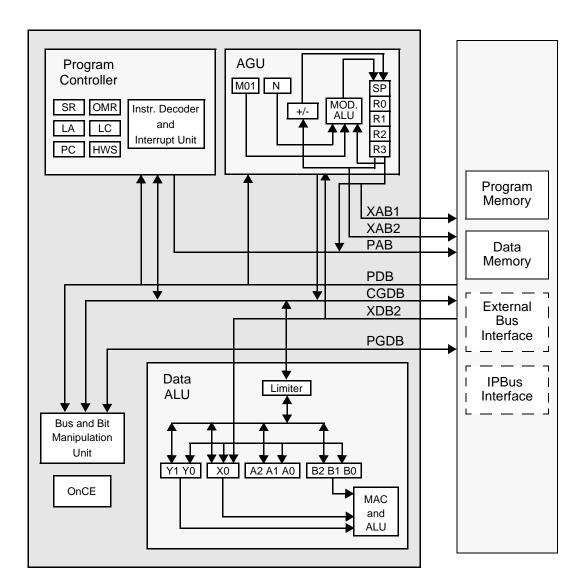

| 1.7              | DSP56800 Core Description                    | l-15          |

| 1.7.1            | 56800 Core Block Diagram                     | l-15          |

| 1.7.2            | Data Arithmetic Logic Unit (Data ALU)        | l-18          |

| 1.7.3            | Address Generation Unit (AGU)                | l <b>-</b> 18 |

| 1.7.4            | Program Controller and Hardware Looping Unit | I <b>-1</b> 9 |

| 1.7.5            | Bit Manipulation Unit                        |               |

| 1.7.6            | Address and Data Buses                       |               |

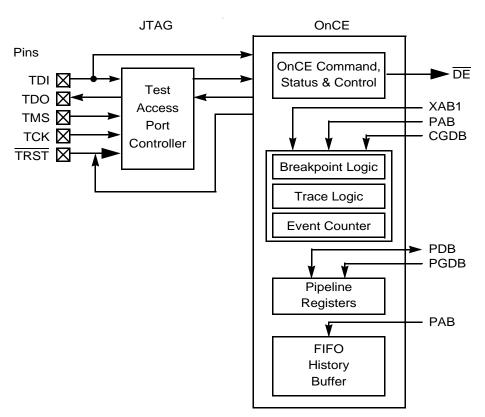

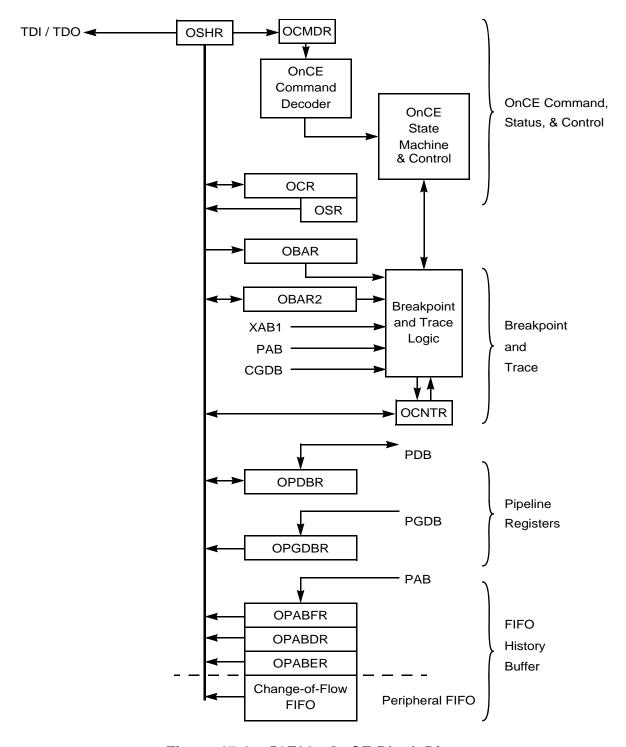

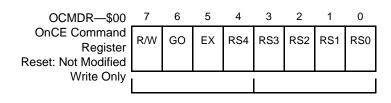

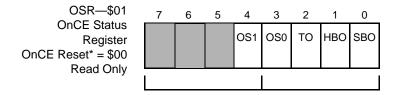

| 1.7.7            | On-Chip Emulation (OnCE) Module              |               |

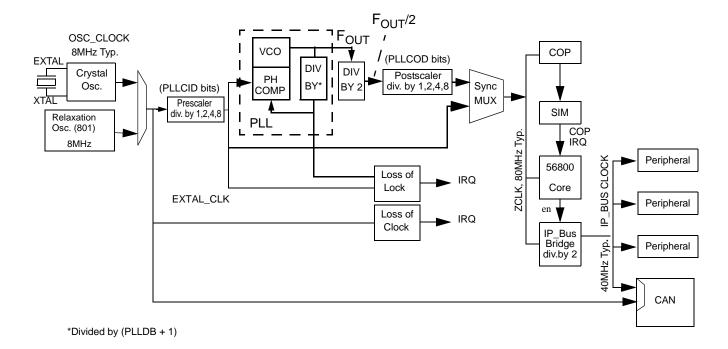

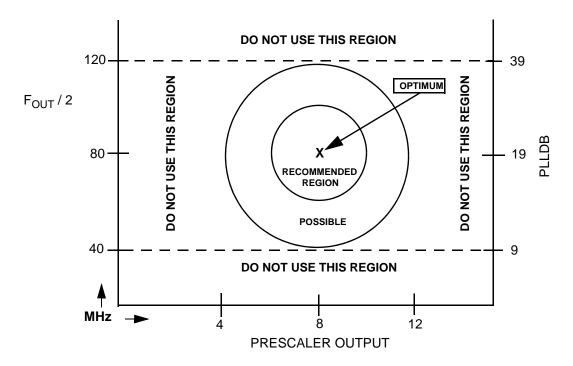

| 1.7.8            | On-Chip Clock Synthesis Block                |               |

| 1.7.9            | Oscillators                                  |               |

| 1.7.10           |                                              |               |

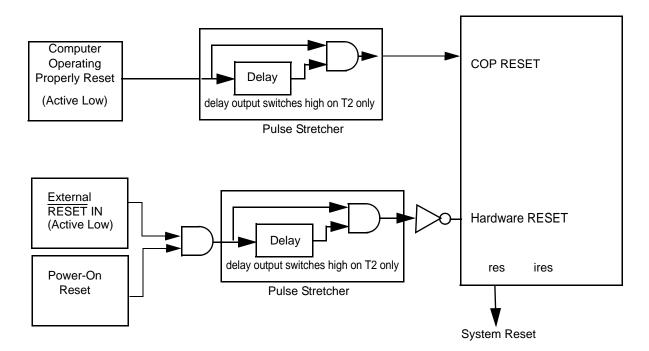

| 1.7.11<br>1.7.12 | Resets                                       |               |

| 1.7.12           |                                              |               |

| 1.7.13           |                                              |               |

| 1.8.1            | Memory Modules                               |               |

| 1.8.2            | Program Flash                                |               |

| 1.8.3            | Data Flash                                   |               |

| 1.8.4            | Data RAM                                     |               |

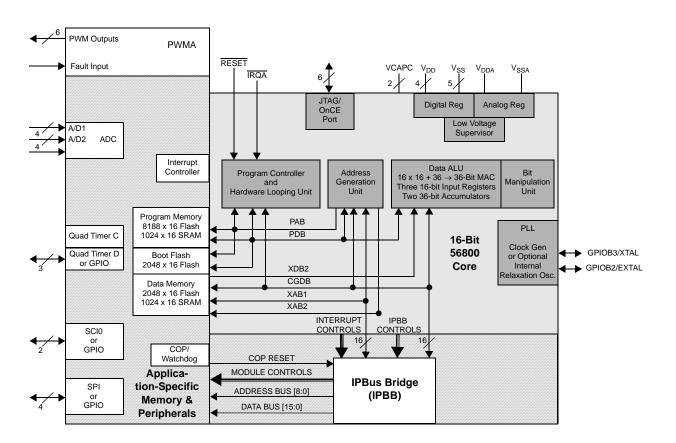

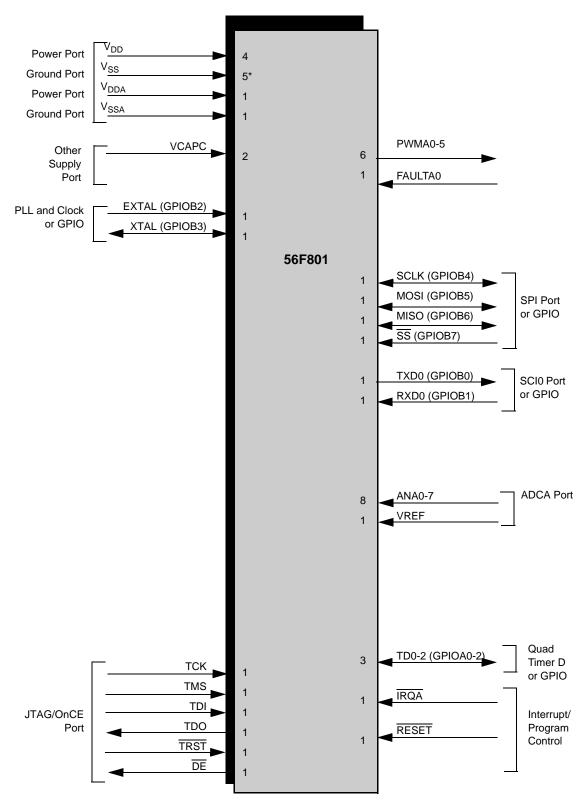

| 1.9              | 56F801 Peripheral Blocks                     |               |

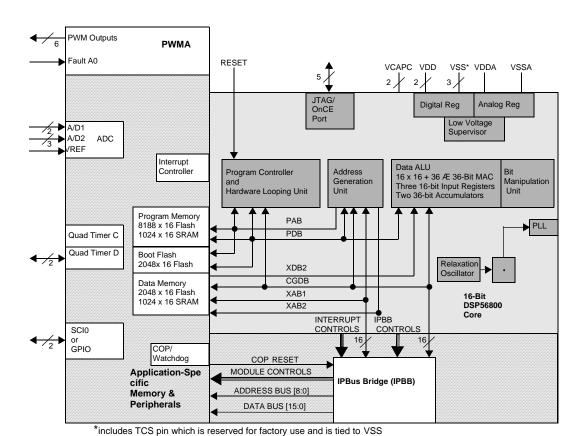

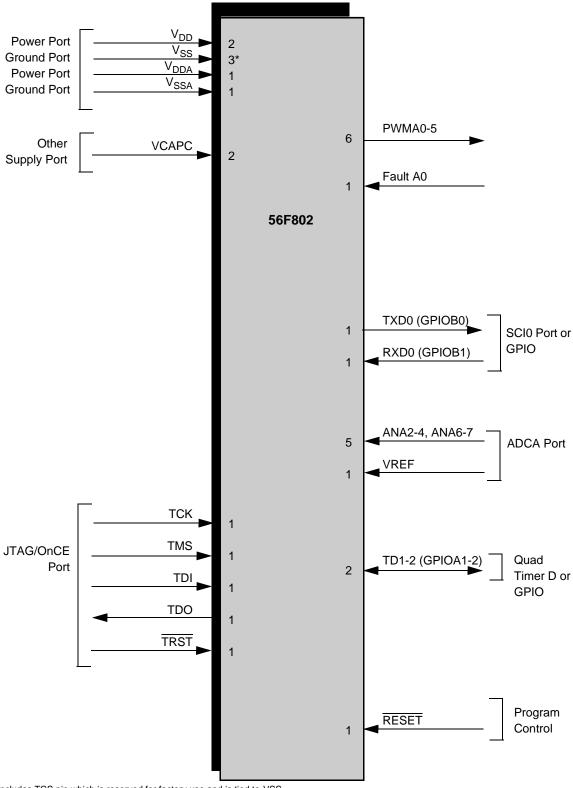

| 1.10             | 56F802 Peripheral Blocks                     |               |

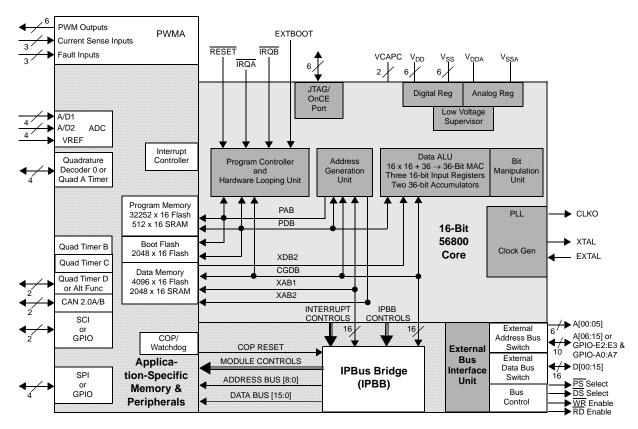

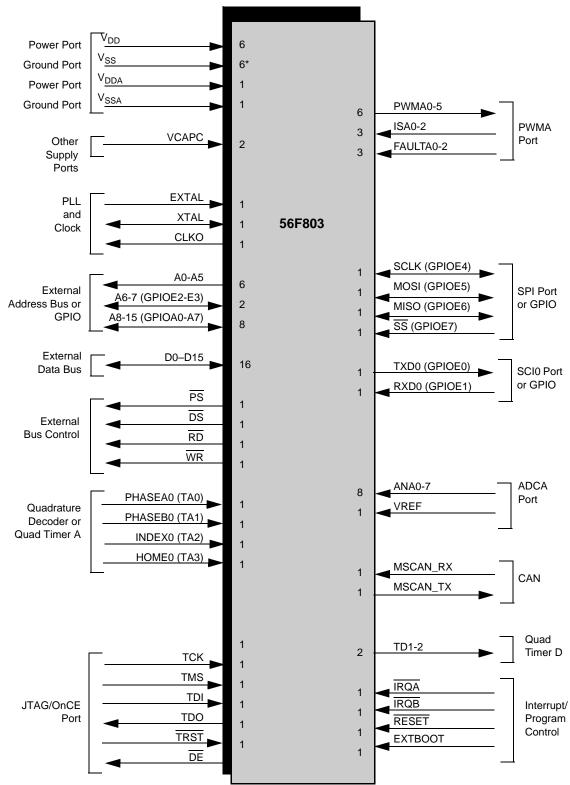

| 1.11             | 56F803 Peripheral Blocks                     |               |

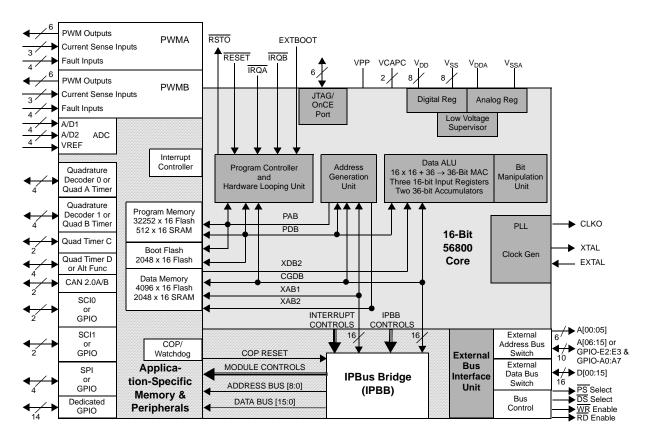

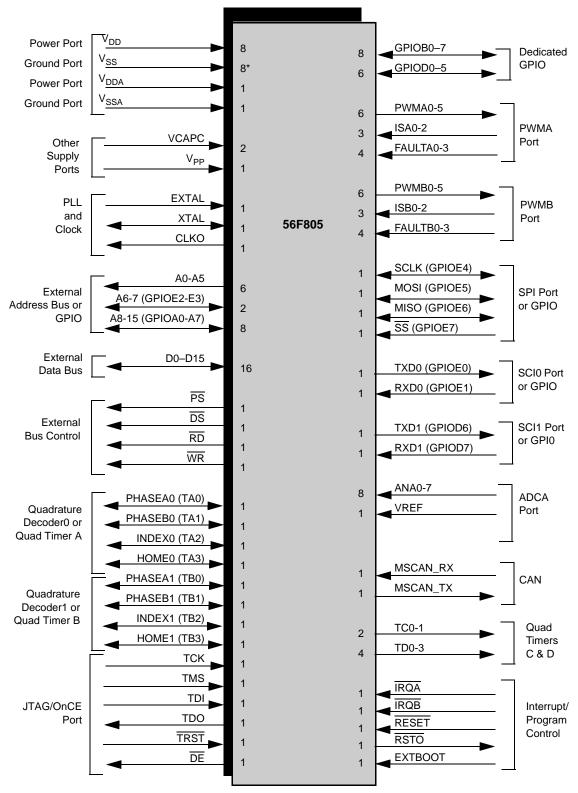

| 1.12             | 56F805 Peripheral Blocks                     |               |

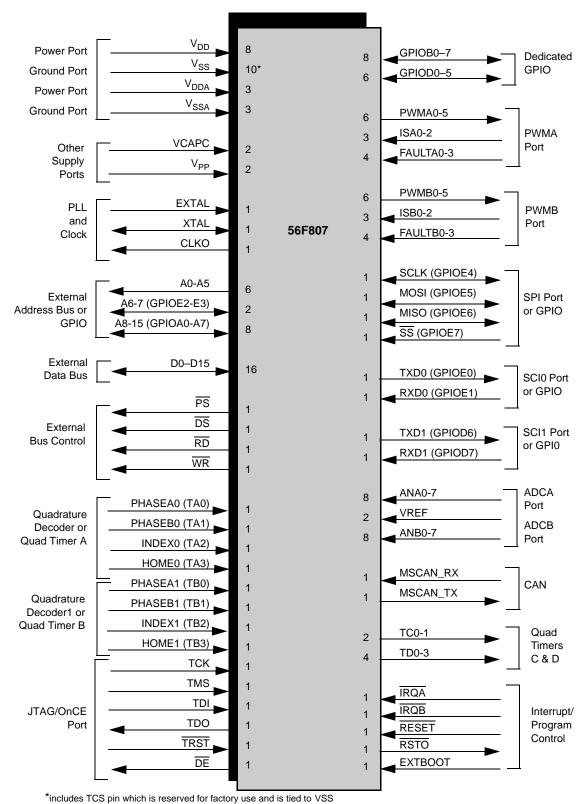

| 1.13             | 56F807 Peripheral Blocks                     |               |

| 1.14             | Peripheral Descriptions                      |               |

| 1.14.1           | External Memory Interface (EMI)              |               |

| 1.14.2           |                                              |               |

| 1.14.3           |                                              |               |

| 1.14.4           |                                              |               |

| 1.14.5           | · · · · · · · · · · · · · · · · · · ·        |               |

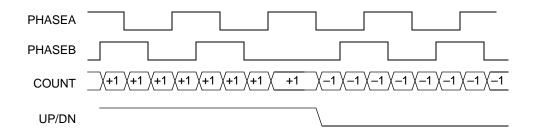

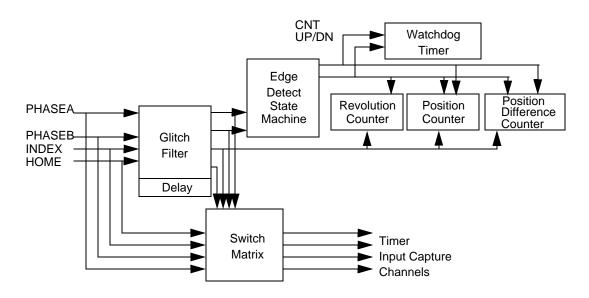

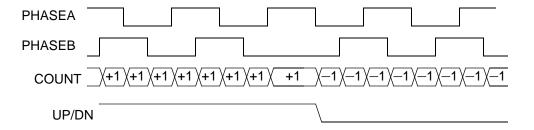

| 1.14.6                            | Quadrature Decoder                                                                                                                                                            | 1-31                  |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| 1.14.7                            | Quad Timer Module                                                                                                                                                             | 1-31                  |

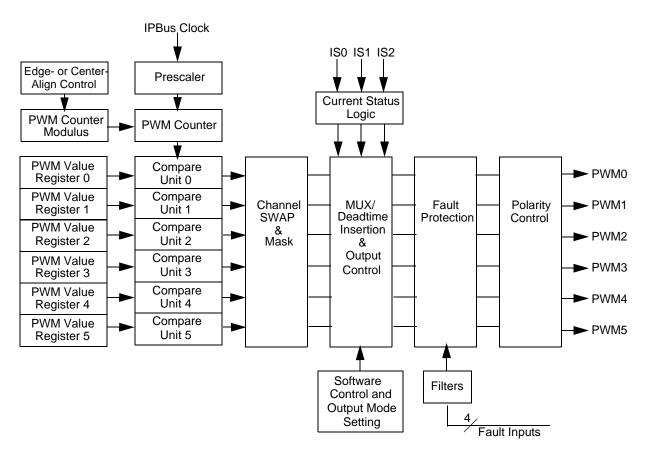

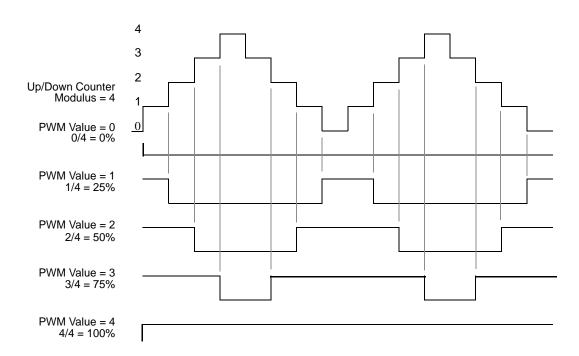

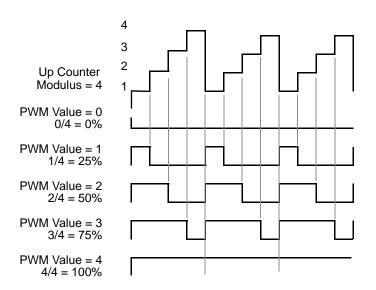

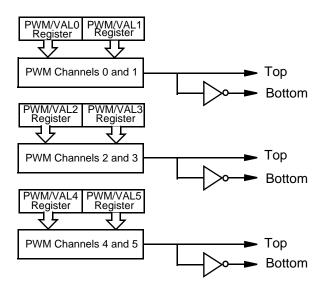

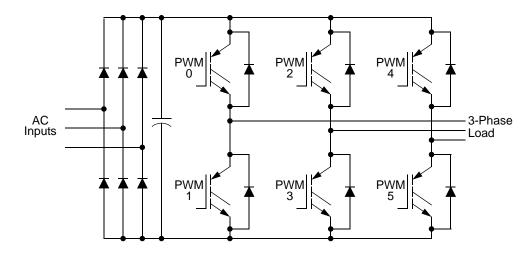

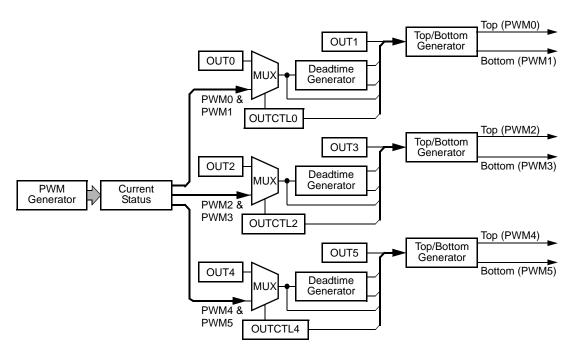

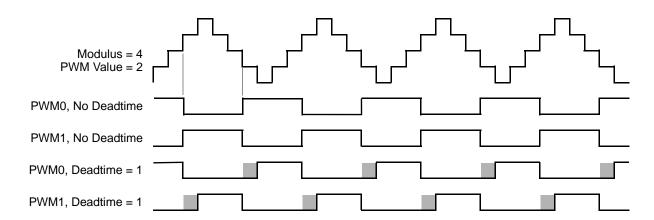

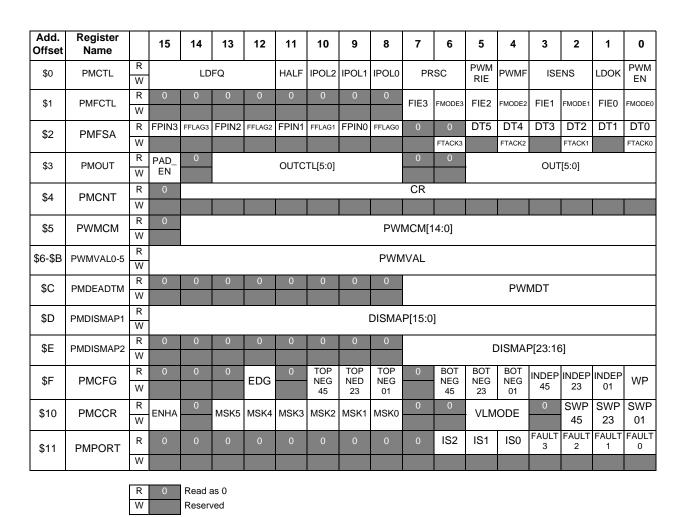

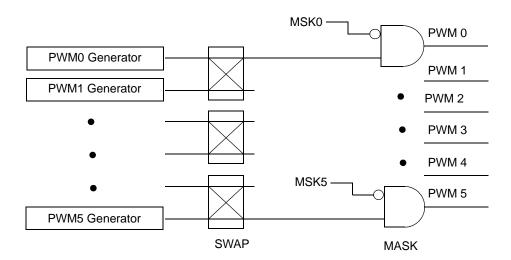

| 1.14.8                            | Pulse Width Modulator (PWM) Module                                                                                                                                            | 1-32                  |

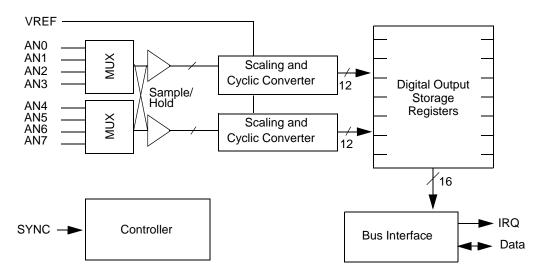

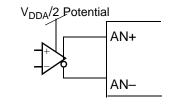

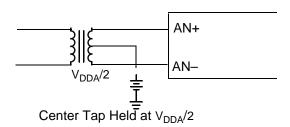

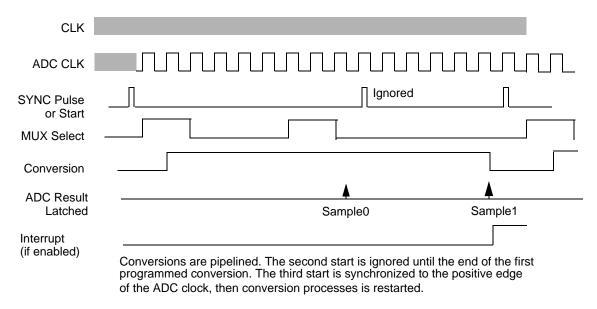

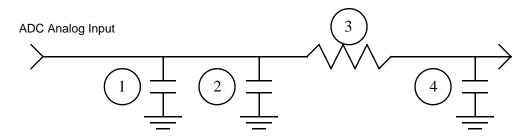

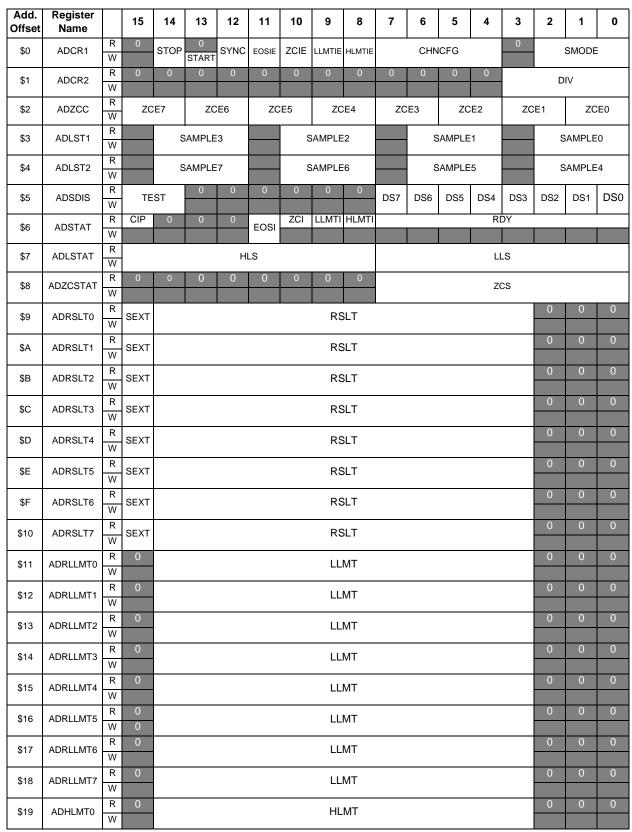

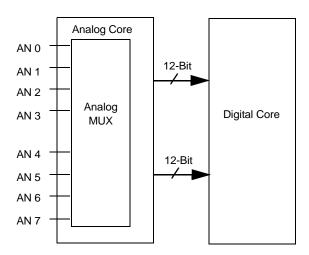

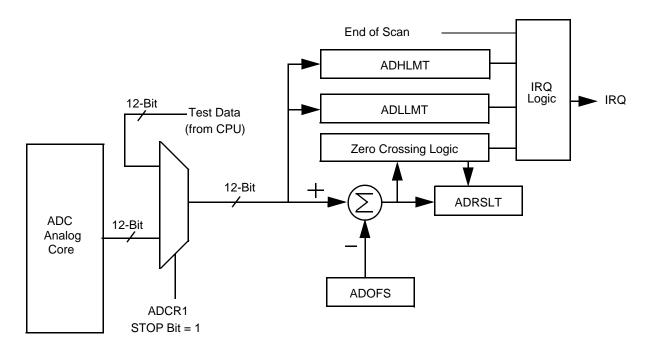

| 1.14.9                            | Analog-to-Digital Conversion (ADC)                                                                                                                                            | 1-33                  |

| 1.14.10                           | ADC and PWM Synchronization Feature                                                                                                                                           | 1-33                  |

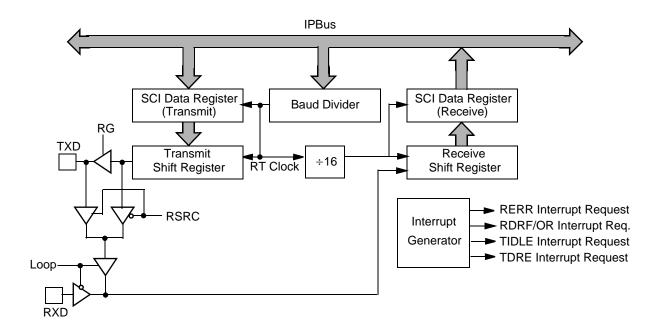

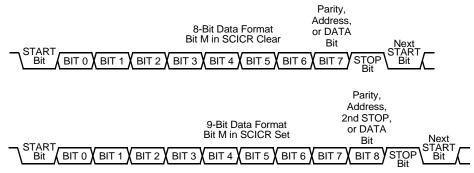

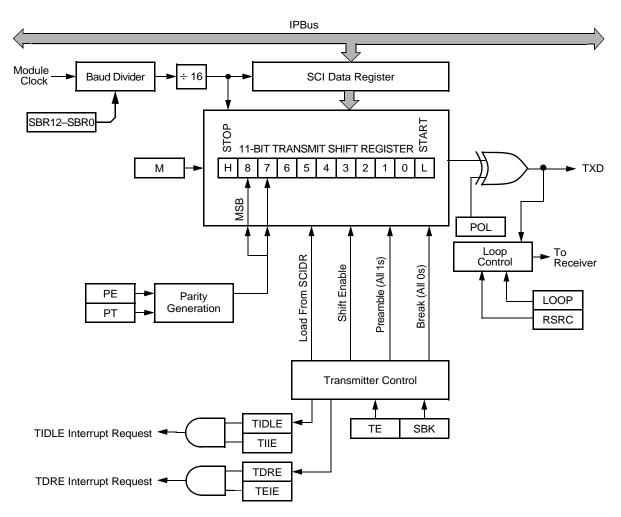

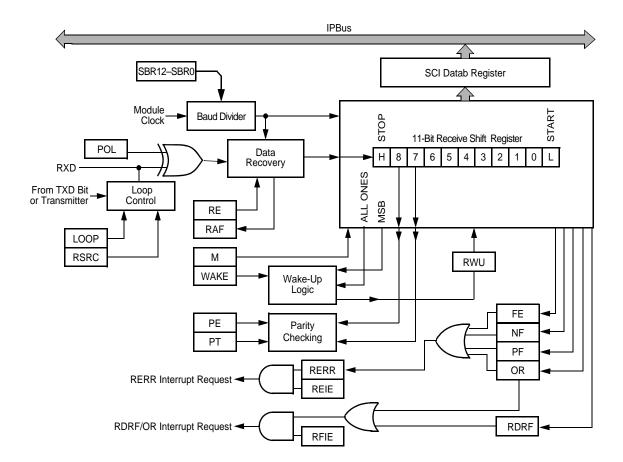

| 1.14.11                           | Serial Communications Interface (SCI)                                                                                                                                         | 1-34                  |

| 1.14.12                           | Controller Area Network (CAN) Module                                                                                                                                          | 1-34                  |

| 1.14.13                           | Peripheral Interrupts                                                                                                                                                         | 1-34                  |

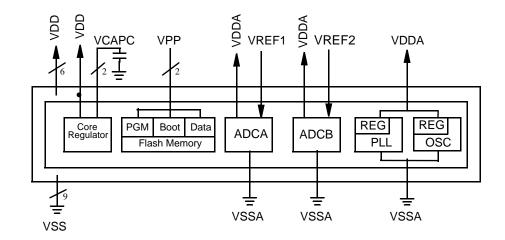

| 2.1 II<br>2.2 F<br>2.3 C<br>2.4 A | ter 2 escriptions  Introduction.  Power and Ground Signals.  Clock and Phase Lock Loop Signals  Address, Data, and Bus Control Signals Interrupt and Program Control Signals. | . 2-7<br>2-11<br>2-12 |

| 2.6                               | SPIO Signals                                                                                                                                                                  | 2-14                  |

|                                   | Pulse Width Modulator (PWM) Signals                                                                                                                                           |                       |

| 2.8                               | Serial Peripheral Interface (SPI) Signals                                                                                                                                     | 2-16                  |

|                                   | Quadrature Decoder Signals                                                                                                                                                    |                       |

|                                   | Serial Communications Interface (SCI) Signals                                                                                                                                 |                       |

|                                   | CAN Signals                                                                                                                                                                   |                       |

|                                   | nalog-to-Digital Converter (ADC) Signals                                                                                                                                      |                       |

|                                   | Quad Timer Module Signals                                                                                                                                                     |                       |

|                                   | TAG/OnCE                                                                                                                                                                      |                       |

|                                   | ory and Operating Modes                                                                                                                                                       | 2.1                   |

|                                   | Nemory Map                                                                                                                                                                    |                       |

|                                   |                                                                                                                                                                               |                       |

|                                   | Data Memory                                                                                                                                                                   |                       |

| 3.3.1<br>3.3.1.1                  | Bus Control Register (BCR)                                                                                                                                                    |                       |

| 3.3.1.2                           | Reserved—Bits 15–10                                                                                                                                                           |                       |

| 3.3.1.2                           | Reserved—Bit 8                                                                                                                                                                |                       |

| 3.3.1.4                           | Wait State Data Memory (WSX[3:0])—Bits 7–4                                                                                                                                    |                       |

| 3.3.1.5                           | Wait State P Memory (WSP[3:0])—Bits 3–0                                                                                                                                       |                       |

| 3.3.2                             | Operating Mode Register (OMR)                                                                                                                                                 |                       |

| 3.3.2.1                           | Nested Looping (NL)—Bit 15                                                                                                                                                    |                       |

| 3.3.2.2                           | Reserved—Bits 14–9                                                                                                                                                            |                       |

| 5.5.2.2                           |                                                                                                                                                                               |                       |

DSP56F800 Family User's Manual, Rev. 8

Table of Contents - ii

Freescale Semiconductor

| 3.3.2.3 | Condition Codes (CC)—Bit 8                     |

|---------|------------------------------------------------|

| 3.3.2.4 | 4 Reserved—Bit 7                               |

| 3.3.2.  | 5 Stop Delay (SD)—Bit 6                        |

| 3.3.2.6 | 6 Rounding (R)—Bit 5                           |

| 3.3.2.7 | 7 Saturation (SA)—Bit 4                        |

| 3.3.2.8 |                                                |

| 3.3.2.9 |                                                |

| 3.3.2.  |                                                |

| 3.3.2.  | Operating Mode A (MA)—Bit 0                    |

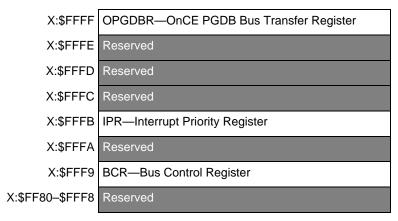

| 3.4     | Core Configuration Memory Map                  |

| 3.5     | On-Chip Peripheral Memory Map                  |

| 3.6     | Program Memory                                 |

| 3.7     | 56800 Operating Modes                          |

| 3.7.1   | Mode 0-Single Chip Mode: Start-Up              |

| 3.7.2   | Modes 1 and 2                                  |

| 3.7.3   | Mode 3–External                                |

| 3.8     | Boot Flash Operation                           |

| 3.9     | Executing Programs from XRAM                   |

| 3.10    | 56800 Reset and Interrupt Vectors              |

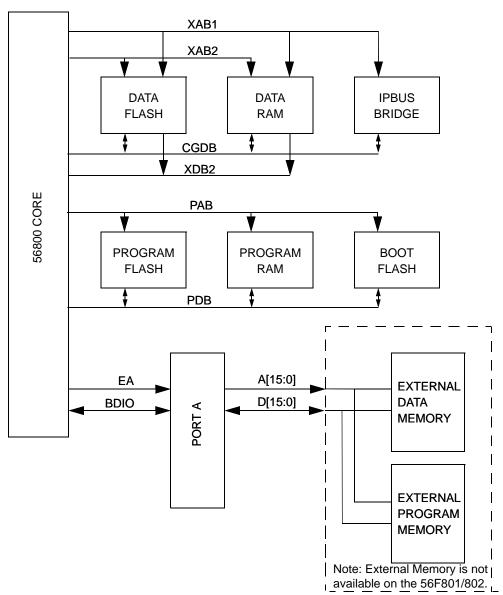

| 3.11    | Memory Architecture                            |

| Cha     | pter 4                                         |

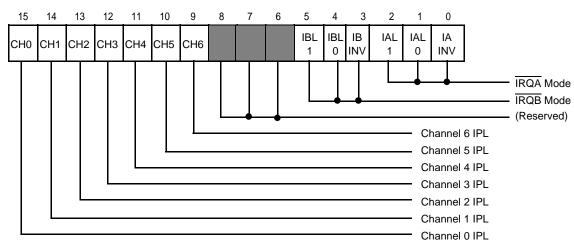

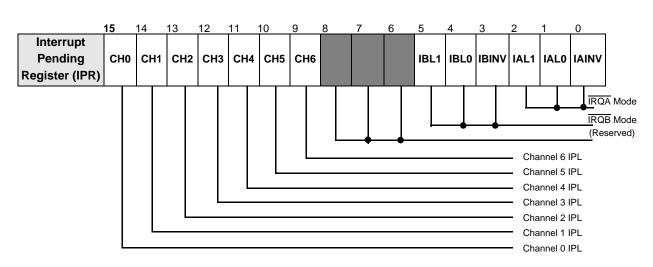

|         | rupt Controller (ITCN)                         |

| 4.1     | Introduction                                   |

| 4.2     | Interrupt Source                               |

| 4.3     | Interrupt Control                              |

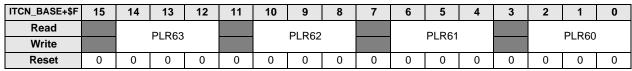

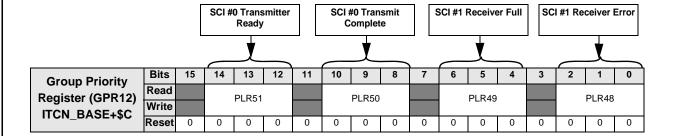

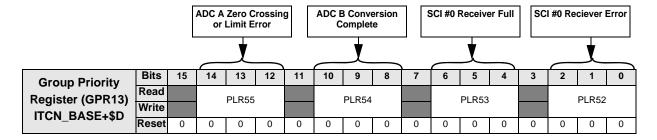

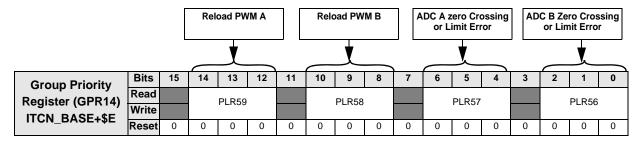

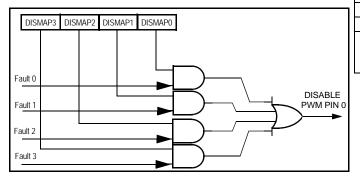

| 4.4     | Priority Level Register (PLR)                  |

| 4.5     | Interrupt Exceptions                           |

| 4.6     | Interrupt Enable                               |

| 4.7     | Interrupt Priority Register (IPR)              |

| 4.8     | ITCN Register Summary                          |

| 4.9     | Priority Level and Vector Assignments4-4       |

| 4.10    | Register Definitions                           |

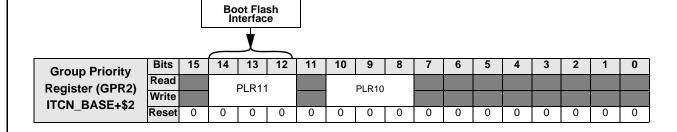

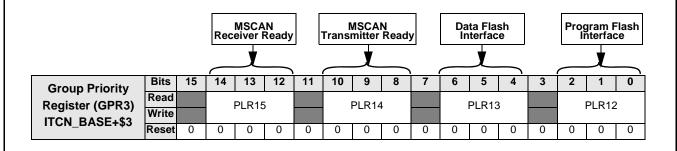

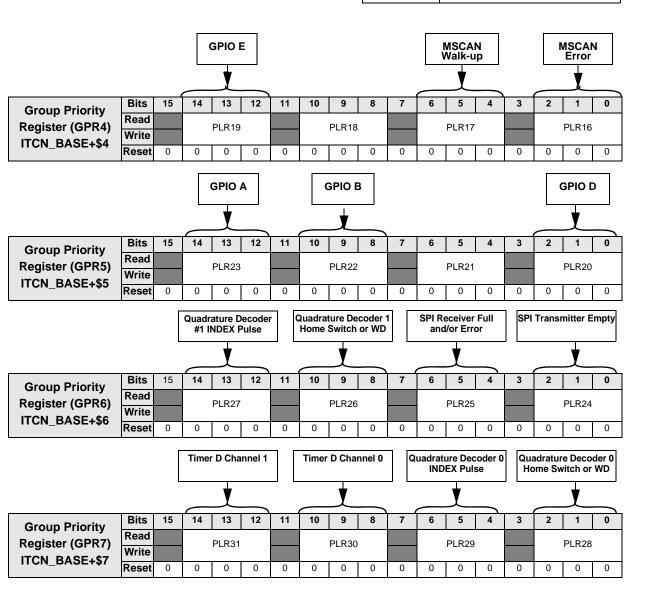

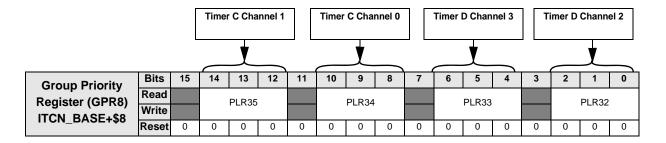

|         | Group Priority Registers 2–15 (GPR2–GPR15) 4-8 |

|         |                                                |

Freescale Semiconductor Table of Contents - iii

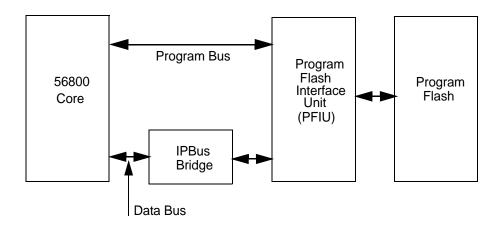

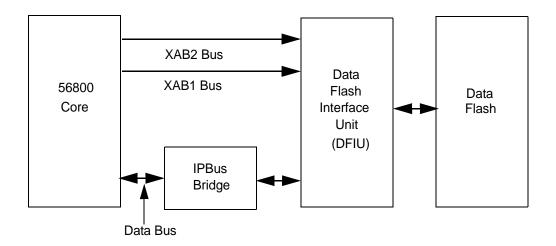

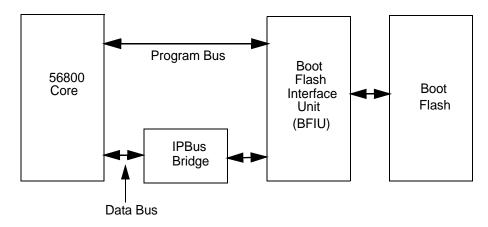

# **Chapter 5 Flash Memory Interface**

| 5.1                | Introduction5-1                                    |

|--------------------|----------------------------------------------------|

| 5.2                | Features                                           |

| 5.3                | Flash Description                                  |

| 5.4                | Program Flash (PFLASH)                             |

|                    | Data Flash (DFLASH)                                |

|                    | Boot Flash (BFLASH)                                |

|                    | Program/Data/Boot Flash Interface Unit Features    |

|                    | Program/Data/Boot Flash Modes                      |

|                    | Functional Description of the PFIU, DFIU, and BFIU |

|                    | Flash Programming and Erase Models                 |

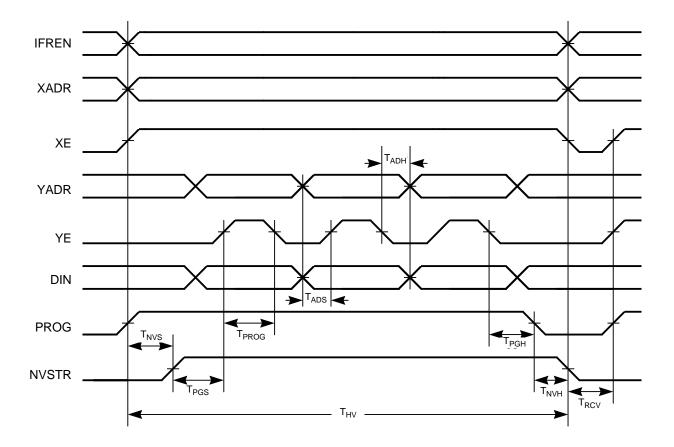

| 5.10.1             | Intelligent Word Programming                       |

| 5.10.1             | Dumb Word Programming                              |

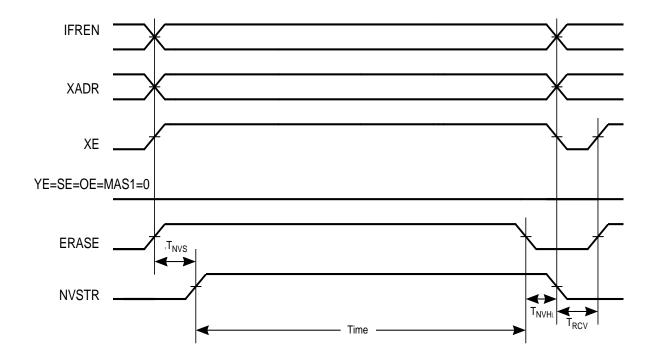

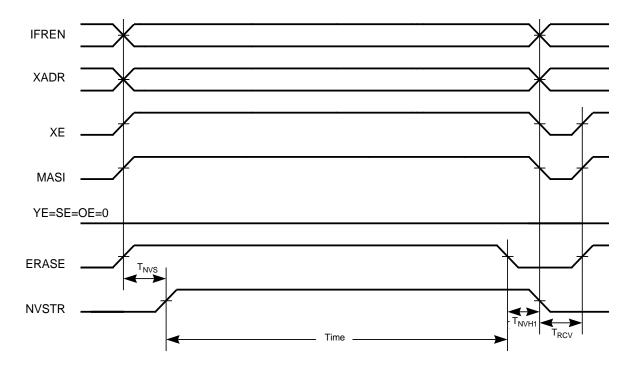

| 5.10.2             | Intelligent Erase Operation                        |

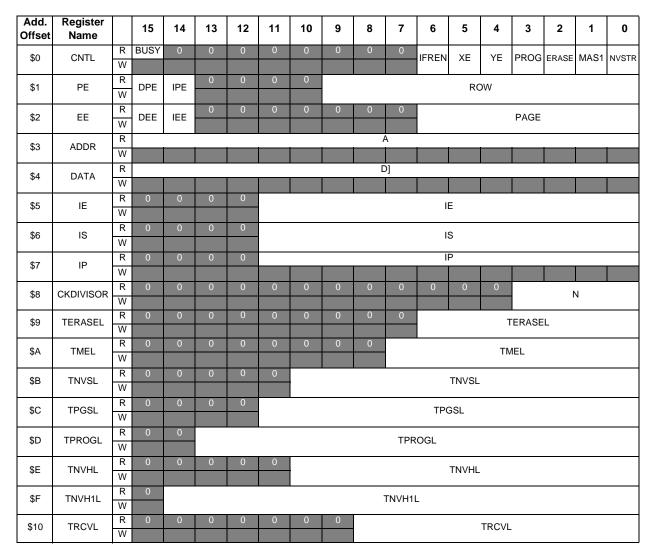

|                    | Register Definitions                               |

| 5.11.1             | Flash Control Register (FIU_CNTL)                  |

| 5.11.1<br>5.11.1.  |                                                    |

| 5.11.1.<br>5.11.1. |                                                    |

| 5.11.1.<br>5.11.1. |                                                    |

| 5.11.1.<br>5.11.1. | $\cdot$                                            |

| 5.11.1.<br>5.11.1. |                                                    |

| 5.11.1.            |                                                    |

| 5.11.1.            |                                                    |

| 5.11.1.            |                                                    |

| 5.11.1.            |                                                    |

| 5.11.2             | Flash Program Enable Register (FIU_PE)             |

| 5.11.2.            |                                                    |

| 5.11.2.            | 2 Intelligent Program Enable (IPE)—Bit 14 5-20     |

| 5.11.2.            | 3 Reserved—Bits 13–105-20                          |

| 5.11.2.            | 4 Row Number (ROW)—Bits 9–05-20                    |

| 5.11.3             | Flash Erase Enable Register (FIU_EE)5-21           |

| 5.11.3.            | 1 Dumb Erase Enable (DEE)—Bit 155-21               |

| 5.11.3.            |                                                    |

| 5.11.3.            |                                                    |

| 5.11.3.            |                                                    |

| 5.11.4             | Flash Address Register (FIU_ADDR)                  |

| 5.11.5             | Flash Data Register (FIU_DATA)                     |

| 5.11.6             | Flash Interrupt Enable Register (FIU_IE)           |

| 5.11.6.            |                                                    |

| 5.11.6.            | 2 Interrupt Enable (IE)—Bits 11–0                  |

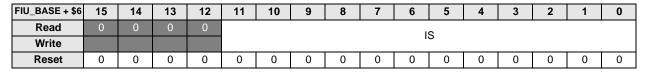

| 5.11.7    | Flash Interrupt Source Register (FIU_IS)                 | 5-23 |

|-----------|----------------------------------------------------------|------|

| 5.11.7.1  | Reserved—Bits 15–12                                      | 5-23 |

| 5.11.7.2  | Interrupt Source (IS)—Bit 11                             | 5-23 |

| 5.11.7.3  | Interrupt Source (IS)—Bit 10                             | 5-24 |

| 5.11.7.4  | Interrupt Source (IS)—Bit 9                              | 5-24 |

| 5.11.7.5  | Interrupt Source (IS)—Bit 8                              |      |

| 5.11.7.6  | Interrupt Source (IS)—Bit 7                              | 5-24 |

| 5.11.7.7  | Interrupt Source (IS)—Bit 6                              |      |

| 5.11.7.8  | Interrupt Source (IS)—Bit 5                              |      |

| 5.11.7.9  | Interrupt Source (IS)—Bit 4                              |      |

| 5.11.7.10 |                                                          |      |

| 5.11.7.11 | Interrupt Source (IS)—Bit 2                              |      |

| 5.11.7.12 |                                                          |      |

| 5.11.7.13 |                                                          |      |

| 5.11.8    | Flash Interrupt Pending Register (FIU_IP)                |      |

| 5.11.8.1  | Reserved—Bits 15–12                                      |      |

| 5.11.8.2  | Interrupt Pending (IP)—Bits 11–0                         | 5-25 |

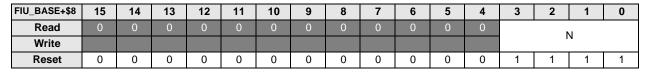

| 5.11.9    | Flash Clock Divisor Register (FIU_CLKDIVISOR)            |      |

| 5.11.9.1  | Reserved—Bits 15–4                                       |      |

| 5.11.9.2  | Clock Divisor (N)—Bits 3–0                               | 5-26 |

| 5.11.10   | Flash TERASE Limit Register (FIU_TERASEL)                |      |

| 5.11.10.1 | Reserved—Bits 15–7                                       |      |

| 5.11.10.2 | Timer Erase Limit (TERASEL)—Bits 6–0                     | 5-26 |

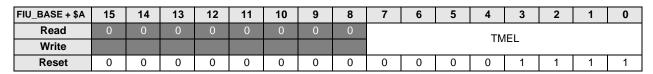

| 5.11.11   | Flash TME Limit Register (FIU_TMEL)                      |      |

| 5.11.11.1 | Reserved—Bits 15–8                                       | 5-27 |

| 5.11.11.2 |                                                          |      |

| 5.11.12   | Flash TNVS Limit Register (FIU_TNVSL)                    | 5-27 |

| 5.11.12.1 | Reserved—Bits 15–11                                      | 5-27 |

| 5.11.12.2 | Timer Non-Volatile Storage Limit (TNVSL)—Bits 10–0       | 5-28 |

| 5.11.13   | Flash TPGS Limit Register (FIU_TPGSL)                    | 5-28 |

| 5.11.13.1 | Reserved—Bits 15–12                                      |      |

| 5.11.13.2 | Timer Program Setup Limit (TPGSL)—Bits 11–0              | 5-28 |

| 5.11.14   | Flash TPROG Limit Register (FIU_TPROGL)                  | 5-28 |

| 5.11.14.1 | Reserved—Bits 15–14                                      |      |

| 5.11.14.2 | Timer Program Limit (TPROGL)—Bits 13–0                   | 5-29 |

| 5.11.15   | Flash TNVH Limit Register (FIU_TNVHL)                    | 5-29 |

| 5.11.15.1 | Reserved—Bits 15–11                                      |      |

| 5.11.15.2 | Timer Non-Volatile Hold Limit (TNVHL)—Bits 10–0          | 5-29 |

| 5.11.16   | Flash TNVH1 Limit Register                               | 5-30 |

| 5.11.16.1 | Reserved—Bit 15                                          |      |

| 5.11.16.2 | Timer Non-Volatile Hold 1 Limit (TNVH1L[14:0])—Bits 14–0 | 5-30 |

| 5.11.17   | Flash TRCV Limit Register (FIU_TRCVL)                    | 5-30 |

| 5.11.17.1 | Reserved—Bits 15–9                                       | 5-30 |

DSP56F800 Family User's Manual, Rev. 8

Freescale Semiconductor

Table of Contents - v

| 5.11.1 | 7.2 Timer Recovery Limit (TRCVL[8:0])—Bits 8–0 5-31 |

|--------|-----------------------------------------------------|

| 5.11.1 | 8 Flash Interface Unit Timeout Registers5-31        |

| 5.12   | Reset                                               |

| 5.13   | Interrupts                                          |

|        |                                                     |

|        | pter 6                                              |

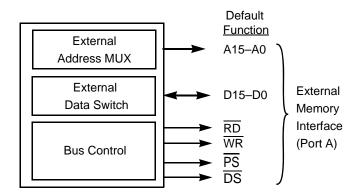

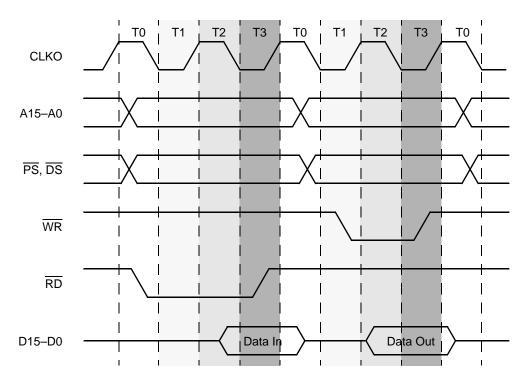

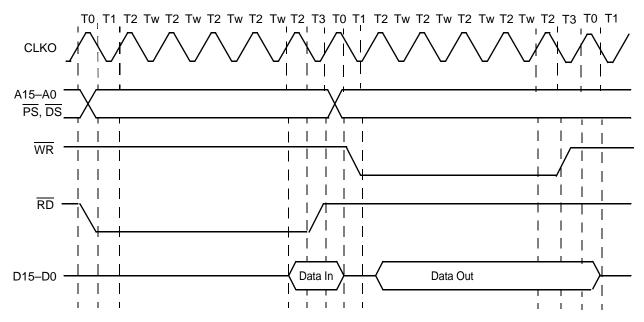

| Exte   | ernal Memory Interface (EMI)                        |

| 6.1    | Introduction                                        |

| 6.2    | Block Diagram                                       |

| 6.2.1  | External Memory Port Architecture                   |

| 6.3    | Pin Descriptions                                    |

| 6.4    | Register Definition                                 |

| 6.4.1  | Bus Control Register (BCR)                          |

| 6.4.1. |                                                     |

| 6.4.1. | 2 Drive (DRV)—Bit 9                                 |

| 6.4.1. | 3 Reserved—Bit 8                                    |

| 6.4.1. | Wait State X Data Memory (WSX)—Bits 7–4 6-3         |

| 6.4.1. |                                                     |

| 6.4.2  | State of Pins in Different Processing States        |

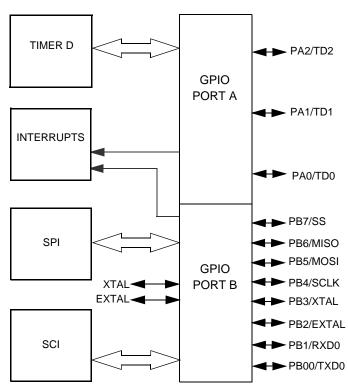

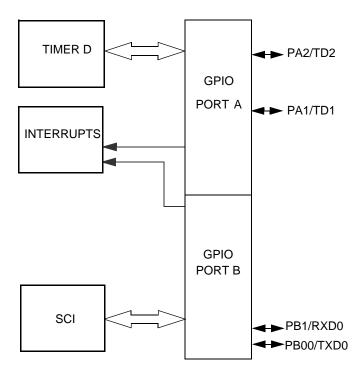

|        | pter 7<br>eral Purpose Input/Output (GPIO)          |

| 7.1    | Introduction                                        |

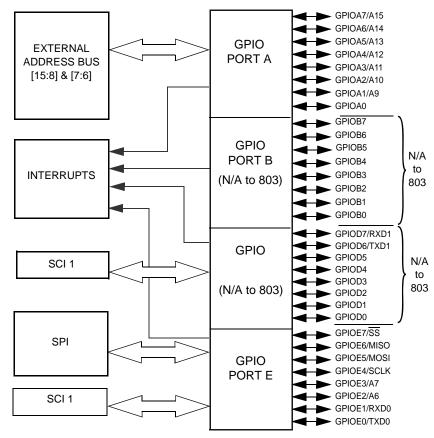

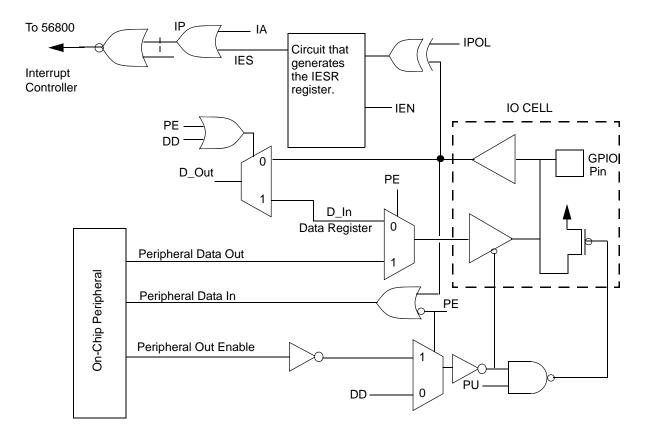

| 7.2    | Block Diagrams                                      |

| 7.2.1  | Summary: Dedicated and Multiplexed GPIOs7-3         |

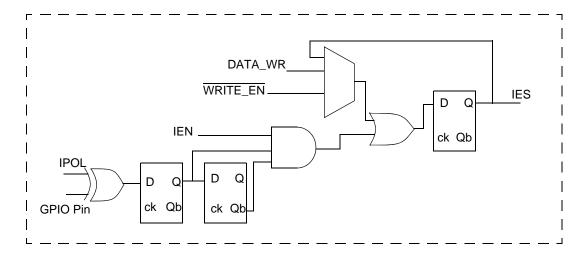

| 7.3    | GPIO Interrupts                                     |

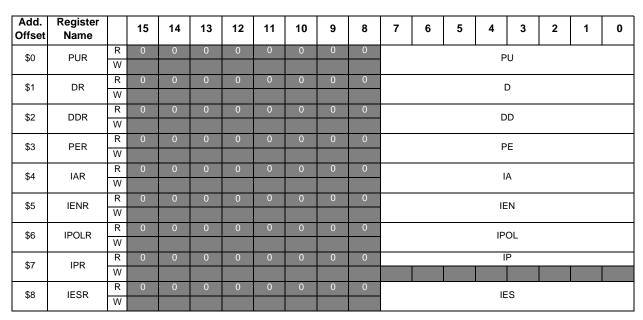

| 7.4    | Register Definitions                                |

| 7.5    | Chip Specific Configurations                        |

| 7.6    | Register Definitions                                |

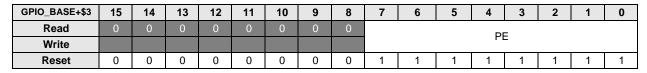

| 7.6.1  | Pull-Up Enable Register (PUR)7-10                   |

| 7.6.2  | Data Register (DR)                                  |

| 7.6.3  | Data Direction Register (DDR)                       |

| 7.6.4  | Peripheral Enable Register (PER)                    |

| 7.6.5  | Interrupt Assert Register (IAR)                     |

| 7.6.6  | Interrupt Enable Register (IENR)                    |

| 7.6.7  | Interrupt Polarity Register (IPOLR)                 |

| 7.6.8  | Interrupt Pending Register (IPR)                    |

| 7.6.9  | Interrupt Edge Sensitive Register (IESR)            |

| 7.7    | GPIO Programming Algorithms                         |

DSP56F800 Family User's Manual, Rev. 8

Table of Contents - vi Freescale Semiconductor

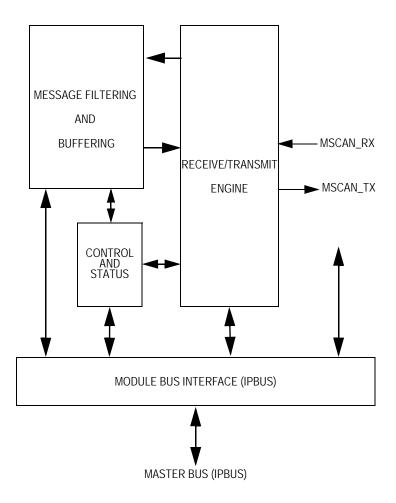

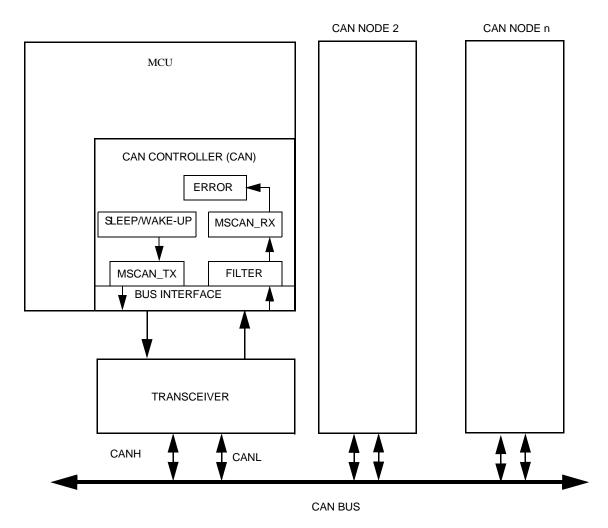

#### Chapter 8 Controller Area Network (CAN)

| 8.1 Introduction                                       | 8-1  |

|--------------------------------------------------------|------|

| 8.2 Features                                           | 8-1  |

| 8.3 Block Diagram                                      | 8-3  |

| 8.4 Functional Description                             | 8-3  |

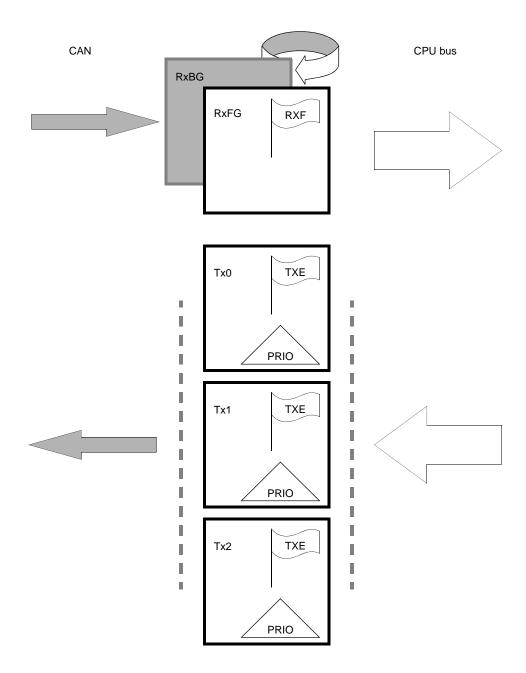

| 8.4.1 Message Storage                                  | 8-3  |

| 8.4.1.1 Message Transmit Background                    |      |

| 8.4.1.2 Transmit Structures                            | 8-6  |

| 8.4.1.3 Receive Structures                             | 8-7  |

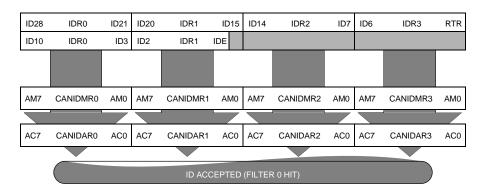

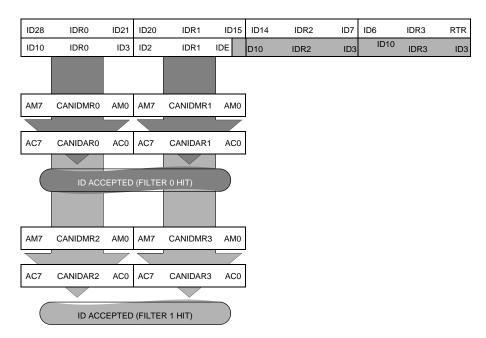

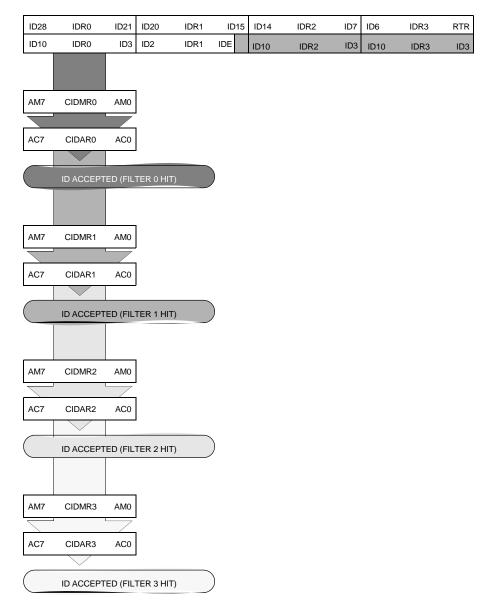

| 8.4.1.4 Identifier Acceptance Filter                   | 8-8  |

| 8.4.2 Protocol Violation Protection                    | 8-11 |

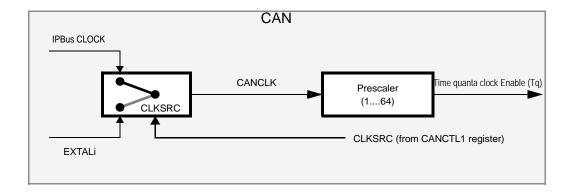

| 8.4.3 Clock System                                     | 8-12 |

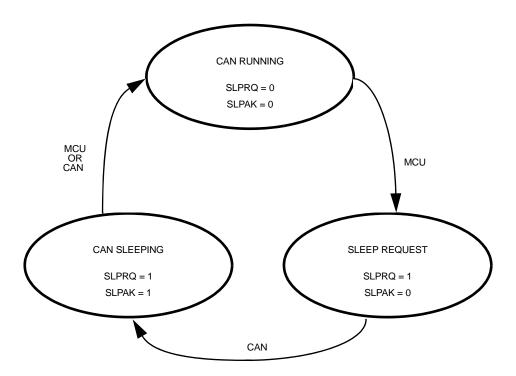

| 8.5 Operating Modes                                    | 8-15 |

| 8.5.1 Normal Modes                                     | 8-15 |

| 8.5.2 Special Modes                                    | 8-15 |

| 8.5.3 Emulation Modes                                  |      |

| 8.5.4 Security Modes                                   | 8-15 |

| 8.6 Pin Definitions                                    | 8-15 |

| 8.7 Register Definitions                               | 8-16 |

| 8.7.1 CAN Control Register 0 (CANCTL0)                 | 8-23 |

| 8.7.1.1 Reserved—Bits 15–8                             | 8-24 |

| 8.7.1.2 Received Frame Flag (RXFRM)—Bit 7              | 8-24 |

| 8.7.1.3 Receiver Active Status (RXACT)—Bit 6           |      |

| 8.7.1.4 CAN Stops in Wait Mode (CSWAI)—Bit 5           |      |

| 8.7.1.5 Synchronized Status (SYNCH)—Bit 4              |      |

| 8.7.1.6 Reserved—Bit 3                                 |      |

| 8.7.1.7 Sleep Acknowledge (SLPAK)—Bit 2                |      |

| 8.7.1.8 Sleep Request–Go Into Sleep Mode (SLPRQ)—Bit 1 |      |

| 8.7.1.9 Soft Reset (SFTRES)—Bit 0                      |      |

| 8.7.2 CAN Control Register 1 (CANCTL1)                 |      |

| 8.7.2.1 Reserved—Bits 15–8                             |      |

| 8.7.2.2 CAN Enable (CANE)—Bit 7                        |      |

| 8.7.2.3 Reserved—Bits 6–3                              |      |

| 8.7.2.4 Loop Back Self Test Mode (LOOPB)—Bit 2         |      |

| 8.7.2.5 Wake-Up Mode (WUPM)—Bit 1                      |      |

| 8.7.2.6 CAN Clock Source (CLKSRC)—Bit 0                |      |

| 8.7.3.1 Reserved—Bits 15–8                             |      |

| 8.7.3.2 Synchronization Jump Width (SJW)—Bits 7–6      |      |

| 8.7.3.3 Baud Rate Prescaler (BRP)—Bits 5–0             |      |

| 8.7.4 CAN Bus Timing Register 1 (CANBTR1)              |      |

| o o o                                                  | 0 20 |

| 8.7.4.1  | Reserved—Bits 15–8                                        | 8-29 |

|----------|-----------------------------------------------------------|------|

| 8.7.4.2  | Sampling (SAMP)—Bit 7                                     |      |

| 8.7.4.3  | Time Segment 2 (TSEG22–TSEG20)—Bits 6–4                   |      |

| 8.7.4.4  | Time Segment 1 (TSEG13–TSEG10)—Bits 3–0                   | 8-30 |

| 8.7.5    | CAN Receiver Flag Register (CANRFLG)                      |      |

| 8.7.5.1  | Reserved—Bits 15–8                                        |      |

| 8.7.5.2  | Wake-Up Interrupt Flag (WUPIF)—Bit 7                      |      |

| 8.7.5.3  | Receiver Warning Interrupt Flag (RWRNIF)—Bit 6            | 8-31 |

| 8.7.5.4  | Transmitter Warning Interrupt Flag (TWRNIF)—Bit 5         | 8-32 |

| 8.7.5.5  | Receiver Error Passive Interrupt Flag (RERRIF)—Bit 4      | 8-32 |

| 8.7.5.6  | Transmitter Error Passive Interrupt Flag (TERRIF)—Bit 3   | 8-32 |

| 8.7.5.7  | Bus Off Interrupt Flag (BOFFIF)—Bit 2                     | 8-32 |

| 8.7.5.8  | Overrun Interrupt Flag (OVRIF)—Bit 1                      | 8-33 |

| 8.7.5.9  | Receive Buffer Full (RXF)—Bit 0                           | 8-33 |

| 8.7.6    | CAN Receiver Interrupt Enable Register (CANRIER)          | 8-33 |

| 8.7.6.1  | Reserved—Bits 15–8                                        |      |

| 8.7.6.2  | Wake-Up Interrupt Enable (WUPIE)—Bit 7                    |      |

| 8.7.6.3  | Receiver Warning Interrupt Enable (RWRNIE)—Bit 6          |      |

| 8.7.6.4  | Transmitter Warning Interrupt Enable (TWRNIE)—Bit 5       |      |

| 8.7.6.5  | Receiver Error Passive Interrupt Enable (RERRIE)—Bit 4    |      |

| 8.7.6.6  | Transmitter Error Passive Interrupt Enable (TERRIE)—Bit 3 |      |

| 8.7.6.7  | Bus Off Interrupt Enable (BOFFIE)—Bit 2                   |      |

| 8.7.6.8  | Overrun Interrupt Enable (OVRIE)—Bit 1                    |      |

| 8.7.6.9  | Receiver Full Interrupt Enable (RXFIE)—Bit 0              | 8-35 |

| 8.7.7    | CAN Transmitter Flag Register (CANTFLG)                   |      |

| 8.7.7.1  | Reserved—Bits 15–7                                        |      |

| 8.7.7.2  | Abort Acknowledge (ABTAK)—Bits 6–4                        |      |

| 8.7.7.3  | Reserved—Bits 3                                           |      |

| 8.7.7.4  | Transmitter Buffer Empty (TXE)—Bits 2–0                   |      |

| 8.7.8    | CAN Transmitter Control Register (CANTCR)                 |      |

| 8.7.8.1  | Reserved—Bits 15–7                                        |      |

| 8.7.8.2  | Abort Request (ABTRQ)—Bits 6–4                            |      |

| 8.7.8.3  | Reserved—Bit 3                                            |      |

| 8.7.8.4  | Transmitter Empty Interrupt Enable (TXEIE)—Bits 2–0       |      |

| 8.7.9    | CAN Identifier Acceptance Control Register (CANIDAC)      |      |

| 8.7.9.1  | Reserved—Bits 15–6                                        |      |

| 8.7.9.2  | Identifier Acceptance Mode (IDAM)—Bits 5–4                |      |

| 8.7.9.3  | Reserved—Bit 3                                            |      |

| 8.7.9.4  | Identifier Acceptance Hit Indicator (IDHIT)—Bits 2–0      |      |

| 8.7.10   | CAN Receive Error Counter Register (CANRXERR)             |      |

| 8.7.11   | CAN Transmit Error Counter Register (CANTXERR)            |      |

| 8.7.12   | CAN Identifier Acceptance Registers (CANIDAR0–7)          |      |

| 8.7.12.1 | Acceptance Code Bits (AC)—Bits 7–0                        | 8-40 |

Table of Contents - viii Freescale Semiconductor

| 8.7.13     | 9.2.2.2.2.4.2.2.4.4.2.4.4.4.4.4.4.4.4.4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 8.7.13     | 3.1 Acceptance Mask Bits (AM)—Bits 7–0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8-41 |

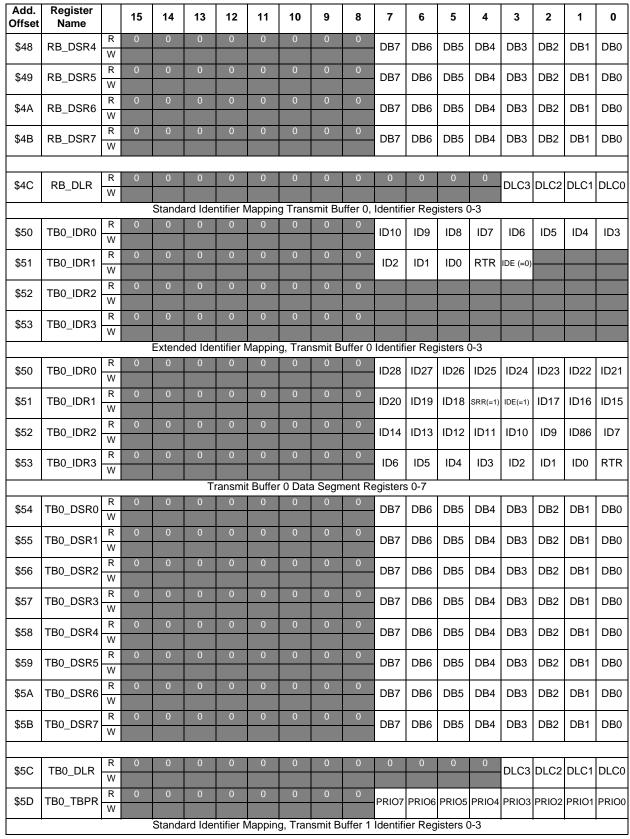

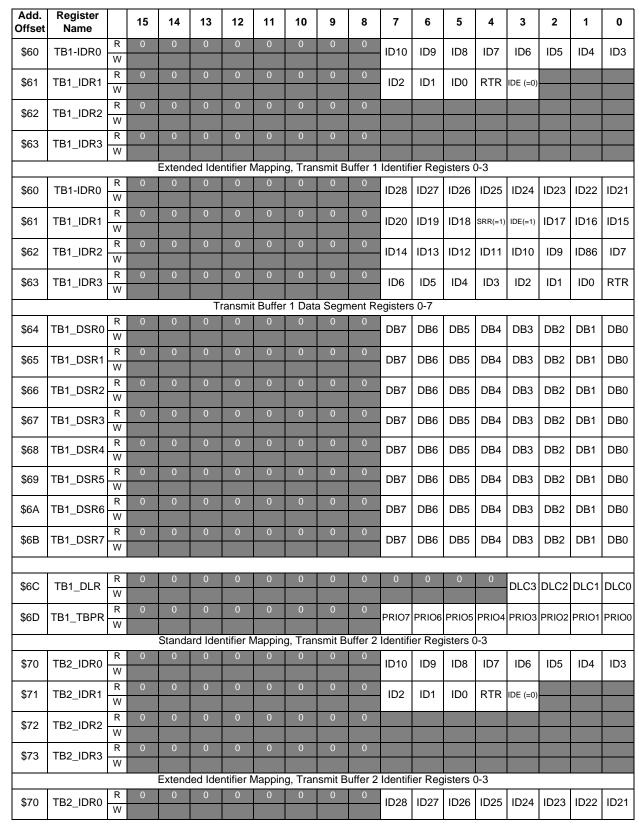

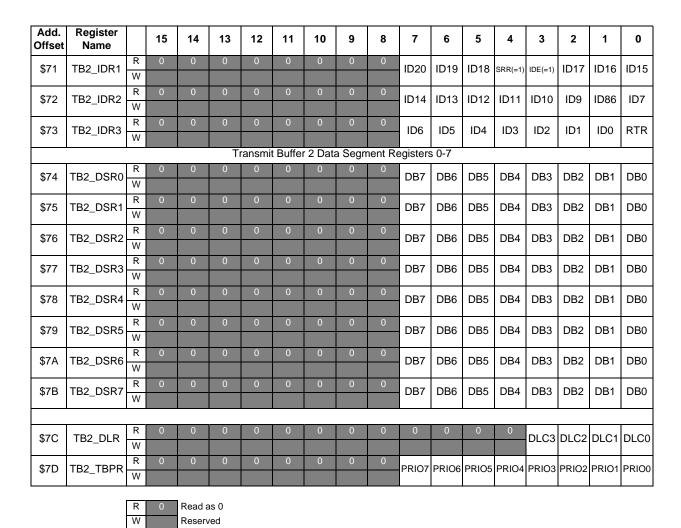

| 8.7.14     | Programmer's Model of Message Storage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 8-42 |

| 8.7.15     | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

| 8.7.15     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| 8.7.15     | the state of the s |      |

| 8.7.15     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| 8.7.15     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| 8.7.15     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| 8.7.16     | , , , , , , , , , , , , , , , , , , , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

| 8.7.17     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| 8.7.18     | , , , , , , , , , , , , , , , , , , , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

| 8.8        | Low Power Options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

| 8.8.1      | Run Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 8-49 |

| 8.8.2      | Wait Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 8-49 |

| 8.8.3      | Stop Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

| 8.8.4      | Sleep Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

| 8.8.5      | Soft Reset Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| 8.8.6      | Power Down Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| 8.8.7      | Programmable Wake-Up Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

| 8.9        | Interrupt Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

| 8.9.1      | Interrupt Acknowledge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 8-55 |

| 8.9.2      | Interrupt Sources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |