MPS

6520

PERIPHERAL

ADAPTER

# **6520 PERIPHERAL ADAPTER**

### **DESCRIPTION**

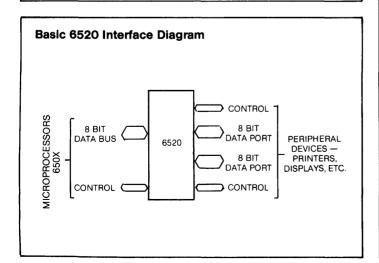

The 6520 Peripheral Adapter is designed to solve a broad range of peripheral control problems in the implementation of microcomputer systems. This device allows a very effective trade-off between software and hardware by providing significant capability and flexibility in a low cost chip. When coupled with the power and speed of the 6500 family of microprocessors, the 6520 allows implementation of very complex systems at a minimum overall cost.

Control of peripheral devices is handled primarily through two 8-bit bi-directional ports. Each of these lines can be programmed to act as either an input or an output. In addition, four peripheral control/interrupt input lines are provided. These lines can be used to interrupt the processor or for "hand-shaking" data between the processor and a peripheral device.

# **FEATURES**

- High performance replacement for Motorola/AMI /MOSTEK/Hitachi peripheral adapter.

- N channel, depletion load technology, single +5V supply.

- Completely Static and TTL compatible.

- CMOS compatible peripheral control lines.

- Fully automatic "hand-shake" allows very positive control of data transfers between processor and peripheral devices.

#### **SUMMARY OF 6520 OPERATION**

See MOS TECHNOLOGY Microcomputer Hardware Manual for detailed description of 6520 operation.

# CA1/CBI CONTROL

| CRA (CRB) |       | (CRB) | Active Transition | IRQA (IRQB)                                                                                  |  |  |  |  |  |

|-----------|-------|-------|-------------------|----------------------------------------------------------------------------------------------|--|--|--|--|--|

|           | Bit 1 | BitO  | of Input Signal*  | Interrupt Outputs                                                                            |  |  |  |  |  |

|           | 0     | 0     | negative          | Disable — remain high                                                                        |  |  |  |  |  |

|           | 0     | 1     | negative          | Enable — goes low when bit 7 in CRA (CRB) is set by active transition of signal on CA1 (CB1) |  |  |  |  |  |

|           | 1     | 0     | positive          | Disable — remain high                                                                        |  |  |  |  |  |

|           | 1     | 1     | positive          | Enable — as explained above                                                                  |  |  |  |  |  |

\*Note: Bit 7 of CRA (CRB) will be set to a logic 1 by an active transition of the CA1 (CB1) signal. This is independent of the state of Bit 0 in CRA (CRB).

# CA2/CB2 INPUT MODES

| CRA (CRB)             |   |   |   | l,                                    |                                                                                              |

|-----------------------|---|---|---|---------------------------------------|----------------------------------------------------------------------------------------------|

| Bit 5   Bit 4   Bit 3 |   |   |   | Active Transition<br>of Input Signal* | IRQA (IRQB)<br>Interrupt Output                                                              |

|                       | 0 | 0 | 0 | negative                              | Disable — remains high                                                                       |

|                       | 0 | 0 | 1 | negative                              | Enable — goes low when bit 6 in CRA (CRB) is set by active transition of signal on CA2 (CB2) |

|                       | 0 | 1 | 0 | positive                              | Disable — remains high                                                                       |

|                       | 0 | 1 | 1 | positive                              | Enable — as explained above                                                                  |

\*Note: Bit 6 of CRA (CRB) will be set to a logic 1 by an active transition of the CA2 (CB2) signal. This is independent of the state of Bit 3 in CRA (CRB).

#### **CA2 OUTPUT MODES**

| CRA |       | 1     |       |                        |                                                                                                                                                                                                                                     |  |  |

|-----|-------|-------|-------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|     | Bit 5 | Bit 4 | Bit 3 | Mode                   | Description                                                                                                                                                                                                                         |  |  |

|     | 1     | 0     | 0     | "Handshake"<br>on Read | CA2 is set high on an active transition of the CA1 interrupt input signal and set low by a microprocessor "Read A Data" operation. This allows positive control of data transfers from the peripheral device to the microprocessor. |  |  |

|     | 1     | 0     | 1     | Pulse Output           | CA2 goes low for one cycle after a "Read A Data" operation. This pulse can be used to signal the peripheral device that data was taken.                                                                                             |  |  |

|     | 1     | 1     | 0     | Manual Output          | CA2 set low                                                                                                                                                                                                                         |  |  |

|     | 1     | l 1   | 1     | Manual Output          | CA2 set high                                                                                                                                                                                                                        |  |  |

# **CB2 OUTPUT MODES**

|   | Bit 5 | CRB<br>Bit 4 | Bit 3 | Mode                    | Description                                                                                                                                                                                                                           |

|---|-------|--------------|-------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| - | 1     | 0            | 0     | "Handshake"<br>on Write | CB2 is set low on microprocessor "Write B Data" operation and is set high by an active transition of the CB1 interrupt input signal. This allows positive control of data transfers from the microprocessor to the peripheral device. |

|   | 1     | 0            | 1     | Pulse Output            | CB2 goes low for one cycle after a microprocessor "Write B Data" operation. This can be used to signal the peripheral device that data is available.                                                                                  |

|   | 1     | 1            | 0     | Manual Output           | CB2 set low                                                                                                                                                                                                                           |

|   | 1     | 1            | 1     | Manual Output           | CB2 set high                                                                                                                                                                                                                          |

#### **MAXIMUM RATINGS**

Supply Voltage, V<sub>CC</sub> -0.3 to +7.0V Input Voltage, V<sub>IN</sub> -0.3 to +7.0V Operating Temperature Range, T<sub>A</sub> 0 to +70°C Storage Temperature Range, T<sub>STG</sub> -55 to +150°C

This device contains circuitry to protect the inputs against damage due to high static voltages, however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this circuit.

#### COMMENT

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of this device at these or any other conditions above those indicated in the operational sections of this specification is not implied and exposure to absolute maximum rating conditions for extended periods may affect device reliability.

STATIC D.C. CHARACTERISTICS (V<sub>CC</sub> = 5.0 V  $\pm$  5%, V<sub>SS</sub> = 0, T<sub>A</sub> = 25°C unless otherwise noted)

| Characteristic                                                                             | Symbol | Min   | Тур      | Max  | Unit   |

|--------------------------------------------------------------------------------------------|--------|-------|----------|------|--------|

| Input High Voltage (Normal Operating Levels)                                               | VIH    | +2.0  | _        | VCC  | Vdc    |

| Input Low Voltage (Normal Operating Levels)                                                | VIL    | -0.3  | name.    | +.8  | Vdc    |

| Input Threshold Voltage                                                                    | VIT    | 0.8   |          | 2.0  | Vdc    |

| Input Leakage Current                                                                      | IN     |       |          | uAdc | μAdc   |

| $V_{in} = 0 \text{ to } 5.0 \text{ Vdc}$                                                   |        |       | ±1.0     | ±2.5 |        |

| "R/W, Reset, RS0,RS1,CS0,CS1,CS2,CA1,CB1,Ø2                                                |        |       |          |      |        |

| Three-State (Off State Input Current)                                                      | ITSI   |       | ±2.0     | ±10  | ,uAdc  |

| (Vin = 0.4 to 2.4 Vdc, V <sub>CC</sub> = max) D0-D7,PB0-PB7,CB2<br>Input High Current      | UH     | _     | 12.0     | 110  | μλασ   |

| $(V_{IH} = 2.4 \text{ Vdc}) \text{ PAO-PA7,CA2}$                                           | I 'IH  | -100  | -250     |      | μAdc   |

| Input Low Current                                                                          | l IIL  | 100   |          |      | μασ    |

| $(V_{11} = 0.4 \text{ Vdc}) \text{ PA0-PA7,CA2}$                                           | ,,,,   |       | -1.0     | -1.6 | mAdc   |

| Output High Voltage                                                                        | VOH    |       |          |      |        |

| $(V_{CC} = min, 1_{Load} = -100 \text{ uAdc})$                                             | 011    | 2.4   | _        | -    | Vdc    |

| Output Low Voltage                                                                         | VOL    |       |          |      |        |

| $(V_{CC} = min, 1_{Load} = 1.6 \text{ mAdc})$                                              |        | _     | _        | +0.4 | Vdc    |

| Output High Current (Sourcing)                                                             | ЧОН    |       |          |      | A -1 - |

| $(V_{OH} = 2.4 \text{ Vdc})$                                                               |        | -100  | -1000    | _    | µAdc   |

| $^{(VO)}$ = 1.5 Vdc, the current for driving other than                                    |        | -1.0  | -2.5     |      | mAdc   |

| TTL, e.g., Darlington Base) PB0-PB7,CB2                                                    | 1      |       | i        |      |        |

| Output Low Current (Sinking)                                                               | l lor  |       |          |      |        |

| (VOL = 0.4 Vdc)                                                                            |        | 1.6 - |          | _    | mAdc   |

| Output Leakage Current (Off State) IRQA, IRQB                                              | off    | _     | 1.0      | 10   | μAdc   |

| Power Dissipation                                                                          | PD     | _     | 200      | 500  | mW     |

| Input Capacitance                                                                          | Cin    |       |          |      | pF     |

| (V <sub>in</sub> - 0, T <sub>A</sub> = 25°C, f = 1.0 MHz)<br>D0-D7.PA0-PA7.PB0-PB7.CA2.CB2 | 1      | i     |          | 10   | 1      |

| R/W,Reset,RS0,RS1,CS0,CS1,CS2,                                                             |        |       |          | 7.0  |        |

| CA1,CB1,Ø2                                                                                 |        |       | _        | 20   |        |

| Output Capacitance                                                                         | Cout   |       | <b>[</b> | ===  |        |

| $(V_{in} - 0, T_A = 25^{\circ}C, f = 1.0 \text{ MHz})$                                     | - 501  | _     | _        | 10   | рF     |

NOTE: Negative sign indicates outward current flow, positive indicates inward flow.

# A.C. CHARACTERISTICS

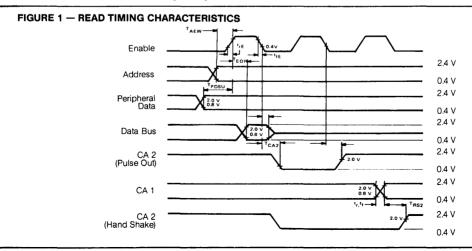

Figure 1 — Read Timing Characteristics (Loading 130 pF and one TTL load)

| Characteristics                                                   | Symbol  | Min | Тур | Max | Unit |

|-------------------------------------------------------------------|---------|-----|-----|-----|------|

| Delay Time, Address valid to Enable positive transition           | TAEW    | 180 | _   | _   | ns   |

| Delay Time, Enable positive transition to Data valid on bus       | TEDR    | l – | _   | 395 | ns   |

| Peripheral Data Setup Time                                        | TPDSU   | 300 |     | _   | ns   |

| Data Bus Hold Time                                                | THR     | 10  |     | _   | ns   |

| Delay Time, Enable negative transition to CA2 negative transition | TCA2    | l — | _   | 1.0 | μs   |

| Delay Time, Enable negative transition to CA2 positive transition | TRS1    | . – |     | 1.0 | us   |

| Rise and Fall Time for CA1 and CA2 input signals                  | tritf   | l – | _   | 1.0 | μs   |

| Delay Time from CA1 active transition to CA2 positive transition  | TRS2    | -   | _   | 2.0 | μs   |

| Rise and Fall Time for Enable input                               | trE,tfE |     |     | 25  | ņs   |

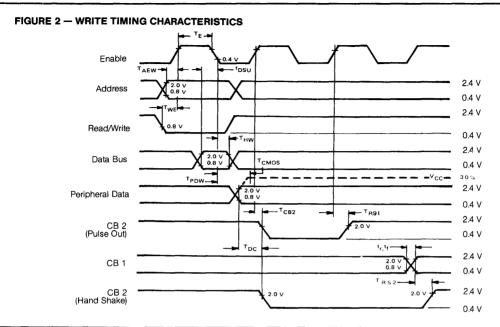

Figure 2 — Write Timing Characteristics

| Characteristics                                                                                | Symbol           | Min   | Тур | Max | Unit   |

|------------------------------------------------------------------------------------------------|------------------|-------|-----|-----|--------|

| Enable Pulse Width                                                                             | TF               | 0.470 |     | 25  | μs     |

| Delay Time, Address valid to Enable positive transition                                        | TAEW             | 180   | _   | _   | ns l   |

| Delay Time, Data valid to Enable negative transition                                           | TDSU             | 300   | _   | _   | l ns l |

| Delay Time, Read/Write negative transition to Enable positive transition                       | TWE              | 130   | _   | _   | ns     |

| Data Bus Hold Time                                                                             | THW              | 10    | _   | _   | l ns l |

| Delay Time, Enable negative transition to Peripheral Data valid                                | TPDW             | -     | _   | 1.0 | l us   |

| Delay Time, Enable negative transition to Peripheral Data valid, CMOS (VCC - 30%) PA0-PA7, CA2 | TCMOS            | -     |     | 2.0 | jus    |

| Delay Time, Enable positive transition to CB2 negative transition                              | T <sub>CB2</sub> | -     | _   | 1.0 | l us l |

| Delay Time, Peripheral Data valid to CB2 negative transition                                   | TDC              | 0     | _   | 1.5 | us l   |

| Delay Time, Enable positive transition to CB2 positive transition                              | TRS1             | _     | -   | 1.0 | μs     |

| Rise and Fall Time for CB1 and CB2 input signals                                               | tr. tr           | -     | _   | 1.0 | us l   |

| Delay Time, CB1 active transition to CB2 positive transition                                   | TRS2             |       |     | 2.0 | μs     |

COMMODQRE SEMICONDUCTOR GROUP reserves the right to make changes to any products herein to improve reliability, function or design. COMMODORE SEMICONDUCTOR GROUP does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others.