# 6532 (MEMORY, I/O, TIMER ARRAY)

# THE 6532 CONCEPT-

The 6532 is designed to operate in conjunction with the MCS650X Microprocessor Family. It is comprised of a 128 x 8 static RAM, two software controlled 8 bit bi-directional data ports allowing direct interfacing between the microprocessor unit and peripheral devices, a software programmable interval timer with interrupt capable of timing in various intervals from 1 to 262,144 clock periods, and a programmable edge detect circuit.

# FEATURES OF THE 6532

- 8 bit bi-directional Data Bus for direct communication with the microprocessor

- Programmable edge-sensitive interrupt

- 128 x 8 static RAM

- Two 8 bit bi-directional data ports for interface to peripherals

- Two programmable I/O Peripheral Data Direction Registers

- Programmable Interval Timer

- Programmable Interval Timer Interrupt

- TTL & CMOS compatible peripheral lines

- Peripheral pins with Direct Transistor

- Drive Capability

- High Impedance Three-State Data Pins

- 1MHz, 2MHz and 3MHz operation

# 8532 PIN DESIGNATION

| VSS  | d,                                                                                                                                  | 40 | A6    |

|------|-------------------------------------------------------------------------------------------------------------------------------------|----|-------|

| A5   |                                                                                                                                     | 39 | Ø2    |

| A4   | d3                                                                                                                                  | 38 | CSI   |

| A3   | □                                                                                                                                   | 37 | CS2   |

| A2   | <b>5</b>                                                                                                                            | 36 | RS    |

| AI   | <b>4</b> 6                                                                                                                          | 35 | R/W   |

| AO   | 2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>0<br>1<br>1<br>2<br>3<br>4<br>5<br>1<br>4 | 34 | RES   |

| PAO  | d.                                                                                                                                  | 33 | DBO   |

| PAI  | d,                                                                                                                                  | 32 | DBI   |

| PA2  |                                                                                                                                     | 31 | D82   |

| PA 3 |                                                                                                                                     | 30 | D83   |

| PA4  | <b> </b>                                                                                                                            | 29 | 084   |

| PA5  | <b>C</b> 13                                                                                                                         | 28 | D85   |

| PA6  |                                                                                                                                     | 27 | 086   |

| PA7  | <b>_</b> '5                                                                                                                         | 26 | 087   |

| P87  | <b>16</b>                                                                                                                           | 25 | IRQ   |

| PB6  | []16<br>[]17                                                                                                                        | 24 | PBO   |

| P85  | <b>C</b> 18                                                                                                                         | 23 | PB)   |

| PB4  | C 19                                                                                                                                | 22 | PB2   |

| VDD  | 20                                                                                                                                  | 21 | P 8 3 |

|      |                                                                                                                                     |    |       |

BLOCK DIAGRAM

PERIPHERALS

# **MAXIMUM RATINGS**

| RATING                      | SYMBOL | VOLTAGE       | UNIT |  |  |

|-----------------------------|--------|---------------|------|--|--|

| Supply Voltage              | vcc    | 3 to +7.0     | v    |  |  |

| Input/Output Voltage        | VIN    | 3 to +7.0     | v    |  |  |

| Operating Temperature Range | TOP    | 0 to 70       | •c   |  |  |

| Storage Temperature Range   | TSTG   | - 55 to + 150 | •c   |  |  |

All inputs contain protection circuitry to prevent damage due to high static charges. Care should be exercised to prevent unnecessary application of voltage outside the specified range.

# ELECTRICAL CHARACTERISTICS (VCC = $5.0v \pm 5\%$ , VSS = 0v, T<sub>A</sub> = $0.70^{\circ}$ C)

| CHARACTERISTIC                                                                                        | SYMBOL  | MIN.                  | TYP.   | MAX.                 | UNIT |

|-------------------------------------------------------------------------------------------------------|---------|-----------------------|--------|----------------------|------|

| Input High Voltage                                                                                    | ⊻ін     | V <sub>SS</sub> + 2.4 | 1.3    | vcc                  | v    |

| Input Low Voltage                                                                                     | VIL     | V <sub>SS</sub> – .3  | 1.1    | V <sub>SS</sub> + .8 | v    |

| Input Leakage Current; V <sub>IN</sub> = V <sub>SS</sub> + 5v<br>A0-A6, RS, RW, RES, Ø2, CS1, CS2     | IIN     | -                     | 1.0    | 2.5                  | Au   |

| Input Leakage Current for High Impedance State<br>(Three State); V <sub>IN</sub> = .4v to 2.4v; D0-D7 | ITSI    | -                     | ± 1.0  | ± 10.0               | Aµ   |

| Input High Current; V <sub>IN</sub> = 2.4v<br>PAO-PA7, P3O-PB7                                        | Ϋн      | - 100.                | - 300. | -                    | ۸    |

| Input Low Current; V <sub>IN</sub> = .4v<br>PA0-PA7, PB0-PB7                                          | ιL      | _                     | - 1.0  | - 1.6                | mA   |

| Output High Voltage                                                                                   |         |                       |        |                      |      |

| VCC = MIN, $I_{LOAD} \leq \cdot 100 \mu A$ (PAO-PA7, PBO-PB7, DO-D7)                                  | ∨он     | VSS + 2.4             | 3.5    | vcc                  | v    |

| Output Low Voltage                                                                                    |         |                       |        |                      |      |

| VCC = MIN, $I_{LOAD} \le 1.6MA$                                                                       | VOL     | VSS                   | .2     | VSS + .4             | v    |

| Output High Current (Sourcing);<br>VOH ≥ 2.4v (PAO-PA7, PBO-PB7, DO-D7)                               | •<br>ЮН | - 100                 | - 1000 | _                    | هم   |

| Output Low Current (Sinking); VOL <u>&lt;</u> .4v (PA0-PA7) (PB0-PB7)                                 | IOL     | 1.6                   | 3.0    |                      | mA   |

| Clock Input Capacitance                                                                               | CClk    | -                     | 18     | 30                   | pf   |

| Input Capacitance                                                                                     | CIN     | _                     | 7      | 10                   | pf   |

| Output Capacitance                                                                                    | Cour    | _                     | 7      | 10                   | pf   |

| Power Dissipation                                                                                     | PD      | _                     | 500    | 1000                 | mW   |

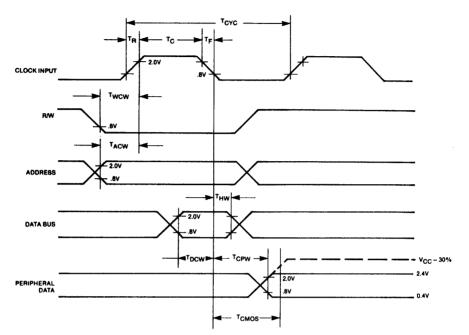

# WRITE TIMING CHARACTERISTICS

# **READ TIMING CHARACTERISTICS**

|                                                                                             |        | 1 MHz |     | 2MHz |      | 3MHz  |      |          |  |

|---------------------------------------------------------------------------------------------|--------|-------|-----|------|------|-------|------|----------|--|

| CHARACTERISTIC                                                                              | SYMBOL | MIN   | MAX | MIN  | MAX  | MIN   | мах  | UNIT     |  |

| Clock Period                                                                                | TCYC   | 1     | 20  | .5   | 10   | 0.33  | 10   | μS       |  |

| Rise & Fall Times                                                                           | TR, TF |       | 25  | -    | 25   | _     | 25   | nS       |  |

| Clock Pulse Width                                                                           | тс     | .470  | 10  | .235 | 5    | 0.160 | 5    | μS       |  |

| R/W valid before positive transition of<br>clock                                            | TWCW   | 180   | _   | 90   | _    | 60    |      | nS       |  |

| Address valid before positive transition<br>of clock                                        | TACW   | 180   | _   | 90   | -    | 60    | -    | nS       |  |

| Data Bus valid before negative transition of clock                                          | TDCW   | 300   | _   | 150  | _    | 100   | -    | nS       |  |

| Data Bus Hold Time                                                                          | THW    | 10    | _   | 10   | _    | 10    | _    | nS       |  |

| Peripheral data valid after negative<br>transition of clock                                 | TCPW   | -     | 1   | _    | .500 | _     | .333 | μS       |  |

| Peripheral data valid after negative<br>transition of clock driving CMOS<br>(Level=VCC-30%) | тсмоз  | —     | 2   | _    | 1    | -     | .666 | ہ<br>Suر |  |

# WRITE TIMING CHARACTERISTICS

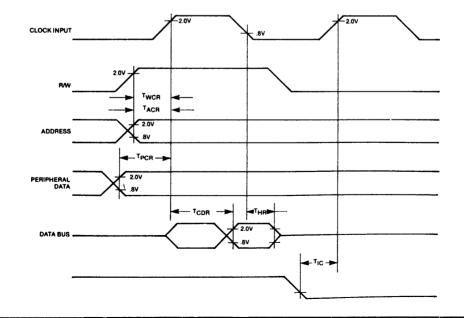

# **READ TIMING CHARACTERISTICS**

|                                                              |        | 1 MHz |     | 2MHz |     | 3MHz |     |      |

|--------------------------------------------------------------|--------|-------|-----|------|-----|------|-----|------|

| CHARACTERISTIC                                               | SYMBOL | MIN   | МАХ | MIN  | мах | MIN  | МАХ | UNIT |

| R/W valid before positive transition of<br>clock             | TWCR   | 180   | _   | 90   | _   | 60   | _   | nS   |

| Address valid before positive transition<br>of clock         | TACR   | 180   | _   | 90   | _   | 60   | _   | nS   |

| Peripheral data valid before positive<br>transition of clock | TPCR   | 300   | _   | 150  | _   | 100  | _   | nS   |

| Data Bus valid after positive transition<br>of clock         | TCDR   | _     | 400 | _    | 200 | _    | 135 | nS   |

| Data Bus Hold Time                                           | THR    | 10    | _   | 10   | -   | 10   | —   | nS   |

| IRQ valid before positive transition of<br>clock             | TIC    | 200   | _   | 100  | _   | 75   | _   | nS   |

Loading = 30 pf + 1 TTL load

PERIPHERALS

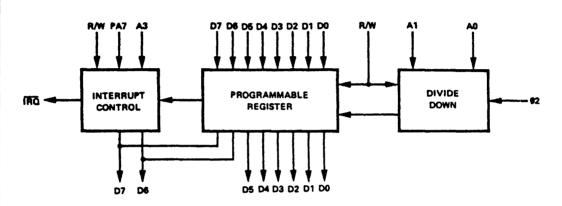

## INTERNAL ORGANIZATION

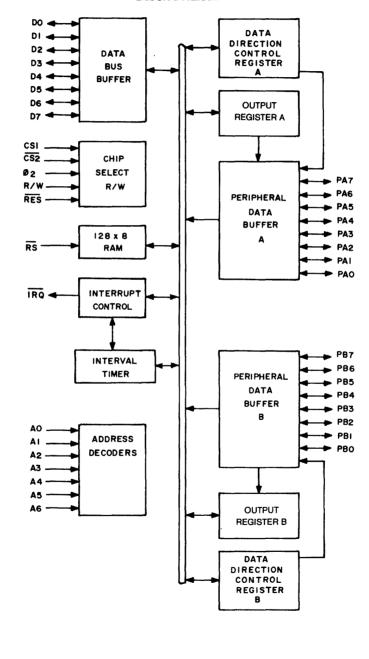

A block diagram of the internal architecture is shown in Figure 1. The 6532 is divided into four basic sections, RAM, I/O, TIMER, and Interrupt Control. The RAM interfaces directly with the microprocessor through the system data bus and address lines. The I/O section consists of two 8-bit halves. Each half contains a Data Direction Register (DDR) and an I/O Register.

#### RAM-128 Bytes (1024 Bits)

The 128 x 8 Read/Write memory acts as a conventional static RAM. Data can be written into the RAM from the microprocessor by selecting the chip (CS1 = 1, CS2 = 0) and by setting RS to a logic 0 (0.4v). Address lines A0 through A6 are then used to select the desired byte of storage.

## Internal Peripheral Registers

The Peripheral A I/O port consists of eight lines which can be individually programmed to act as either an input or an output. A logic zero in a bit of the Data Direction Register (DDRA) causes the corresponding line of the PA port to act as an input. A logic one causes the corresponding PA line to act as an output. The voltage on any line programmed to be an output is determined by the corresponding bit in the Output Register (ORA).

Data is read directly from the PA pins during any read operation. For any output pin, the data transferred into the processor will be the same as that contained in the Output Register if the voltage on the pin is allowed to go to 2.4v for a logic one. Note that for input lines, the processor can write into the corresponding bit of the Output Register. This will not affect the polarity on the pin until the corresponding bit of DDRA is set to a logic one to allow the peripheral pin to act as an output.

In addition to acting as a peripheral I/O line, the PA7 line can be used as an edge-detecting input. In this mode, an active transition will set the internal interrupt flag (bit 6 of the Interrupt Flag register). Setting the interrupt flag will cause IRQ output to go low if the PA7 interrupt has been enabled. The PA7 line should be set up as an input for this mode.

Control of the PA7 edge detecting mode is accomplished by writing to one of four addresses. In this operation, A0 controls the polarity of the active transition and A1 acts to enable or disable interrupting of the processor. The data which is placed on the Data Bus during this operation is discarded and has no effect on the control of PA7.

Setting of the PA7 interrupt flag will occur on an active transition even if the pin is being used as a normal input or as a peripheral control output. The flag will also be set by an active transition if interrupting from PA7 is disabled. The reset signal ( $\overline{RES}$ ) will disable the PA7 interrupt and will set the active transition to negative (high to low). During the system initialization routine, it is possible to set the interrupt flag by a negative transition. It may also be set by changing the polarity of the active interrupt. It is therefore recommended that the interrupt flag be cleared before enabling interrupting from PA7.

Clearing of the PA7 Interrupt Flag occurs when the microprocessor reads the Interrupt Flag Register.

The operation of the Peripheral B Input/Output port is exactly the same as the normal I/O operation of the Peripheral A port. The eight lines can each be programmed to act as either an input or as an output by placing a 0 or a 1 into the Data Direction register (DDRB). In the output mode, the voltage on a peripheral pin is controlled by the Output Register (ORB).

The primary difference between the PA and the PB ports is in the operation of the output buffers which drive these pins. The buffers are push-pull devices which are capable of sourcing 3 ma at 1.5v. This allows these pins to directly drive transistor switches. To assure that the microprocessor will read proper data on a "Read PB" operation, sufficient logic is provided in the chip to allow the microprocessor to read the Output Register instead of reading the peripheral pin as on the PA port.

#### INTERFACE SIGNAL DESCRIPTION

#### **Reset (RES)**

During system initialization a logic "0" on the RES input will cause a zeroing of all four I/O registers. This in turn will cause all I/O buses to act as inputs thus protecting external components from possible damage and erroneous data while the system is being configured under software control. The Data Bus Buffers are put into an OFF-STATE during Reset. Interrupt capability is disabled with the RES signal. The RES signal must be held low for at least one clock period when reset is required.

#### **Input Clock**

The input clock is a system Phase Two clock which can be either a low level clock ( $V_{IL} < 0.4$ ,  $V_{IL} > 2.4$ ) or high level clock ( $V_{IL} < 0.2$ ,  $V_{IH} = Vcc \pm \frac{3}{2}$ )

#### Read/Write (R/W)

The RW signal is supplied by the microprocessor array and is used to control the transfer of data to and from the microprocessor array and the 6532. A high on the RW pin allows the processor to read (with proper addressing) the data supplied by the 6532. A low on the RW pin allows a write (with proper addressing) to the 6532.

#### Interrupt Request (IRQ)

The IRQ pin is an interrupt pin from the interrupt control logic. The pin will be normally high with a low indicating an interrupt from the 6532. An external pull-up device is required. The IRQ pin may be activated by a transition on PA7 or timeout of the interval timer.

## Data Bus (D0-D7)

The 6532 has eight bi-directional data pins (D0-D7). These pins connect to the system's data lines and allow transfer of data to and from the microprocessor array. The output buffers remain in the off state except when a Read operation occurs and are capable of driving one standard TTL load and 130 pf.

## **Peripheral Data Ports**

The 6532 has 16 pins available for peripheral I/O operations. Each pin is individually software programmable to act as either an input or an output. The 16 pins are divided into 2 8-bit ports, PAO-PA7 and PBO-PB7. PA7 also has other uses which are discussed in later sections. The pins are set as inputs by writing a "0" into the corresponding bit of the data direction register. A "1" into the data direction register will cause the corresponding pin to be an output. When in the input mode, the peripheral output buffers are in the "1" state and pull-up device acts as less than one TTL load to the peripheral data lines. On a Read operation, the microprocessor unit reads the peripheral pin. When the peripheral device gets information from the 6532 it receives data stored in the data register. The microprocessor will read correct information if the peripheral lines are greater than 2.0 volts for a "1" and less than 0.8 volts for a "0" as the peripheral pins are all TTL compatible. Pins PBO-PB7 are also capable of sourcing 3 ma at 1.5v, thus making them capable of Darlington drive.

#### Address Lines (AO-A6)

There are 7 address pins. In addition to these 7, there is a RAM SELECT pin. These pins, A0-A6 and RAM SELECT, are always used as addressing pins. There are two additional pins which are used as CHIP SELECTS. They are pins CS1 and CS2.

## Interval Timer

The Timer section of the 6532 contains three basic parts: preliminary divide down register, programmable 8-bit register and interrupt logic.

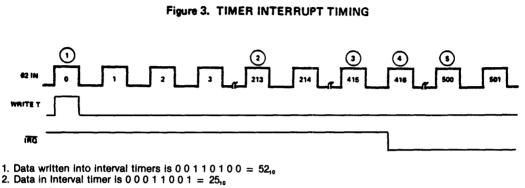

The interval time can be programmed to count up to 255 time intervals. Each time interval can be either 17, 87, 64T or 1024T increments, where T is the system clock period. When a full count is reached, an interrupt flag is set to a logic "1". After the interrupt flag is set the internal clock begins counting down to a maximum of – 255T. Thus, after the interrupt flag is set, a Read of the timer will tell how long since the flag was set up to a maximum of 255T.

The 8 bit system Data Bus is used to transfer data to and from the Interval Timer. If a count of 52 time intervals were to be counted, the pattern 0 0 1 1 0 1 0 0 would be put on the Data Bus and written into the Interval Time register.

At the same time that data is being written to the Interval Timer, the counting intervals of 1, 8, 64, 1024T are decoded from address lines A0 and A1. During a Read or Write operation address line A3 controls the interrupt capability; i.e.,  $A_3 = 1$  enables IRQ,  $A_3 = 0$  disables IRQ. When the timer is read prior to the interrupt flag being set, the number of time intervals remaining will be read, i.e., 51, 50, 49, etc.

When the timer has counted thru 0000000 on the next count time an interrupt will occur and the counter will read 1111111. After interrupt, the timer register decrements at a divide by "1" rate of the system clock. If after interrupt, the timer is read and a value of 11100100 is read, the time since interrupt is 27T. The value read is in two's complement, but remember that interrupt occurred on count number. Therefore, we must subtract 1.

Value read = 11100100

Complement = 00011011

ADD 1 = 0 0 0 1 1 1 0 0 = 28 Equals two's complement of register

SUB 1 = 00011011 = 27

Thus, to arrive at the total elapsed time, merely do a two's complement add to the original time written into the timer. Again, assume time written as 00110100 (= 52). With a divide by 8, total time to interrupt is  $(52 \times 8) + 1 = 417T$ . Total elapsed time would be 416T + 28T = 444T, assuming the value read after interrupt was 11100100.

After the interrupt, whenever the timer is written or read the interrupt is reset. However, the reading of the timer at the same time the interrupt occurs will not reset the interrupt flag. When the interrupt flags are read (DB7 for the timer, DB6 for edge detect) data bus lines D0-D5 go to 0.

- 4. interrupt has occurred at 02 pulse #416 Data in Interval timer = 1 1 1 1 1 1 1 1

- 5. Data in Interval timer is 1 0 1 0 1 1 0 0 two's complement is 0 1 0 1 0 1 0 0 = 84<sub>10</sub> 84 + (52x8) = 500<sub>10</sub>

When reading the timer after an interrupt, A3 should be low so as to disable the IRQ pin. This is done so as to avoid future interrupts until after another Write operation.

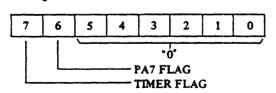

## Interrupt Flag Register

The Interrupt Flag Register consists of two bits: the timer interrupt flag and the PA7 interrupt flag. When a read operation is performed on the Interrupt Flag Register, the bits are transferred to the processor on the data bus, as the diagram below, indicates.

Figure 4. INTERRUPT FLAG REGISTER

The PA7 flag is cleared when the Interrupt Flag Register is read. The timer flag is cleared when the timer register is either written or read.

# ADDRESSING

Addessing of the 6532 is accomplished by the 7 addressing pins, the RS pin and the two chip select pins CS1 and CS2. To address the RAM, CS1 must be high with CS2 and RS low. To address the I/O and Interval timer CS1 and RS must be high with CS2 low. As can be seen to access the chip CS1 is high and CS2 is low. To distinguish between RAM or I/O Timer the RS pin is used. When this pin is low the RAM is addressed, when high the I/O Interval timer section is addressed. To distinguish between timer and I/O address line A2 is utilized. When A2 is high the Interval timer is accessed. When A2 is low the I/O section is addressed. Table 1 illustrates the chip addressing.

# Edge Sense Interrupt

In addition to its use as a peripheral I/O line, the PA7 pin can function as an edge sensitive input. In this mode, an active transition on PA7 will set the internal interrupt flag (bit 6 of the Interrupt Flag Register). When this occurs, and providing the PA7 interrupt is enabled, the IRQ output will go low.

Control of the PA7 edge detecting logic is accomplished by performing a write operation for one of four addresses. The data lines for this operation are "don't care" and the addresses to be used are found in Figure 4.

The setting of the internal interrupt flag by an active transition on PA7 is always enabled, no matter whether PA7 is set up as an input or an output.

The RES signal disables the PA7 interrupt and sets the active transition to the negative edge-detect state. During the reset operation, the interrupt flag may be set by a negative transition. It may, therefore, be necessary to clear the flag before its normal use as an edge detecting input is enabled. This can be achieved by reading the Interrupt Flag Register, as defined by Figure 4 immediately after reset.

# VO Register-Timer Addressing

Table 1 illustrates the address decoding for the internal elements and timer programming. Address line A2 distinguishes I/O registers from the timer. When A2 is low and RS is high, the I/O registers are addressed. Once the I/O registers are addressed, address lines A1 and A0 decode the desired register.

When the timer is selected A1 and A0 decode the "divide-by" matrix. This decoding is defined in Table 1. In addition, Address A3 is used to enable the interrupt flag to IRQ.

| OPERATION                 | RS  | R/W | A4  | A3  | A2 | A1  | A0  |

|---------------------------|-----|-----|-----|-----|----|-----|-----|

| Write RAM                 | 0   | 0   | -   |     | _  | -   | _   |

| Read RAM                  | 0   | 1   | - 1 | - 1 | -  | -   |     |

| Write DDRA                | 1   | 0   | i – |     | 0  | 0   | 1   |

| Read DDRA                 | 1 1 | 1   | _   | - 1 | 0  | 0   | 1   |

| Write DDRB                | 1 1 | 0   | -   | -   | 0  | 1   | 1 1 |

| Read DDRB                 | 1   | 1   | -   | _   | 0  | 1   | 1   |

| Write Output Reg A        | 1 1 | 0   | - 1 | i   | 0  | 0   | 0   |

| Read Output Reg A         | 1   | 1   | i – | _   | 0  | 0   | 0   |

| Write Output Reg B        | 1 1 | 0   | -   | -   | 0  | 1   | 0   |

| Read Output Reg B         | 1   | 1   | l – | - 1 | 0  | 1   | 0   |

| Write Timer               | 1   |     |     |     |    |     |     |

| + 1T                      | 1 1 | 0   | 1   | (a) | 1  | 0   | 0   |

| + 8T                      | 1   | 0   | 1   | (a) | 1  | 0   | 1   |

| + 64T                     | 1 1 | 0   | 1   | (a) | 1  | 1   | 0   |

| + 1024T                   | 1   | 0   | 1   | (a) | 1  | 1   | 1   |

| Read Timer                | 1   | 1   | J _ | (8) | 1  | _   | 0   |

| Read Interrupt Flag(s)    | 1   | 1   | I – |     | 1  |     | 1   |

| Write Edge Detect Control | 1 1 | 0   | l o |     | 1  | (b) | (C) |

## Table 1: ADDRESSING DECODE

NOTES:-- = Don't Care, "1" = High level (>2.4V), "0" = Low level (< 0.4V)

(a) A3 = 0 to disable interrupt from timer to  $\overline{IRG}$ A3 = 1 to enable interrupt from timer to  $\overline{IRG}$ (b) A1 = 0 to disable interrupt from PA7 to  $\overline{IRG}$ A1 = 1 to enable interrupt from PA7 to  $\overline{IRG}$ (c) A0 = 0 for negative adge-detect A0 = 1 for positive adge-detect

COMMODQRE SEMICONDUCTOR GROUP reserves the right to make changes to any products herein to improve reliability, function or design. COMMODORE SEMICONDUCTOR GROUP does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others.