# 68HC805K3

# **General Release Specification**

April 19, 1996

CSIC System Design Group Austin, Texas

# **List of Sections**

| Table of Contents                        | 5 |

|------------------------------------------|---|

| List of Figures1                         | 1 |

| List of Tables1                          | 3 |

| Section 1. General Description1          | 5 |

| Section 2. Memory Map2                   | 7 |

| Section 3. Central Processing Unit Core3 | 5 |

| Section 4. Interrupts3                   | 9 |

| Section 5. Resets49                      | 9 |

| Section 6. Operational Modes5            | 3 |

| Section 7. Parallel Input/Output5        | 9 |

| Section 8. 8-Bit Timer7                  | 1 |

| Section 9. Personality EEPROM79          | 9 |

| Section 10. User Program EEPROM8         | 9 |

| Section 11. Instruction Set9             | 1 |

| Section 12. Electrical Specifications109 | 9 |

| Section 13. Mechnical Specifications11   | 5 |

| Section 14. Ordering Information11       | 7 |

# **Table of Contents**

# **Section 1. General Description**

| 1.1     | Contents                               |

|---------|----------------------------------------|

| 1.2     | Introduction                           |

| 1.3     | Features                               |

| 1.4     | Mask Option Register                   |

| 1.5     | Pin Assignments18                      |

| 1.6     | MCU Structure                          |

| 1.7     | Functional Pin Description             |

| 1.7.1   | V <sub>DD</sub> and V <sub>SS</sub> 20 |

| 1.7.2   | OSC1 and OSC220                        |

| 1.7.2.  | 1 2-Pin Crystal Oscillator             |

| 1.7.2.  | ·                                      |

| 1.7.2.3 | 2-Pin RC Oscillators22                 |

| 1.7.2.4 | 4 3-Pin RC Oscillator                  |

| 1.7.2.  | 5 External Clock                       |

| 1.7.3   | Reset (RESET)                          |

| 1.7.4   | Maskable Interrupt Request (IRQ)24     |

| 1.7.5   | PA0 through PA7                        |

| 1.7.6   | PB0                                    |

| 1.7.7   | PB1/OSC3                               |

|         | Section 2. Memory Map                  |

|         | •                                      |

| 2.1     | Contents                               |

| 2.2     | Introduction                           |

| 2.3     | I/O and Control Registers              |

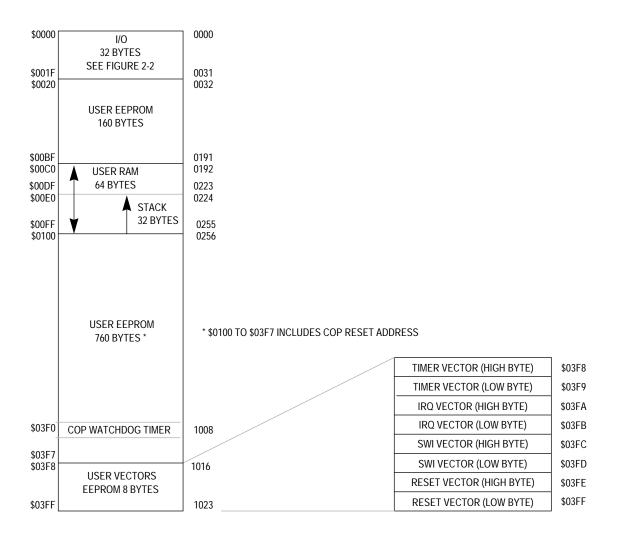

2.4

# **General Release Specification**

| 2.5   | User Electronically Erasable Programmable Read-Only Memory |

|-------|------------------------------------------------------------|

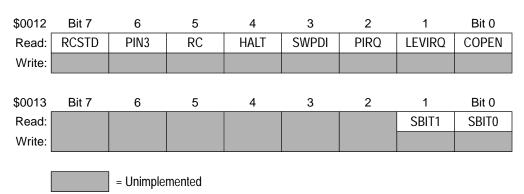

| 2.6   | Mask Option Registers (MOR) \$0012 and \$001332            |

|       |                                                            |

|       | Section 3. Central Processing Unit Core                    |

| 3.1   | Contents                                                   |

| 3.2   | Introduction                                               |

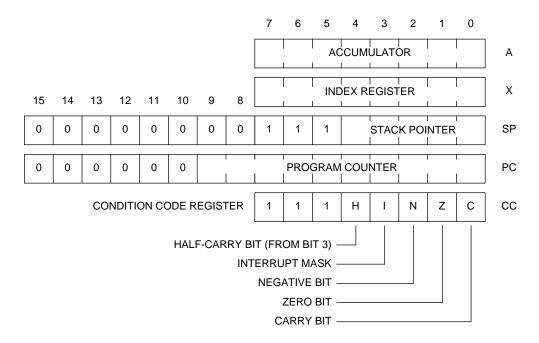

| 3.3   | Registers36                                                |

| 3.3.1 | Stack Pointer (SP)                                         |

| 3.3.2 | Program Counter (PC)37                                     |

|       |                                                            |

|       | Section 4. Interrupts                                      |

| 4.1   | Contents                                                   |

| 4.2   | Introduction                                               |

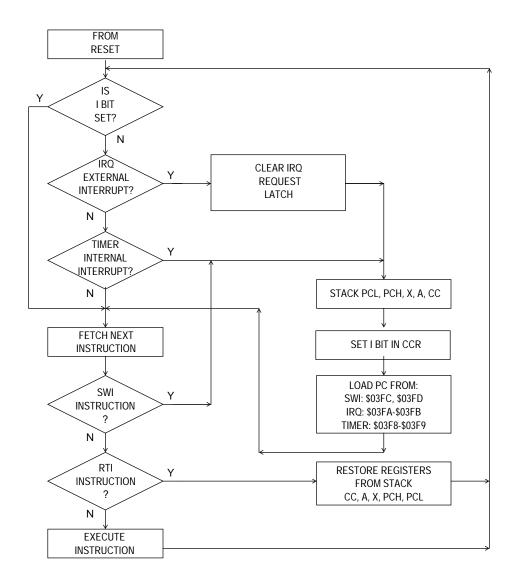

| 4.3   | CPU Interrupt Processing40                                 |

| 4.4   | Reset Interrupt Sequence42                                 |

| 4.5   | Software Interrupt (SWI)42                                 |

| 4.6   | Hardware Interrupts                                        |

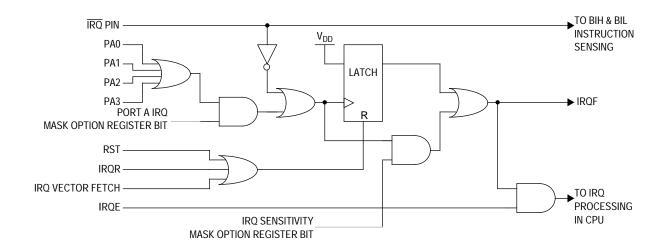

| 4.6.1 | External Interrupt (IRQ)43                                 |

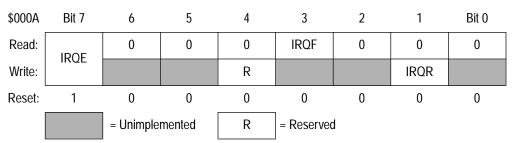

| 4.6.2 | IRQ Status/Control Register (ISCR)                         |

| 4.6.3 | Port Interrupts (PA0–PA3)                                  |

| 4.6.4 | Timer Interrupt (TIMER)                                    |

|       |                                                            |

|       | Section 5. Resets                                          |

| 5.1   | Contents                                                   |

| 5.2   | Introduction                                               |

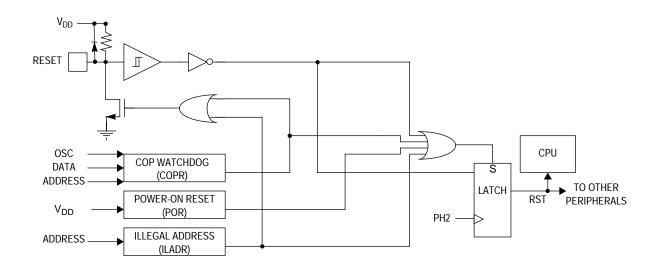

| 5.3   | External Reset (RESET)50                                   |

| 5.4   | Internal Resets                                            |

| 5.4.1 | Power-On Reset (POR)50                                     |

| 5.4.2 | Computer Operating Properly Reset (COPR)51                 |

| 5.4.3 | Illegal Address Reset (ILADR)51                            |

MC68HC805K3 — Rev. 1.0

General Release Specification

# **Section 6. Operational Modes**

|       | •                                 |

|-------|-----------------------------------|

| 6.1   | Contents                          |

| 6.2   | Introduction                      |

| 6.3   | Low-Power Modes                   |

| 6.3.1 | Stop Mode53                       |

| 6.3.2 | Halt Mode                         |

| 6.3.3 | Wait Mode                         |

| 6.3.4 | COP Watchdog Timer Considerations |

|       | Section 7. Parallel Input/Output  |

| 7.1   | Contents                          |

| 7.2   | Introduction                      |

| 7.3   | Port A                            |

| 7.3.1 | Port A Data Register              |

| 7.3.2 | Port A Data Direction Register    |

| 7.3.3 | Port A Pulldown Inhibit Register  |

| 7.3.4 | Port A LED Drive Capability       |

| 7.3.5 | Port A I/O Pin Interrupts         |

| 7.4   | Port B                            |

| 7.4.1 | Port B Data Register              |

| 7.4.2 | Port B Data Direction Register    |

| 7.4.3 | Port B Pulldown Inhibit Register  |

| 7.4.4 | Port B with 3-Pin RC Oscillator   |

| 7.5   | I/O Port Programming66            |

| 7.5.1 | Pin Data Direction                |

| 7.5.2 | Output Pin                        |

| 7.5.3 | Input Pin                         |

| 7.5.4 | I/O Pin Transitions               |

| 755   | I/O Pin Truth Tables 68           |

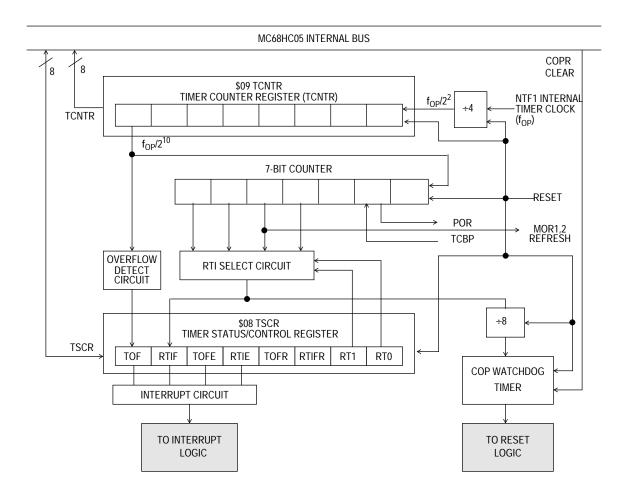

# Section 8. 8-Bit Timer

**General Release Specification**

| Contents                                    |

|---------------------------------------------|

| Introduction71                              |

| Timer Registers                             |

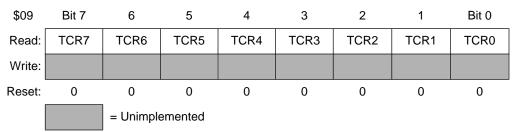

| Timer Counter Register (TCNTR) \$0973       |

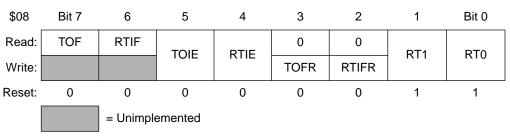

| Timer Status/Control Register (TSCR) \$0874 |

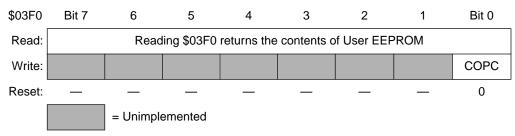

| COP Watchdog Timer76                        |

| Operating During Stop Mode                  |

| Operating During Wait Mode77                |

| Section 9. Personality EEPROM               |

| Contents                                    |

| Introduction                                |

| PEEPROM Registers                           |

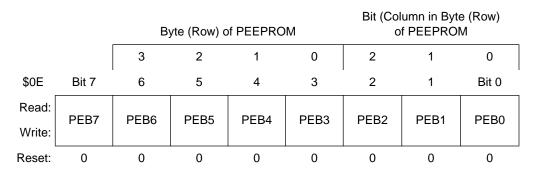

| PEEPROM Bit Select Register (PEBSR)         |

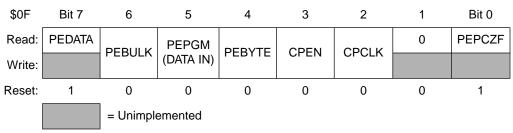

| PEEPROM Status/Control Register (PESCR)82   |

| PEEPROM Programming                         |

| PEEPROM Read Access                         |

| Section 10. User Program EEPROM             |

| Contents                                    |

| Introduction89                              |

| EEPROM Programming                          |

| EEPROM Security89                           |

|                                             |

## **Section 11. Instruction Set**

| 11.1   | Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11.2   | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 11.3   | Addressing Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 11.3.1 | Inherent                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 11.3.2 | Immediate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 11.3.3 | Direct93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 11.3.4 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 11.3.5 | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 11.3.6 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 11.3.7 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 11.3.8 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 11.4   | Instruction Types95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 11.4.1 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 11.4.2 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 11.4.3 | and the second s |

| 11.4.4 | The state of the s |

| 11.4.5 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 11.5   | Instruction Set Summary102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|        | Section 12. Electrical Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 12.2   | Maximum Ratings109                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 12.3   | Operating Range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 12.4   | Thermal Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 12.5   | 5.0 Volt DC Electrical Characteristics111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 12.6   | 3.0 Volt DC Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 12.7   | 5.0 Volt Control Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 12.8   | 3.0 Volt Control Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

# **General Release Specification**

|      | Section 13. Mechnical Specifications        |

|------|---------------------------------------------|

| 13.1 | Contents                                    |

| 13.2 | Introduction                                |

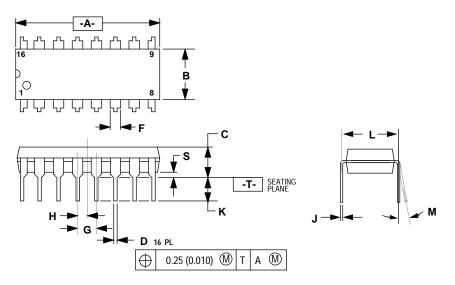

| 13.3 | Dual-In-Line Package (Case 648)116          |

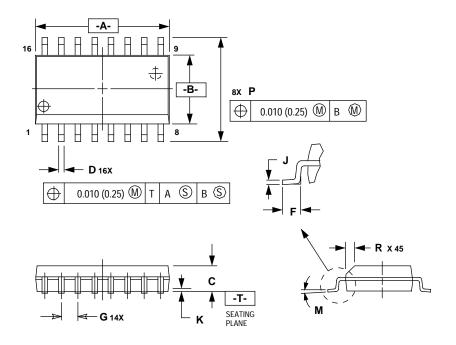

| 13.4 | Small Outline Integrated Circuit (Case 751) |

|      |                                             |

|      | Section 14. Ordering Information            |

| 14.1 | Contents                                    |

| 14.2 | Introduction                                |

| 14.3 | MC Order Numbers                            |

# **List of Figures**

| Figure | Title                                   | Page |

|--------|-----------------------------------------|------|

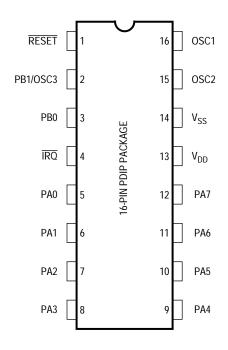

| 1-1    | MC68HC805K3 Pin Assignments             | 18   |

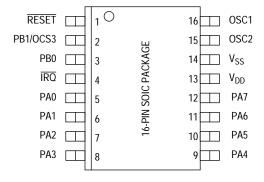

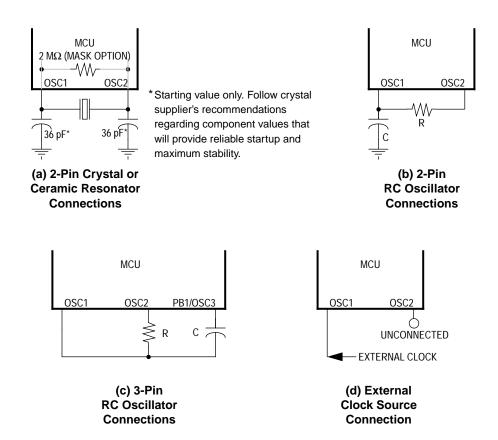

| 1-2    | MC68HC805K3 Block Diagram               |      |

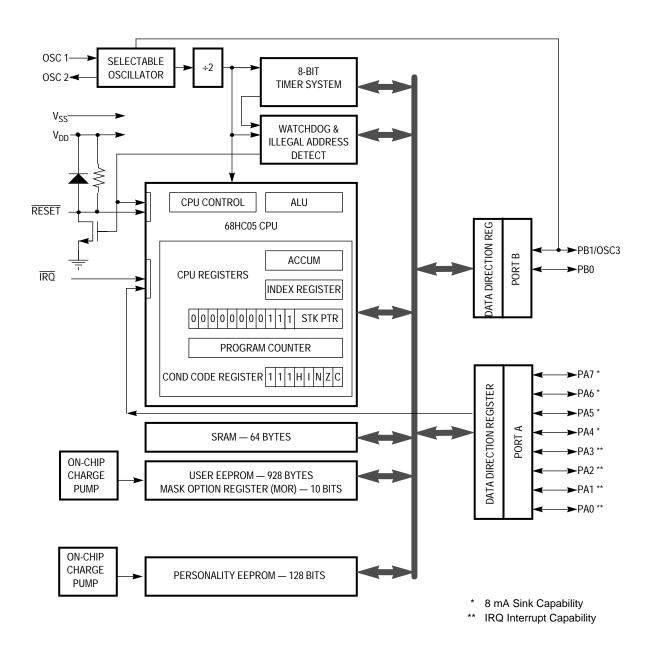

| 1-3    | Oscillator Connections                  |      |

| 2-1    | MC68HC805K3 Single-Chip Mode Memory Map | 28   |

| 2-2    | MC68HC805K3 I/O Registers Memory Map    | 29   |

| 2-3    | MC68HC805K3 I/O Registers \$0000-\$000F | 30   |

| 2-4    | MC68HC805K3 I/O Registers \$0010-\$001F | 31   |

| 2-5    | Mask Option Register                    |      |

| 3-1    | M68HC05 Programming Model               | 36   |

| 4-1    | Interrupt Processing Flowchart          | 41   |

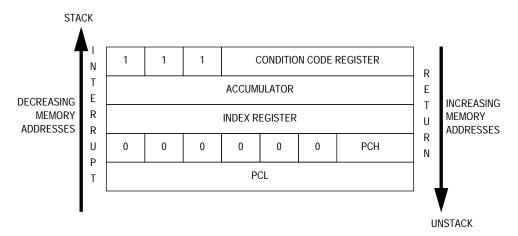

| 4-2    | Interrupt Stacking Order                |      |

| 4-3    | IRQ Function Block Diagram              |      |

| 4-4    | IRQ Status/Control Register             | 45   |

| 5-1    | Reset Block Diagram                     | 50   |

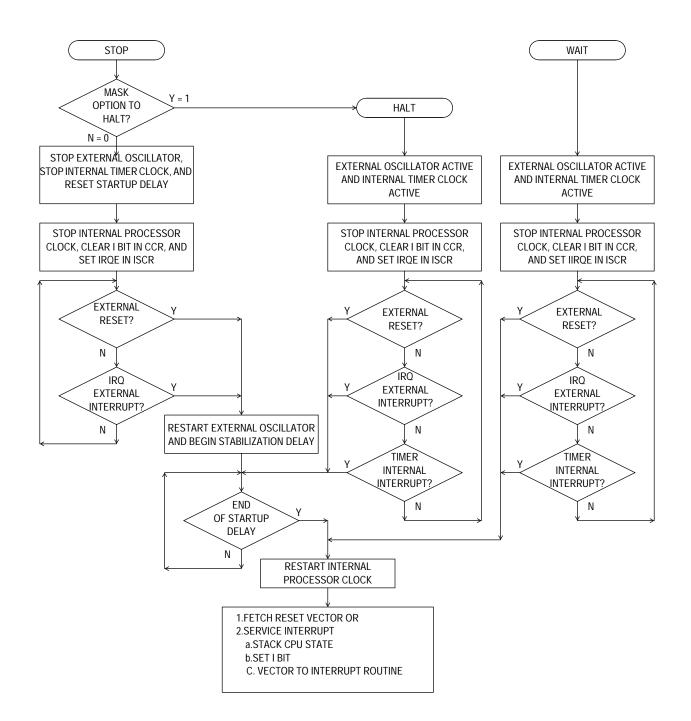

| 6-1    | Stop/Halt/Wait Flowcharts               | 55   |

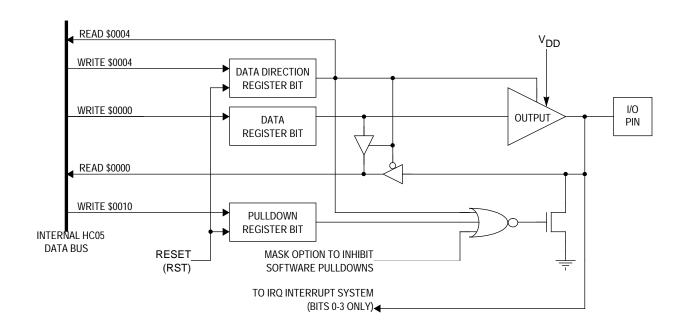

| 7-1    | Port A I/O Circuitry                    | 60   |

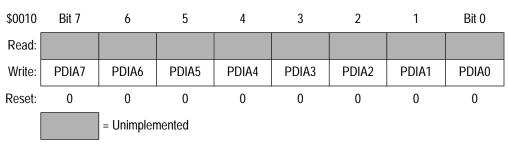

| 7-2    | Port A Pulldown Inhibit Register (PDRA) | 62   |

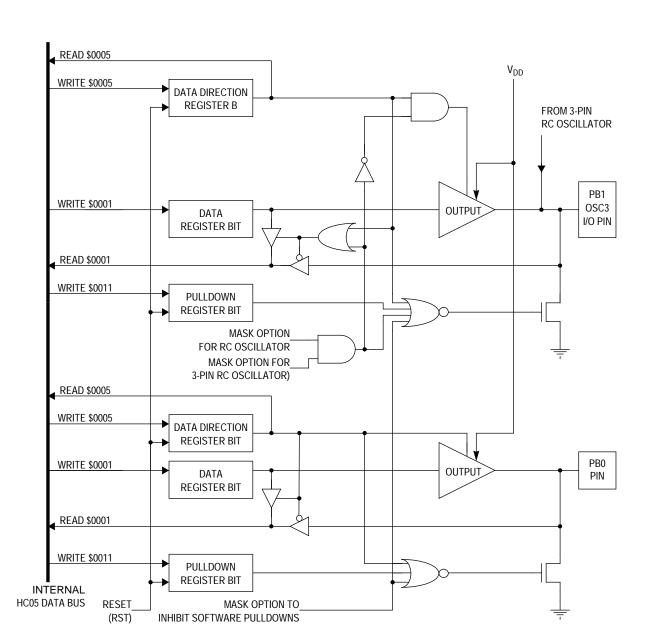

| 7-3    | Port B I/O Circuitry                    |      |

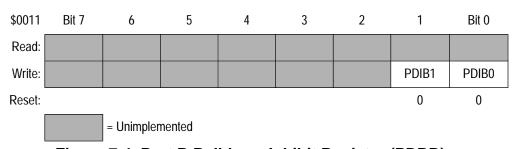

| 7-4    | Port B Pulldown Inhibit Register (PDRB) |      |

| 8-1    | Timer Block Diagram                     | 72   |

| 8-2    | Timer Counter Register                  | 73   |

| 8-3    | Timer Status/Control Register           |      |

| 8-4    | COPR Watchdog Timer Location            | 76   |

# **General Release Specification**

www.DataSheet4U.com

| Figure | Title                            | Page |

|--------|----------------------------------|------|

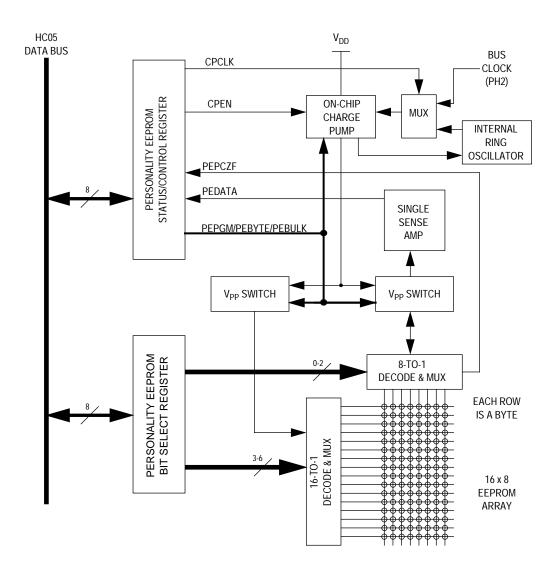

| 9-1    | Personality EEPROM Block Diagram | 80   |

| 9-2    | PEBSR Select Register            | 81   |

| 9-3    | PESCR Status/Control Register    | 82   |

# **List of Tables**

| Table | Title                                     | Page |

|-------|-------------------------------------------|------|

| 4-1   | Vector Addresses for Interrupts and Reset | 40   |

| 7-1   | Port A Pin Functions                      | 68   |

| 7-2   | PB0 Pin Functions                         | 68   |

| 7-3   | PB1/OSC3 Pin Functions                    | 69   |

| 8-1   | RTI Rates and COP Reset Times             | 75   |

| 9-1   | Software to Read PEEPROM                  | 83   |

| 11-1  | Register/Memory Instructions              | 96   |

| 11-2  | Read-Modify-Write Instructions            | 97   |

| 11-3  | Jump and Branch Instructions              | 99   |

| 11-4  | Bit Manipulation Instructions             | 100  |

| 11-5  | Control Instructions                      |      |

| 11-6  | Instruction Set Summary                   | 102  |

| 11-7  | Opcode Map                                | 108  |

# Section 1. General Description

#### 1.1 Contents

| 1.2     | Introduction                           |

|---------|----------------------------------------|

| 1.3     | Features                               |

| 1.4     | Mask Option Register                   |

| 1.5     | Pin Assignments                        |

| 1.6     | MCU Structure                          |

| 1.7     | Functional Pin Description             |

| 1.7.1   | V <sub>DD</sub> and V <sub>SS</sub>    |

| 1.7.2   | OSC1 and OSC220                        |

| 1.7.2.  | 1 2-Pin Crystal Oscillator             |

| 1.7.2.2 | 2 2-Pin Ceramic Resonator Oscillator22 |

| 1.7.2.3 | 3 2-Pin RC Oscillators                 |

| 1.7.2.4 | 4 3-Pin RC Oscillator23                |

| 1.7.2.5 | 5 External Clock                       |

| 1.7.3   | Reset (RESET)                          |

| 1.7.4   | Maskable Interrupt Request (IRQ)24     |

| 1.7.5   | PA0 through PA725                      |

| 1.7.6   | PB0                                    |

| 1.7.7   | PB1/OSC3                               |

#### 1.2 Introduction

The low-cost MC68HC805K3 microcontroller is a member of the M68HC805 Family of microprocessors. This device has 64 bytes of user RAM, 128 bits of personality electronically erasable programmable ROM (PEEPROM), and 928 bytes of user EEPROM. This device is available in the 16-pin plastic dual in-line package (PDIP) and 16-pin small outline integrated circuit (SOIC) package. A functional block diagram of the MC68HC805K3 is shown in **Figure 1-2**.

**Features**

#### 1.3 Features

- Low-Cost HC05 Core

- 16-Pin PDIP or SOIC Package

- 928 Bytes of User EEPROM (Including Eight Bytes of User Vectors)

- 64 Bytes of User RAM

- 128 Bits of Personality EEPROM (Not Memory Mapped)

Programmed using User Software or during User EEPROM

Programming

- On-Chip Charge Pump for In-Circuit Programming of the Personality EEPROM at 3.0 to 5.5 Vdc.

- 8-Bit Free-Running Timer

- 4-Stage Selectable Real-Time Interrupt Generator

- 10 Bidirectional Input/Output (I/O) Lines Including:

- 8 mA Sink Capability on Four I/O Pins (PA7–PA4)

- Mask Option Register Bit for Software Programmable Pulldowns on All I/O Pins

- Mask Option Register Bit for Port Interrupts on Four I/O Pins (PA3–PA0) (Keyboard Scan Feature)

- IRQ Interrupt Hardware Mask, Flag Bit, and Request Bit

- Mask Option Register Bit for Sensitivity on IRQ Interrupt (Edgeand Level-Sensitive or Edge-Sensitive Only)

- On-Chip Oscillator (Mask Option Register Bits for Crystal/Ceramic Resonator Oscillator with Internal 2 MΩ Resistor, and 2-Pin or 3-Pin Resistor Capacitor (RC) Oscillator)

- Mask Option Register Bit for Reduced Startup Delay Time with RC Oscillator Options

- Mask Option Register Bit for Computer Operating Properly (COP) Watchdog System

- Power-Saving Stop and Wait Mode Instructions

MC68HC805K3 — Rev. 1.0

General Release Specification

Mask Option Register

- Mask Option Register Bit to Convert STOP Instruction to Halt Mode

- Illegal Address Reset

- Internal Steering Diode and Pullup Resistor on RESET Pin to V<sub>DD</sub>

- Internal RESET Pin Pulldown from COP Watchdog and ILADR

**NOTE:** A line over a signal name indicates an active low signal. For example, RESET is active high and RESET is active low.

Any reference to voltage, current, or frequency specified in the following sections refers to the nominal values. The exact values and their tolerance or limits are specified in **Section 12. Electrical Specifications**.

## 1.4 Mask Option Register

The MC68HC805K3 contains these nine programmable options:

- COP Watchdog Timer (Enable or Disable)

- 2. IRQ Triggering (Edge-Sensitive or Edge- and Level-Sensitive)

- 3. Port A Interrupts (Enable or Disable)

- 4. Port Software Programmable Pulldowns (Enable or Disable)

- 5. STOP Instruction (Enable or Disable)

- Oscillator Type (Crystal/Ceramic Resonator or RC)

- RC Oscillator Type (2-Pin or 3-Pin)

- 8. RC Oscillator Startup Delay (4064 or 16 f<sub>OP</sub> Cycles)

- 9. User EEPROM and PEEP Security (Enable or Disable)

**NOTE:** The startup delay of 16  $f_{OP}$  cycles and the crystal/ceramic resonator oscillator should not be selected together.

# **Pin Assignments**

# 1.5 Pin Assignments

The MC68HC805K3 is available in 16-pin SOIC and PDIP packages. The pin assignments for these packages are shown in Figure 1-1.

Figure 1-1. MC68HC805K3 Pin Assignments

General Release Specification MCU Structure

#### 1.6 MCU Structure

The overall block diagram of the MC68HC805K3 is shown in Figure 1-2.

Figure 1-2. MC68HC805K3 Block Diagram

# **Functional Pin Description**

## 1.7 Functional Pin Description

The following paragraphs give a description of the general function of each pin.

## 1.7.1 $V_{DD}$ and $V_{SS}$

Power is supplied to the MCU through V<sub>DD</sub> and V<sub>SS</sub>. V<sub>DD</sub> is the positive supply and V<sub>SS</sub> is ground. The MCU operates from a single power supply.

Rapid signal transitions occur on the MCU pins. The short rise and fall times place very high short-duration current demands on the power supply. To prevent noise problems, special care should be taken to provide good power supply bypassing at the MCU by using bypass capacitors with high-frequency characteristics that are positioned as close to the MCU as possible.

#### 1.7.2 OSC1 and OSC2

The OSC1 and OSC2 pins are the connections for the 2-pin on-chip oscillator. The OSC1 and OSC2 pins also can be used in conjunction with the PB1/OSC3 pin to create a more stable 3-pin RC oscillator. The OSC1, OSC2, and PB1/OSC3 pins can accept these sets of components:

- A crystal, as shown in Figure 1-3(a)

- 2. A ceramic resonator, as shown in Figure 1-3(a)

- 3. An external resistor and capacitor using two pins, as shown in **Figure 1-3(b)**

- 4. An external resistor and capacitor using three pins, as shown in **Figure 1-3(c)**

- 5. An external clock signal, as shown in Figure 1-3(d)

The frequency, f<sub>osc</sub>, of the oscillator or external clock source is divided by two to produce the internal operating frequency foo. The oscillator type is selected by two mask option register bits.

MC68HC805K3 — Rev. 1.0

General Release Specification Functional Pin Description

#### 1.7.2.1 2-Pin Crystal Oscillator

The circuit in **Figure 1-3(a)** shows a typical 2-pin oscillator circuit for an AT-cut, parallel resonant crystal. The crystal manufacturer's recommendations should be followed, since the crystal parameters determine the external component values required to provide maximum stability and reliable startup. The load capacitance values used in the oscillator circuit design should include all stray capacitances. The crystal and components should be mounted as close as possible to the pins for startup stabilization and to minimize output distortion. An internal startup resistor of approximately 2 M $\Omega$  is provided between OSC1 and OSC2 when the crystal/ceramic resonator oscillator option is used.

Figure 1-3. Oscillator Connections

#### 1.7.2.2 2-Pin Ceramic Resonator Oscillator

In cost-sensitive applications, a ceramic resonator can be used instead of the crystal. The circuit in **Figure 1-3(a)** is for a ceramic resonator also. The resonator manufacturer's recommendations should be followed, since the resonator parameters determine the external component values required for maximum stability and reliable starting. The load capacitance values used in the oscillator circuit design should include all stray capacitances. The ceramic resonator and components should be mounted as close as possible to the pins for startup stabilization and to minimize output distortion. An internal startup resistor of approximately 2 M $\Omega$  is provided between OSC1 and OSC2 for the crystal/ceramic resonator oscillator mask option register bit.

#### 1.7.2.3 2-Pin RC Oscillators

The 2-pin RC oscillator configuration can be used for very low-cost applications. With this option, a resistor must be connected between the two oscillator pins and a capacitor must be connected from the OSC1 pin to  $V_{SS}$ , as shown in **Figure 1-3(b)**. The signal on the OSC2 pin is a square wave and the signal on the OSC1 pin approximates a triangular wave.

The 2-pin RC oscillator is selected by programming bit 5 ("RC") of the mask option register located at \$0012. Bit 6 ("Pin 3") should NOT be programmed when using the 2-pin oscillator.

The 2-pin RC oscillator is optimized for operation at 500 kHz. This oscillator can be used at higher or lower frequencies with degraded accuracy over temperature, supply voltage, and/or device processing variations. The internal startup resistor of approximately 2 M $\Omega$  is **not** connected between OSC1 and OSC2 when the 2-pin RC oscillator mask option register bit is selected.

General Release Specification Functional Pin Description

#### 1.7.2.4 3-Pin RC Oscillator

Another low cost, but more accurate, type of RC oscillator is the 3-pin configuration utilizing the PB1/OSC3 pin. With this option, a resistor must be connected between the OSC1 and OSC2 pins and a capacitor must be connected between the OSC1 and PB1/OSC3 pins, as shown in **Figure 1-3(c)**. This 3-pin RC oscillator is more accurate than the 2-pin RC oscillator with respect to temperature, supply voltage, and/or device processing variations. The signal on the OSC2 and PB1/OSC3 pins is a square wave and the signal on the OSC1 pin approximates a triangular wave.

Selection of the 3-bit RC oscillator requires programming two bits in the mask option register located at \$0012. Bit 5 ("RC"), when programmed, enables the RC oscillator. Bit 6 ("Pin 3"), when programmed along with bit 5, selects the 3-pin oscillator configuration.

The 3-pin RC oscillator is optimized for operation at 500 kHz. This oscillator can be used at higher or lower frequencies with degraded accuracy over temperature, supply voltage, and/or device processing variations. The internal startup resistor of approximately 2 M $\Omega$  is **not** connected between OSC1 and OSC2 when the 3-pin RC oscillator mask option register bit is selected. The typical external components for a 500-kHz oscillator are a 20-k $\Omega$  resistor and a 25- to 30-pF capacitor.

#### **NOTE:**

Capacitors used with the RC oscillators should have minimal leakage. Electrolytic or tantalum capacitors should not be used because they degrade the temperature performance of the oscillator due to excessive variation in their leakage.

#### 1.7.2.5 External Clock

An external clock from another CMOS-compatible device can be connected to the OSC1 input, with the OSC2 input not connected, as shown in **Figure 1-3(d)**. This configuration is possible regardless of whether the oscillator is set up for crystal/ceramic resonator, 2-pin RC, or 3-pin RC operation. However, if the 3-pin RC oscillator is selected, the PB1/OSC3 pin also must be left unconnected.

### Functional Pin Description

## 1.7.3 Reset (RESET)

This pin can be used as an input to reset the MCU to a known startup state by pulling the pin to the low state. The  $\overline{RESET}$  pin contains a steering diode to discharge any voltage on the pin to  $V_{DD}$  when the power is removed. The  $\overline{RESET}$  pin contains an internal pullup resistor to  $V_{DD}$  of approximately 100 k $\Omega$  to allow the  $\overline{RESET}$  pin to be left unconnected for low-power applications. The  $\overline{RESET}$  pin contains an internal Schmitt trigger to improve its noise immunity as an input.

The RESET pin has an internal pulldown device that pulls the RESET pin low when there is an internal COP watchdog or an illegal address reset. Refer to **Section 5. Resets**.

## 1.7.4 Maskable Interrupt Request (IRQ)

The IRQ input pin drives the asynchronous IRQ interrupt function of the CPU. The IRQ interrupt function has a mask option register bit to select either negative edge-sensitive triggering or both negative edge-sensitive and low level-sensitive triggering. If the option is selected to include level-sensitive triggering, the  $\overline{IRQ}$  pin requires an external resistor to  $V_{DD}$  if "wired-OR" operation is desired. If the  $\overline{IRQ}$  pin is not used, it must be tied to the  $V_{DD}$  supply.

**NOTE:**

Each of the PA0 through PA3 I/O pins can be connected through an OR gate to the IRQ interrupt function by a common mask option. This capability allows keyboard scan applications where the transitions or levels on the I/O pins behave the same as the  $\overline{IRQ}$  pin, except that the logic level is inverted. The edge or level sensitivity selected by the mask option register bit for the  $\overline{IRQ}$  pin also applies to the I/O pins ORed to create an IRQ signal.

The IRQ pin contains an internal Schmitt trigger to improve noise immunity. For more details, see **Section 4. Interrupts**.

General Release Specification Functional Pin Description

#### 1.7.5 PA0 through PA7

These eight I/O lines comprise port A. The state of any pin is software programmable and all port A lines are configured as inputs during power-on or reset. The four upper-order I/O pins (PA4 through PA7) are capable of sinking higher currents. The four lower-order I/O pins (PA0 through PA3) can be connected via an internal OR gate to the IRQ interrupt function by a mask option register bit. All the port A pins can have software programmable pulldown devices provided by another mask option bit. See **Section 7. Parallel Input/Output** for more details on the I/O ports.

#### 1.7.6 PB0