14 A\* c

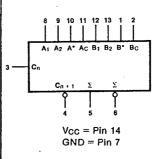

PINOUT A 14 Vcc Bc 2 13 B<sub>2</sub> 12 B<sub>1</sub> C<sub>2</sub> 3 11 Ac Cn+1 4 10 A\* Σ 5 Σ 6 9 A2 8 A1 GND 7

PINOUT B

Ac 1

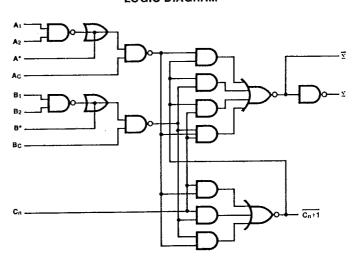

DESCRIPTION -- The '80 is a single-bit, high speed, binary full adder with gated complementary inputs, complementary sum ( $\Sigma$  and  $\overline{\Sigma}$ ) outputs and inverted carry output. It is designed for medium and high speed, multiplebit, parallel-add/serial carry applications. The circuit utilizes DTL for the gated inputs and high speed, high fan-out TTL for the sum and carry outputs. The circuit is entirely compatible with both DTL and TTL logic families. The implementation of a single-inversion, high speed, Darlingtion-connected serial-carry circuit minimizes the necessity for extensive "lookahead" and carry-cascading circuits.

13 A2 B<sub>1</sub> 2 12 Aı B<sub>2</sub> 3 11 GND Vcc 4 10 ∑ B\* 5 9 Σ Bc 6 8 Cn+1 Cn 7

**LOGIC SYMBOL**

## **ORDERING CODE:** See Section 9

|                    | PIN | COMMERCIAL GRADE                                                                         | COMMERCIAL GRADE MILITARY GRADE                                                                 |             |

|--------------------|-----|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-------------|

| PKGS               | оит | $V_{CC} = +5.0 \text{ V } \pm 5\%,$<br>$T_A = 0^{\circ}\text{C to } +70^{\circ}\text{C}$ | $V_{CC} = +5.0 \text{ V} \pm 10\%,$<br>$T_A = -55^{\circ} \text{ C to} + 125^{\circ} \text{ C}$ | PKG<br>TYPE |

| Plastic<br>DIP (P) | А   | 7480PC                                                                                   |                                                                                                 | 9A          |

| Ceramic<br>DIP (D) | Α   | 7480DC .                                                                                 | 5480DM                                                                                          | 6A          |

| Flatpak<br>(F)     | В   | 7480FC                                                                                   | 5480FM                                                                                          | 31          |

#### INPUT LOADING/FAN-OUT: See Section 3 for U.L. definitions

| PIN NAMES                                                         | 54/74 (U.L.)<br>HIGH/LOW |           |

|-------------------------------------------------------------------|--------------------------|-----------|

| A <sub>1</sub> , A <sub>2</sub> , B <sub>1</sub> , B <sub>2</sub> | Operand Inputs           | 0.4/1.0   |

| A*, B*                                                            | Inverted Operand Inputs  | -/1.63    |

| Ac, Bc                                                            | Control Inputs           | 0.4/1.0   |

| C <sub>n</sub><br>C <sub>n + 1</sub><br>Σ, Σ                      | Carry Input              | . 5.0/5.0 |

| Ōn + 1                                                            | Inverted Carry Output    | 5.0/5.0   |

| $\Sigma, \overline{\Sigma}$                                       | Sum Outputs              | 10/10     |

| A*, B*                                                            | When Used As Outputs     | 3.0/3.0   |

|                                                                   |                          |           |

|                                                                   |                          |           |

ww.DataSheet4U.cor

### TRUTH TABLE

|    | INPL | ITS | OUTPUTS |   |   |  |

|----|------|-----|---------|---|---|--|

| Cn | В    | Α   | Cn + 1  | Σ | Σ |  |

| L  | L    | L   | Н       | Н | L |  |

| L  | L    | Н   | н       | L | Н |  |

| L  | Н    | L   | Н       | L | Н |  |

| L  | Н    | Н   | L       | Н | L |  |

| н  | L    | L   | н       | L | Н |  |

| Н  | L    | Н   | L       | н | L |  |

| H  | Н    | L   | L       | Н | L |  |

| Н  | Н    | Н   | L       | L | Н |  |

#### NOTES:

- (1)  $A = \overline{A^* \bullet A_C}$ ,  $B = \overline{B^* \bullet B_C}$  where  $\overline{A_1 \bullet A_2}$ .  $B^* = \overline{B_1} \bullet \overline{B_2}$

- (2) When A' or B' are used as inputs, A<sub>1</sub> and A<sub>2</sub> or B<sub>1</sub> and B<sub>2</sub> respectively must be connected to Gnd.

- (3) When A<sub>1</sub> and A<sub>2</sub> or B<sub>1</sub> and B<sub>2</sub> are used as inputs, A\* or B\* respectively must be open or used to perform Dot-OR logic.

## LOGIC DIAGRAM

# DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unlsess otherwise specified)

| SYMBOL | PARAMETER                                               |          | 54/74        |              | UNITS | CONDITIONS            |

|--------|---------------------------------------------------------|----------|--------------|--------------|-------|-----------------------|

| SIMBUL | FARAMETER                                               | Min      | Max          | ]            |       |                       |

| los    | Output Short Circuit<br>Current at $\overline{C}_n$ + 1 | XM<br>XC | -20<br>-18   | -70<br>-70   | mA    | V <sub>CC</sub> = Max |

| los    | Output Short Circuit<br>Current at A*, B*               | XM<br>XC | -0.9<br>-0.9 | -2.9<br>-2.9 | mA    | V <sub>CC</sub> = Max |

| lcc    | Power Supply Current                                    | XM<br>XC |              | 31<br>35     | mA    | V <sub>CC</sub> = Max |

# AC CHARACTERISTICS: V<sub>CC</sub> = +5.0 V, T<sub>A</sub> = +25° C (See Section 3 for waveforms and load configurations)

| SYMBOL       |                                                                   | 54/74<br>C <sub>L</sub> = 15 pF |          | UNITS | CONDITIONS                                |

|--------------|-------------------------------------------------------------------|---------------------------------|----------|-------|-------------------------------------------|

|              | PARAMETER                                                         |                                 |          |       |                                           |

|              |                                                                   | Min                             | Max      |       |                                           |

| tplH<br>tpHL | Propagation Delay<br>C <sub>n</sub> to C <sub>n</sub> + 1         |                                 | 17<br>12 | ns    | Figs. 3-1, 3-4 $R_L = 780 \Omega$         |

| tPLH<br>tPHL | Propagation Delay<br>Bc to Cn + 1                                 |                                 | 25<br>55 | ns    | Figs. 3-1, 3-5 $R_L = 780 \ \Omega$       |

| tplH<br>tpHL | Propagation Delay<br>A <sub>C</sub> to Σ                          |                                 | 70<br>80 | ns    | Figs. 3-1, 3-4<br>R <sub>L</sub> = 400 Ω  |

| tPLH<br>tPHL | Propagation Delay<br>Bc to ∑                                      |                                 | 55<br>75 | ns    | Figs. 3-1, 3-5<br>R <sub>L</sub> = 400 Ω  |

| tplH<br>tpHL | Propagation Delay<br>A <sub>1</sub> to A* or B <sub>1</sub> to B* |                                 | 65<br>25 | ns    | Figs. 3-1, 3-4<br>R <sub>L</sub> not used |