# **Signetics**

#### **Logic Products**

#### **FEATURES**

- 8-bit transparent latch '373

- 8-bit positive, edge-triggered register — '374

- 3-State output buffers

- Common 3-State Output Enable

- Independent register and 3-State buffer operation

#### DESCRIPTION

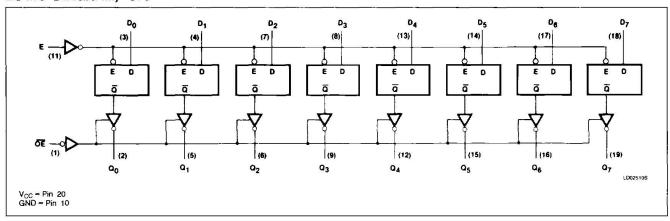

The '373 is an octal transparent latch coupled to eight 3-State output buffers. The two sections of the device are controlled independently by Latch Enable (E) and Output Enable ( $\overline{OE}$ ) control gates.

# 74LS373, 74LS374, S373, S374

# Latches/Flip-Flops

'373 Octal Transparent Latch With 3-State Outputs '374 Octal D Flip-Flop With 3-State Outputs Product Specification

| TYPE    | TYPICAL PROPAGATION DELAY | TYPICAL SUPPLY CURRENT (TOTAL) |

|---------|---------------------------|--------------------------------|

| 74LS373 | 19ns                      | 24mA                           |

| 74S373  | 10ns                      | 105mA                          |

| 74LS374 | 19ns                      | 27mA                           |

| 74S374  | 8ns                       | 116mA                          |

#### **ORDERING CODE**

| PACKAGES       | COMMERCIAL RANGE $V_{CC} = 5V \pm 5\%$ ; $T_A = 0^{\circ}C$ to $+70^{\circ}C$ |

|----------------|-------------------------------------------------------------------------------|

| Plastic DIP    | N74LS373N, N74S373N, N74LS374N, N74S374N                                      |

| Plastic SOL-20 | N74LS373D, N74S373D, N74LS374D, N74S374D                                      |

#### NOTE:

For information regarding devices processed to Military Specifications, see the Signetics Military Products Data Manual.

#### INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

| PINS | DESCRIPTION | 74S   | 74LS   |

|------|-------------|-------|--------|

| All  | Inputs      | 1Sul  | 1LSul  |

| All  | Outputs     | 10Sul | 30LSul |

#### NOTE:

Where a 74S unit load (Sul) is  $50\mu A~I_{lH}$  and  $-2.0mA~I_{lL}$ , and a 74LS unit load (LSul) is  $20\mu A~I_{lH}$  and  $-0.4mA~I_{lL}$ .

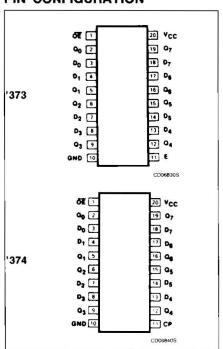

#### PIN CONFIGURATION

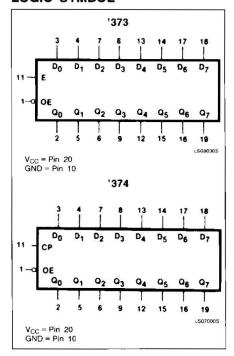

#### LOGIC SYMBOL

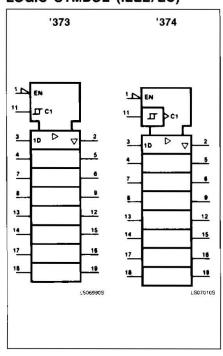

#### LOGIC SYMBOL (IEEE/EC)

## 74LS373, 74LS374, S373, S374

The data on the D inputs are transferred to the latch outputs when the Latch Enable (E) input is HIGH. The latch remains transparent to the data inputs while E is HIGH, and stores the data present one set-up time before the HIGH-to-LOW enable transition. The enable gate has hysteresis built in to help minimize problems that signal and ground noise can cause on the latching operation.

The 3-State output buffers are designed to drive heavily loaded 3-State buses, MOS memories, or MOS microprocessors. The active LOW Output Enable ( $\overline{OE}$ ) controls all eight 3-State buffers independent of the latch

operation. When  $\overline{OE}$  is LOW, the latched or transparent data appears at the outputs. When  $\overline{OE}$  is HIGH, the outputs are in the HIGH impedance "off" state, which means they will neither drive nor load the bus.

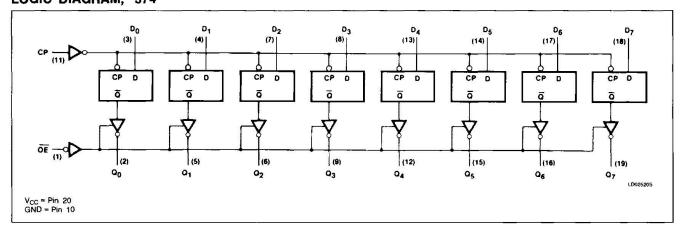

The '374 is an 8-bit, edge-triggered register coupled to eight 3-State output buffers. The two sections of the device are controlled independently by the Clock (CP) and Output Enable (OE) control gates.

The register is fully edge triggered. The state of each D input, one set-up time before the LOW-to-HIGH clock transition, is transferred

to the corresponding flip-flop's Q output. The clock buffer has hysteresis built in to help minimize problems that signal and ground noise can cause on the clocking operation.

The 3-State output buffers are designed to drive heavily loaded 3-State buses, MOS memories, or MOS microprocessors. The active LOW Output Enable ( $\overline{OE}$ ) controls all eight 3-State buffers independent of the register operation. When  $\overline{OE}$  is LOW, the data in the register appears at the outputs. When  $\overline{OE}$  is HIGH, the outputs are in the HIGH impedance "off" state, which means they will neither drive nor load the bus.

#### LOGIC DIAGRAM, '373

#### LOGIC DIAGRAM, '374

#### MODE SELECT - FUNCTION TABLE '373

| ODEDATING MODES                    |                     | INPUTS |                   | MITERNAL DEGISTED               | OUTPUTS    |

|------------------------------------|---------------------|--------|-------------------|---------------------------------|------------|

| OPERATING MODES                    | ŌE E D <sub>n</sub> |        | INTERNAL REGISTER | Q <sub>0</sub> - Q <sub>7</sub> |            |

| Enable and read register           | L<br>L              | Н      | L<br>H            | L<br>H                          | L<br>H     |

| Latch and read register            | L                   | L      | l<br>h            | L<br>H                          | L<br>H     |

| Latch register and disable outputs | H<br>H              | L      | l<br>h            | L<br>H                          | (Z)<br>(Z) |

74LS373, 74LS374, S373, S374

#### MODE SELECT - FUNCTION TABLE '374

| ODEDATING MODES                   |        | INPUTS   |        | INTERNAL REGISTER | OUTPUTS                         |

|-----------------------------------|--------|----------|--------|-------------------|---------------------------------|

| OPERATING MODES                   | ŌĒ     | CP       | Dn     | INTERNAL REGISTER | Q <sub>0</sub> - Q <sub>7</sub> |

| Load and read register            | L      | <b>1</b> | L<br>L | L<br>H            | L<br>H                          |

| Load register and disable outputs | H<br>H | <b>↑</b> | l<br>h | L<br>H            | (Z)<br>(Z)                      |

H = HIGH voltage level

#### ABSOLUTE MAXIMUM RATINGS (Over operating free-air temperature range unless otherwise noted.)

| £                | PARAMETER                                      | 74LS                     | 745                      | UNIT |

|------------------|------------------------------------------------|--------------------------|--------------------------|------|

| V <sub>CC</sub>  | Supply voltage                                 | 7.0                      | 7.0                      | V    |

| VIN              | Input voltage                                  | -0.5 to +7.0             | -0.5 to +5.5             | V    |

| I <sub>IN</sub>  | Input current                                  | -30 to +1                | -30 to +5                | mA   |

| V <sub>OUT</sub> | Voltage applied to output in HIGH output state | -0.5 to +V <sub>CC</sub> | -0.5 to +V <sub>CC</sub> | V    |

| TA               | Operating free-air temperature range           | 0 to                     | o 70                     | °C   |

#### RECOMMENDED OPERATING CONDITIONS

|                 |                                | 74LS |     |      | 748  |     |      |      |

|-----------------|--------------------------------|------|-----|------|------|-----|------|------|

|                 | PARAMETER                      | Min  | Nom | Max  | Min  | Nom | Max  | UNIT |

| V <sub>CC</sub> | Supply voltage                 | 4.75 | 5.0 | 5.25 | 4.75 | 5.0 | 5.25 | ٧    |

| V <sub>IH</sub> | HIGH-level input voltage       | 2.0  |     |      | 2.0  |     |      | ٧    |

| VIL             | LOW-level input voltage        |      |     | +0.8 |      |     | +0.8 | ٧    |

| I <sub>IK</sub> | Input clamp current            |      |     | -18  |      |     | -18  | mA   |

| loh             | HIGH-level output current      |      |     | -2.6 |      |     | -6.5 | mA   |

| loL             | LOW-level output current       |      |     | 24   |      |     | 20   | mA   |

| TA              | Operating free-air temperature | 0    |     | 70   | 0    |     | 70   | °C   |

h = HIGH voltage level one set-up time prior to the LOW-to-HIGH clock transition or HIGH-to-LOW  $\overline{\text{OE}}$  transition

L = LOW voltage level

I = LOW voltage level one set-up time prior to the LOW-to-HIGH clock transition or HIGH-to-LOW OE transition

<sup>(</sup>Z) = HIGH impedance "off" state ↑ = LOW-to-HIGH clock transition

## 74LS373, 74LS374, S373, S374

#### DC ELECTRICAL CHARACTERISTICS (Over recommended operating free-air temperature range unless otherwise noted.)

| PARAMETER       |                                           |                                                  |                              | ONDITIONS!                               |        | 74L              | .S373, | 374  | 74               | S373, 3 | 374   |    |

|-----------------|-------------------------------------------|--------------------------------------------------|------------------------------|------------------------------------------|--------|------------------|--------|------|------------------|---------|-------|----|

|                 |                                           |                                                  | TEST CONDITIONS <sup>1</sup> |                                          | Min    | Typ <sup>2</sup> | Max    | Min  | Typ <sup>2</sup> | Max     | TINU  |    |

| V <sub>OH</sub> | HIGH-level output voltage                 | V <sub>CC</sub> = MIN, V <sub>I</sub>            | H = MIN,                     | / <sub>IL</sub> = MAX, I <sub>OH</sub> = | MAX    | 2.4              | 3.1    |      | 2.4              | 3.1     |       | ٧  |

| \/              | LOW-level output voltage                  | V <sub>CC</sub> = MIN,<br>V <sub>IH</sub> = MIN, |                              | I <sub>OL</sub> = MAX                    |        |                  | 0.35   | 0.5  |                  |         | 0.5   | ٧  |

| V <sub>OL</sub> | LOW-lever output voltage                  | $V_{IL} = MAX$                                   |                              | I <sub>OL</sub> = 12mA (7                | 4LS)   |                  | 0.25   | 0.4  |                  |         |       | ٧  |

| VIK             | Input clamp voltage                       | V <sub>CC</sub> = MIN, I <sub>I</sub>            | = I <sub>IK</sub>            |                                          |        |                  |        | -1.5 |                  |         | -1.2  | ٧  |

| lo-u            | Off-state output current,                 | V <sub>CC</sub> = MAX, V                         | = MIN                        | V <sub>O</sub> = 2.7V                    |        |                  |        | 20   |                  |         |       | μΑ |

| lozh            | HIGH-level voltage applied                | VCC - IVIAA, V                                   | IH - IMILA                   | V <sub>O</sub> = 2.4V                    |        |                  |        |      | 7-2              |         | 50    | μΑ |

| I               | Off-state output current,                 | V = MAY V                                        | V NAV V BAINI                |                                          |        |                  |        | -20  | 7,865            |         |       | μΑ |

| lozu            | LOW-level voltage applied                 | V <sub>CC</sub> = MAX, V <sub>IH</sub> = MIN     |                              | V <sub>O</sub> = 0.5V                    |        |                  |        |      |                  |         | -50   | μΑ |

| f.              | Input current at maximum                  | V <sub>CC</sub> = MAX                            |                              | $V_1 = 7.0V$                             |        |                  |        | 0.1  |                  |         |       | mA |

| lp .            | input voltage                             | ACC = MAX                                        |                              | $V_1 = 5.5V$                             |        |                  |        |      |                  |         | 1.0   | mA |

| I <sub>IH</sub> | HIGH-level input current                  | V <sub>CC</sub> = MAX, V                         | $t_1 = 2.7V$                 |                                          |        | , i              |        | 20   |                  |         | 50    | μΑ |

| L               | LOW-level input current                   | V <sub>CC</sub> = MAX                            |                              | $V_1 = 0.4V$                             |        |                  |        | -0.4 |                  |         |       | mA |

| ارر             | LOW-lever input current                   | ACC - INIAX                                      |                              | $V_1 = 0.5V$                             |        |                  |        |      |                  |         | -0.25 | mA |

| los             | Short-circuit output current <sup>3</sup> | V <sub>CC</sub> = MAX                            |                              |                                          |        | -30              |        | -130 | -40              |         | -100  | mA |

|                 |                                           |                                                  | I <sub>CCZ</sub>             | DE = 4.5V                                | 'LS373 |                  | 24     | 40   |                  |         |       | mA |

|                 |                                           |                                                  | I <sub>CCL</sub>             | DE = 0V                                  | 'S373  |                  |        |      |                  | 105     | 160   | mA |

|                 |                                           | 1                                                | lccz (                       | DE = 4.5V                                | 'LS374 |                  | 27     | 40   |                  |         |       | mA |

| Icc             | Supply current (total)                    | V <sub>CC</sub> = MAX                            | 1 100                        | II inputs<br>ounded                      | '\$374 |                  |        |      |                  | 102     | 140   | mA |

|                 |                                           |                                                  |                              | P, OE = 4.5V<br>inputs = GND             | 'S374  |                  |        |      |                  | 131     | 180   | mA |

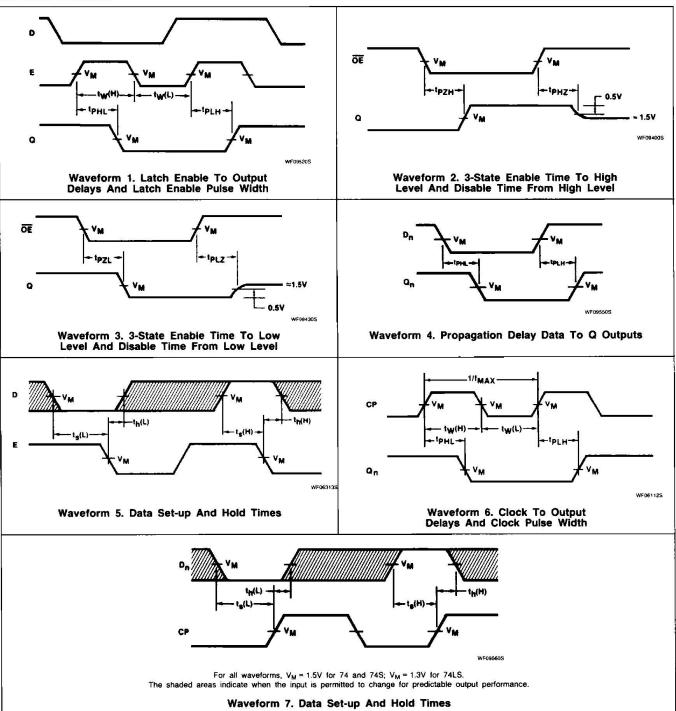

#### AC ELECTRICAL CHARACTERISTICS $T_A = 25$ °C, $V_{CC} = 5.0$ V

|                                      |                                             |                                  | 74LS                                    |          | 74                     | ıs                |      |

|--------------------------------------|---------------------------------------------|----------------------------------|-----------------------------------------|----------|------------------------|-------------------|------|

|                                      | PARAMETER                                   | TEST CONDITIONS                  | C <sub>L</sub> = 45pF, R <sub>L</sub> : |          | C <sub>L</sub> = 15pF, | $R_L = 280\Omega$ | UNIT |

|                                      |                                             |                                  | Min                                     | Max      | Min                    | Max               |      |

| f <sub>MAX</sub>                     | Maximum clock frequency                     | Waveform 6, '374                 | 35                                      |          | 75                     |                   | MHz  |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay<br>Latch enable to output | Waveform 1, '373                 |                                         | 30<br>30 |                        | 14<br>18          | ns   |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay<br>Data to output         | Waveform 4, '373                 |                                         | 18<br>18 |                        | 12<br>12          | ns   |

| t <sub>PLH</sub>                     | Propagation delay<br>Clock to output        | Waveform 6, '374                 |                                         | 28<br>28 |                        | 15<br>17          | ns   |

| t <sub>PZH</sub>                     | Enable time to HIGH level                   | Waveform 2                       |                                         | 28       |                        | 15                | ns   |

| t <sub>PZL</sub>                     | Enable time to LOW level                    | Waveform 3, '373 '374            |                                         | 36<br>28 |                        | 18<br>18          | ns   |

| t <sub>PHZ</sub>                     | Disable time from HIGH level                | Waveform 2, C <sub>L</sub> = 5pF |                                         | 20       |                        | 9                 | ns   |

| t <sub>PLZ</sub>                     | Disable time from LOW level                 | Waveform 3, C <sub>L</sub> = 5pF |                                         | 25       |                        | 12                | ns   |

#### NOTE:

Per industry convention, f<sub>MAX</sub> is the worst case value of the maximum device operating frequency with no constraints on t<sub>r</sub>, t<sub>f</sub>, pulse width or duty cycle.

<sup>1.</sup> For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable type.

<sup>2.</sup> All typical values are at  $V_{CC} = 5V$ ,  $T_A = 25^{\circ}C$ . 3.  $I_{OS}$  is tested with  $V_{OUT} = +0.5V$  and  $V_{CC} = V_{CC}$  MAX + 0.5V. Not more than one output should be shorted at a time and duration of the short circuit should not

# 74LS373, 74LS374, S373, S374

#### **AC WAVEFORMS**

# 74LS373, 74LS374, S373, S374

#### AC SET-UP REQUIREMENTS $T_A = 25$ °C, $V_{CC} = 5.0$ V

|                                          | DADAMETED                         | 74LS             |          | LS  | 74       |     |      |

|------------------------------------------|-----------------------------------|------------------|----------|-----|----------|-----|------|

|                                          | PARAMETER                         | TEST CONDITIONS  | Min      | Max | Min      | Max | UNIT |

| t <sub>W</sub> (H)<br>t <sub>W</sub> (L) | Latch enable pulse width          | Waveform 1, '373 | 15<br>15 |     | 6<br>7.3 |     | ns   |

| ts                                       | Set-up time, data to latch enable | Waveform 5, '373 | 5        |     | 0        |     | ns   |

| t <sub>h</sub>                           | Hold time, data to latch enable   | Waveform 5, '373 | 20       |     | 10       |     | ns   |

| t <sub>W</sub> (H)<br>t <sub>W</sub> (L) | Clock pulse width                 | Waveform 6, '374 | 15<br>15 |     | 6<br>7.3 |     | ns   |

| ts                                       | Set-up time, data to clock        | Waveform 7, '374 | 20       |     | 5        |     | ns   |

| t <sub>h</sub>                           | Hold time, data to clock          | Waveform 7, '374 | 0        |     | 2        |     | ns   |

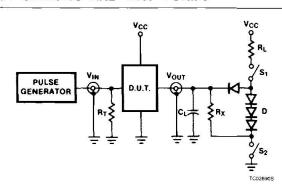

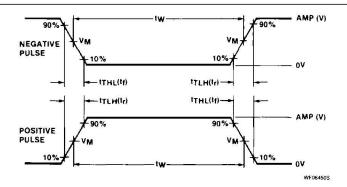

#### **TEST CIRCUITS AND WAVEFORMS**

$V_M = 1.3V$  for 74LS;  $V_M = 1.5V$  for all other TTL families. Input Pulse Definition

Test Circuit For 3-State Outputs

#### **SWITCH POSITION**

| TEST             | SWITCH 1 | SWITCH 2 |

|------------------|----------|----------|

| t <sub>PZH</sub> | Open     | Closed   |

| t <sub>PZL</sub> | Closed   | Open     |

| tenz             | Closed   | Closed   |

| tpLZ             | Closed   | Closed   |

#### **DEFINITIONS**

$R_L$  = Load resistor to  $V_{CC}$ ; see AC CHARACTERISTICS for value.

C<sub>L</sub> = Load capacitance includes jig and probe capacitance; see AC CHARACTERISTICS for value.

$R_T$  = Termination resistance should be equal to  $Z_{OUT}$ of Pulse Generators.

D = Diodes are 1N916, 1N3064, or equivalent.  $R_X = 1k\Omega$  for 74, 74S,  $R_X = 5k\Omega$  for 74LS.

$t_{\text{TLH}},\;t_{\text{THL}}$  Values should be less than or equal to the table entries.

| FAMILY | IN        | PUT PULSE | REQUIREME   | NTS   |                  |

|--------|-----------|-----------|-------------|-------|------------------|

| FAMILY | Amplitude | Rep. Rate | Pulse Width | tTLH  | t <sub>THL</sub> |

| 74     | 3.0V      | 1 MHz     | 500ns       | 7ns   | 7ns              |

| 74LS   | 3.0V      | 1MHz      | 500ns       | 15ns  | 6ns              |

| 74S    | 3.0V      | 1MHz      | 500ns       | 2.5ns | 2.5ns            |