#### 7811 Network Security Processor

$Hi/fn^{\text{$\%$}}$  supplies two of the Internet's most important raw materials: compression and encryption. Hi/fn is also the world's first company to put both on a single chip, creating a processor that performs compression and encryption at a faster speed than a conventional CPU alone could handle, and for much less than the cost of a Pentium<sup>®</sup> or comparable processor.

Hi/fn, Inc. 750 University Avenue Los Gatos, CA 95032 info@hifn.com http://www.hifn.com Tel: 408-399-3500 Fax: 408-399-3501

Hi/fn Applications Support Hotline: 408-399-3544

#### Disclaimer

Hi/fn reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

Hi/fn warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with Hi/fn's standard warranty. Testing and other quality control techniques are utilized to the extent Hi/fn deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

HI/FN SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of Hi/fn products in such critical applications is understood to be fully at the risk of the customer. Questions concerning potential risk applications should be directed to Hi/fn through a local sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

Hi/fn does not warrant that its products are free from infringement of any patents, copyrights or other proprietary rights of third parties. In no event shall Hi/fn be liable for any special, incidental or consequential damages arising from infringement or alleged infringement of any patents, copyrights or other third party intellectual property rights.

"Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals," must be validated for each customer application by customer's technical experts.

The use of this product may require a license from Motorola. A license agreement for the right to use Motorola patents may be obtained through Hi/fn or directly from Motorola.

DS-0018-00 (4/2000) © 1997-2000 by Hi/fn, Inc., including one or more U.S. patents No.: 4,701,745, 5,003,307, 5,016,009, 5,126,739, 5,146,221, 5,414,425, 5,414,850, 5,463,390, 5,506,580, 5,532,694. Other patents pending. Hi/fn and LZS are registered trademarks of Hi/fn, Inc. All other trademarks are the property of their respective holders.

This product is approved for export and reexport under License Exception ENC to non-government end-users worldwide except those located in Iran, Iraq, Libya, North Korea, Sudan, Syria, Yugoslavia (Serbia), and Talibancontrolled regions of Afghanistan.

# **Table of Contents**

| 1  | Introduction<br>1.1 Features<br>1.2 Description<br>1.3 Block Diagram<br>1.4 Specification Summary                                                                                                                        | 7<br>8<br>10                                 |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 2  | Device Architecture         2.1 Data and Control Flow         2.2 Functional Units                                                                                                                                       | 13                                           |

| 3  | Subsystem Configurations         3.1       Subsystem Variants                                                                                                                                                            |                                              |

| 4  | Signal Description                                                                                                                                                                                                       | 26                                           |

| 5  | Memory Maps                                                                                                                                                                                                              | 30<br>31<br>33                               |

| 6  | <ul> <li>General Purpose DMA (GPDMA) Units</li> <li>6.1 Data and Message Modes</li> <li>6.2 Handshaking</li> <li>6.3 Scatter/Gather</li> <li>6.4 Data Mode Example</li> <li>6.5 GPDMA Arbitration and Polling</li> </ul> | 37<br>42<br>43<br>45                         |

| 7  | The Security Engine7.1Operation7.2Registers7.3Descriptors7.4Encode/Decode Command Structures7.5Read RAM/Write RAM Command Structures7.6Source Structures7.7Dest Structures7.8Result Structures7.9Context RAM Usage       | 49<br>51<br>52<br>56<br>64<br>65<br>65<br>65 |

| 8  | Registers         8.1       Group 0 Registers         8.2       Group 1 Registers                                                                                                                                        | 73                                           |

| 9  | Clock Generation and Reset       1         9.1       Clock Generation       1         9.2       Reset       1                                                                                                            | 21                                           |

| 10 | Testability                                                                                                                                                                                                              |                                              |

| 11 | DC Specifications                                                                                                                                                                                                        | 23<br>23                                     |

| 12 | AC Specifications                                                                                                                                                                                                        |                                              |

# hi fn<sub>®</sub>

|      | 12.2 PCI Timing.                                                                           |    |

|------|--------------------------------------------------------------------------------------------|----|

|      | 12.3 MIPS Interface Timing                                                                 |    |

|      | 12.4 SDRAM Timing 1                                                                        | 25 |

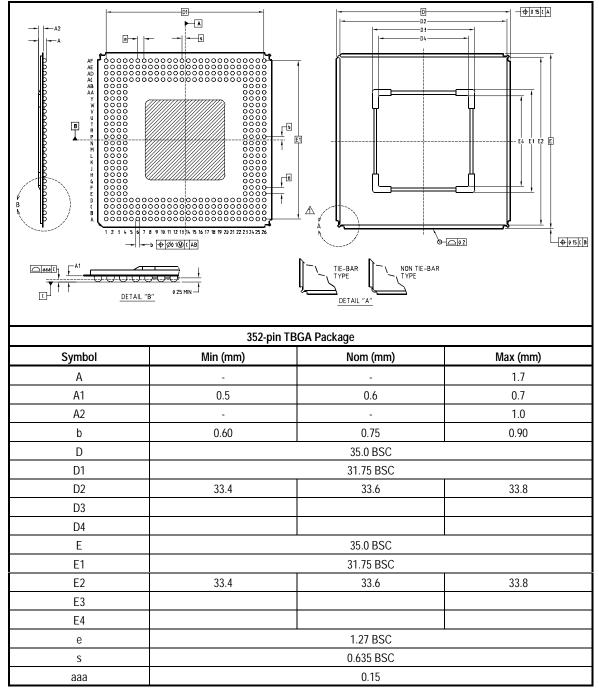

| 13   | Physical Specifications 1                                                                  | 26 |

|      | 13.1 Package Dimensions                                                                    |    |

|      | 13.2 Pin Configuration 1                                                                   | 28 |

| Eie  |                                                                                            |    |

|      | jures                                                                                      | 0  |

|      | rre 1. System concept                                                                      |    |

|      | rre 2. Ordering information                                                                |    |

|      | ure 3. Block Diagram of the 7811                                                           |    |

|      | re 4. Functional units in the 7811                                                         |    |

|      | are 5. Pipeline configurations for encryption and decryption                               |    |

|      | rre 6. Group 0 registers                                                                   |    |

|      | rre 7. Group 1 register summary                                                            |    |

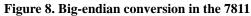

|      | rre 8. Big-endian conversion in the 7811                                                   |    |

|      | re 9. Elements of a 7811 subsystem                                                         |    |

|      | rre 10. Typical subsystem                                                                  |    |

|      | rre 11. High Performance Subsystem                                                         |    |

|      | rre 12. Minimal (no CPU) subsystem                                                         |    |

|      | re 13. Signal Description<br>re 14. Recommended terminations if MIPS processor is not used |    |

|      | ire 15. Usage of PCI memory space by the 7811                                              |    |

|      | re 16. MIPS-to-PCI address decoding                                                        |    |

|      | re 17. Usage of MIPS memory space by the 7811                                              |    |

|      | ire 18. EEPROM memory map                                                                  |    |

|      | re 19. PCI configuration space                                                             |    |

|      | ire 20. PCI Status Register                                                                |    |

|      | ire 21. Application-level GPDMA example                                                    |    |

|      | are 22. GPDMA operation in Message mode                                                    |    |

|      | are 23. GPDMA operation in Message mode                                                    |    |

|      | ire 24. GPDMA Source command structure                                                     |    |

|      | are 25. Bit fields in the Source Control word                                              |    |

|      | are 26. GPDMA Dest Command structure                                                       |    |

| Fio  | are 27. Bit fields in the Dest Control word                                                | 42 |

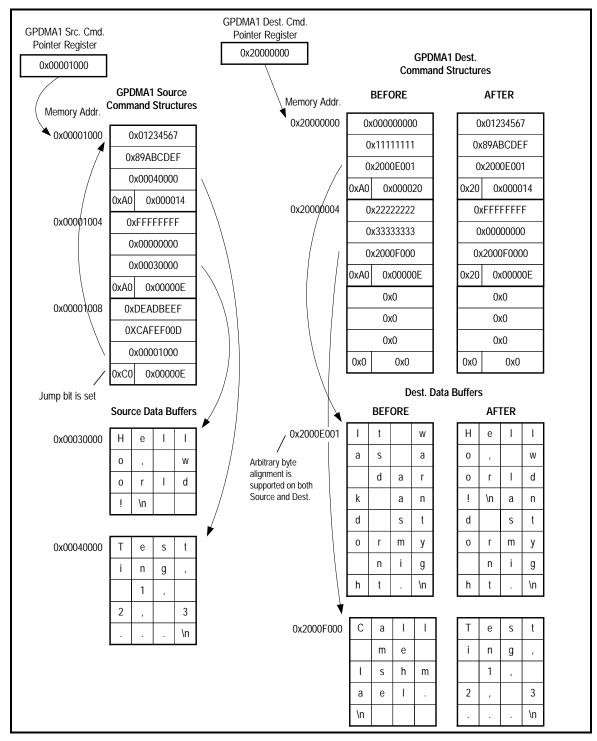

|      | ire 28. GPDMA example                                                                      |    |

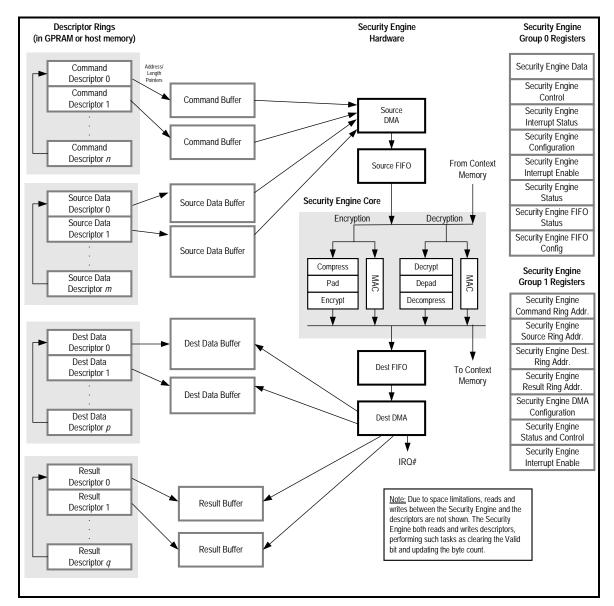

|      | ire 29. Security engine block diagram                                                      |    |

|      | are 30. Mapping between 16-bit and 32-bit representations of the Security                  |    |

| 1 15 | Engine's commands and descriptors                                                          | 50 |

| Fig  | are 31. Security Engine registers in the Group 0 register space                            |    |

|      | are 32. Security Engine registers in the Group 1 register space                            |    |

|      | are 33. Command descriptor                                                                 |    |

| 0    | re 34. Source descriptor                                                                   |    |

|      | ire 35. Dest descriptor                                                                    |    |

| Fig  | re 36. Result descriptor                                                                   | 55 |

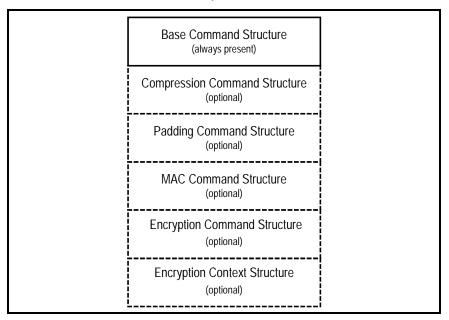

|      | are 37. Command structures                                                                 |    |

|      | ire 38. Base command structure                                                             |    |

|      | are 39. Compress command structure                                                         |    |

|      | are 40. Pad command structure                                                              |    |

|      | ire 41. Mac command structure                                                              |    |

|      | re 42. Encryption command structure                                                        |    |

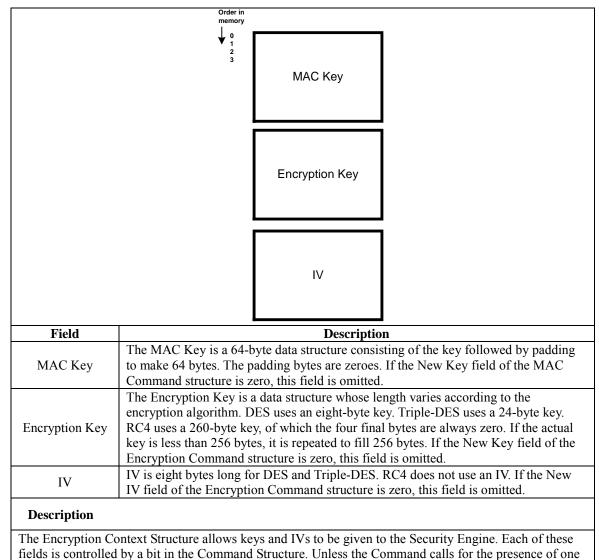

|      | re 43. Encryption Context structure                                                        |    |

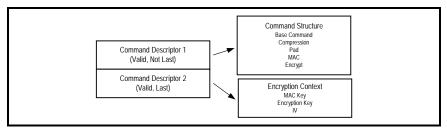

|      | re 44. Typical use of descriptors for a command that requires encryption                   |    |

# hi fn.

| Figure 45. Read RAM command structure                                                                         |   |

|---------------------------------------------------------------------------------------------------------------|---|

| Figure 46. Write RAM command structure                                                                        | 5 |

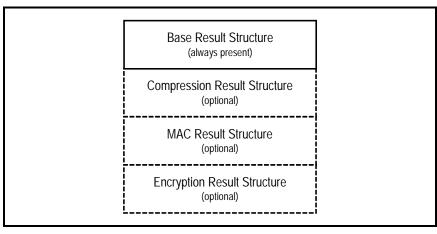

| Figure 47. Result structures                                                                                  | 5 |

| Figure 48. Base Result Structure                                                                              | 5 |

| Figure 49. Compression Result Structure                                                                       |   |

| Figure 50. MAC Result Structure                                                                               |   |

| Figure 51. Encryption Result Structure                                                                        |   |

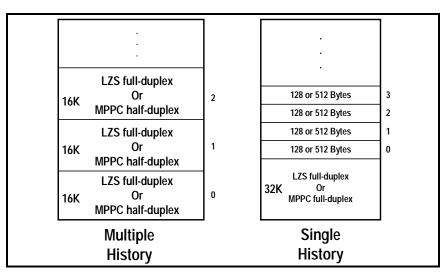

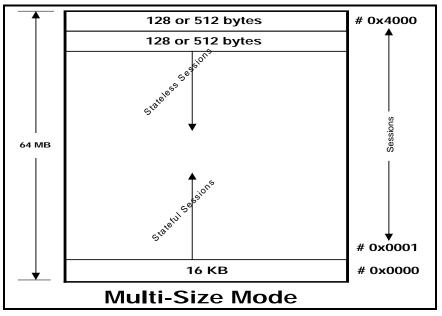

| Figure 52. Context memory modes                                                                               |   |

| Figure 53. Context RAM memory usage in single-size modes                                                      | ) |

| Figure 54. Multi-size mode example                                                                            | ) |

| Figure 55. Multi-size mode memory allocation algorithm                                                        |   |

| Figure 56. Number of Sessions in Multi-size mode                                                              |   |

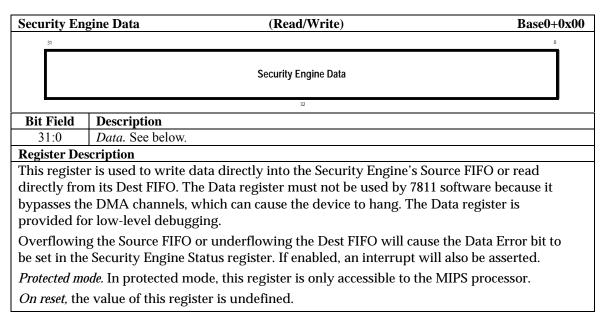

| Figure 57. Security Engine Data register                                                                      |   |

| Figure 58. Security Engine Control register                                                                   |   |

|                                                                                                               |   |

| Figure 59. Security Engine Interrupt Status register                                                          |   |

| Figure 60. Security Engine Configuration register                                                             |   |

| Figure 61. Security Engine Interrupt Enable register                                                          |   |

| Figure 62. Security Engine Status register                                                                    |   |

| Figure 63. Security Engine FIFO Status register                                                               |   |

| Figure 64. Security Engine FIFO Configuration register                                                        |   |

| Figure 65. Security Engine Command Ring Address register                                                      |   |

| Figure 66. Security Engine Source Ring Address register                                                       |   |

| Figure 67. Security Engine Result Ring Address register                                                       |   |

| Figure 68. Security Engine Dest Ring Address register                                                         |   |

| Figure 69. Security Engine Status and Control register                                                        |   |

| Figure 70. Security Engine Interrupt Enable register                                                          | 5 |

| Figure 71. Security Engine DMA Config register                                                                |   |

| Figure 72. PCI Address "OR" mask register                                                                     | 1 |

| Figure 73. PCI Interrupt register                                                                             | 3 |

| Figure 74. PCI Interrupt Enable register                                                                      | 3 |

| Figure 75. MIPS Interrupt register                                                                            | ) |

| Figure 76. MIPS Interrupt Mask register                                                                       | ) |

| Figure 77. RNG Enable register                                                                                | ) |

| Figure 78. RNG Config register                                                                                |   |

| Figure 79. Decoding of the first prescaler field                                                              | l |

| Figure 80. RNG Data register                                                                                  |   |

| Figure 81. RNG Status register                                                                                |   |

| Figure 82. MIPS SDRAM1 Address register                                                                       |   |

| Figure 83. MIPS SDRAM2 Address register                                                                       |   |

| Figure 84. MIPS Group 1 Address register                                                                      |   |

| Figure 85. MIPS Group 0 Address register                                                                      |   |

| Figure 86. MIPS PCI1 Address register                                                                         |   |

| Figure 87. MIPS PCI2 Address register                                                                         |   |

| Figure 88. MIPS PCI1 Translation register                                                                     |   |

| Figure 89. MIPS PCI2 Translation register                                                                     |   |

| Figure 90. MIPS Config register                                                                               |   |

| Figure 91. MIPS Reset register                                                                                |   |

| Figure 92. Revision Number register                                                                           | ) |

| Figure 93. EEPROM data register                                                                               |   |

| Figure 94. GPDMA1 Source Address register                                                                     |   |

| Figure 95. GPDMA1 Source Address register                                                                     |   |

|                                                                                                               |   |

| Figure 96. GPDMA1 Dest Address register                                                                       |   |

| Figure 97. GPDMA2 Dest Address register.       102         Figure 98. GPDMA1_2 Arbitration register       103 |   |

|                                                                                                               | , |

# hi fn<sub>®</sub>

| Figure 99. GPDMA1_2 Config register            |     |

|------------------------------------------------|-----|

| Figure 100. GPDMA1_2 Status register           |     |

| Figure 101. GPDMA1_2 Interrupt Enable register |     |

| Figure 102. PCI BAR0 Shadow register           | 109 |

| Figure 103. PCI BAR1 Shadow register           | 109 |

| Figure 104. PCI BAR2 Shadow register           | 110 |

| Figure 105. SDRAM Config register              |     |

| Figure 106. GPDMA3 Source Address register     | 111 |

| Figure 107. GPDMA4 Source Address register     | 111 |

| Figure 108. GPDMA3 Dest Address register       |     |

| Figure 109. GPDMA4 Dest Address register       | 112 |

| Figure 110. GPDMA3_4 Arbitration register      |     |

| Figure 111. GPDMA3_4 Config register           |     |

| Figure 112. GPDMA3 4 Status register           |     |

| Figure 113. GPDMA3_4 Interrupt Enable register | 118 |

| Figure 114. Global Status register             |     |

| Figure 115. Test-and-Set register              |     |

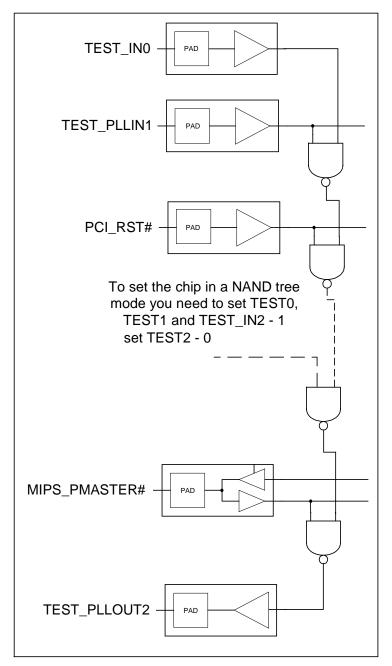

| Figure 116. Pin ordering for NAND Tree         |     |

| Figure 117. Recommended operating conditions   |     |

| Figure 118. Recommended operating conditions   |     |

| Figure 119. DC electrical characteristics      |     |

| Figure 120. Test conditions                    |     |

| Figure 121. MIPS_CLK parameters                | 125 |

| Figure 122. Package dimensions                 |     |

| Figure 123. Pin configuration, columns A-N     |     |

| Figure 124. Pin configuration, columns P-AF    |     |

| Figure 125. Pin configuration, alphabetical    |     |

|                                                |     |

### Introduction

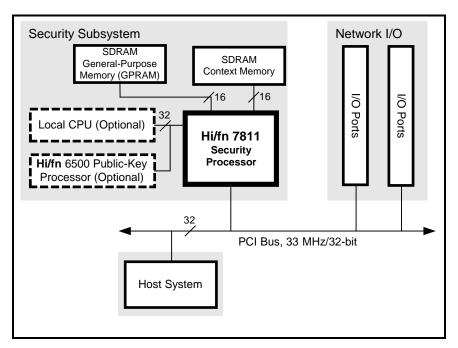

The Hi/fn® 7811 Security Processor performs network security functions in hardware. Its pipelined architecture allows compression, encryption, and authentication to be performed in a single pass. The 7811 hardware supports the encryption, compression, and authentication algorithms, required for IPSec, PPTP, L2TP, PPP, and others.

The 7811 is used in network servers, routers, and gateways. It accelerates the security functions of virtual private networks, electronic commerce, and secure Web sessions. The 7811's PCI interface allows it to be implemented as an add-in card or on the motherboard.

A 7811-based security subsystem includes a PCI interface, SDRAM memory, and a dedicated microprocessor. Running Hi/fn's security software, such a subsystem handles network security protocols at the packet level, supporting the Internet security protocol (IPSec) in both tunnel and transport modes. The PPP, PPTP, and L2TP transmission protocols are supported in addition to TCP/IP.

#### 1.1 Features

#### **Security Engine**

- Pipelined security engine performs encryption/decryption, compression/ decompression, and authentication

- Supports major security protocols

- Built-in DMA engines handle command and data streams

- Supports 32K simultaneous IPSec sessions

- Optional lock/unlock mode allows manufacturer-selected levels of exportability

- Backward-compatible with the Hi/fn 7751

#### Local CPU Interface

- Glueless CPU interface connects to a 32-bit MIPS microprocessor

- Local CPU works with 7811 to boost performance and offload host CPU

- Dedicated CPU allows sensitive operations to be isolated from the host

#### **SDRAM** Interfaces

- General purpose SDRAM interface supports up to 64 MB and increases performance and reduces PCI bus activity

- Dedicated context memory interface supports up to 64 MB for session contexts

- Memory can be made inaccessible to the host, enhancing security

#### **PCI Interface**

Bus-mastering 32-bit, 33 MHz PCI interface

#### True Random Number Generator

• On-chip true-random number for public-key cryptography and IV generation

#### **Security Barrier**

- Security barrier features protect security-relevant data items such as keys

- Encryption hardware and memory can be made inaccessible from PCI

- Supports FIPS 140-1, Level 3-compliant security subsystems

Figure 1. System concept

# 1.2 Description

Hi/fn's 7811 is a maximum-performance network security processor, achieving high performance through a pipelined Security Engine, two private memory buses, an attached microprocessor, and four general purpose DMA units. In addition to high performance, the 7811 is designed for high security. When the 7811 is in *protected mode*, encryption keys, session keys, and other security-relevant data items cannot be recovered from the 7811. The 7811 has many additional security features to protect its data and its operation, making it ideal for FIPS 140-1, Level 3-compliant security subsystems. These same features also enhance the security of systems that do not require the stringent FIPS 140-1 Level 3 standards.

The 7811 supports up to 64 MB of SDRAM on each of two local buses. *Context memory* holds session-oriented context information. *GPRAM (general purpose memory)* provides I/O buffering and general purpose storage. The 7811 supports 32768 independent, simultaneous IPSec sessions.

The 7811 is a PCI bus master, controlling data moving into and out of the host system with its four general purpose DMA units. When the host has packets for the 7811 to process, it creates a small DMA command structure and sets a Valid bit. The 7811 transfers the commands and data, processes the packets, and writes the transformed packets and status information back to host memory. The 7811 maintains all security information locally.

An on-chip true-random number generator (RNG) provides random data for use in public-key encryption.

Unless run in 7751 compatibility mode, an attached microprocessor controls the 7811. The processor initializes the 7811, sets up and tears down each security session, controls the 7811's four general purpose DMA engines, performs header processing, and manages the security subsystem in general. The processor adds performance to the security subsystem, reduces host overhead, and allows the

creation of a security barrier, where the security subsystem is isolated from the rest of the system and security information (such as keys) cannot be recovered by the host or an intruder who has gained control of the host. The subsystem generally includes a processor, a boot ROM, and local memory.

Hi/fn provides security software for the 7811, including a complete set of software for the 7811's MIPS processor and interface routines for the host.

With or without the MIPS CPU, the 7811 can run in 7751 compatibility mode, where it functions as an upgraded, higher-performance 7751 security processor.

| Part Number | Description                     |

|-------------|---------------------------------|

| 7811-PB3    | 7811 Network Security Processor |

Figure 2. Ordering information

1.3 Block Diagram

Figure 3. Block Diagram of the 7811

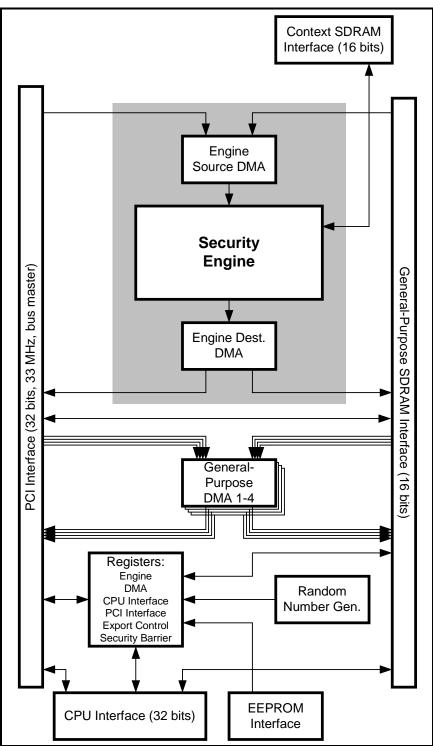

| Block                                            | Description                                                                                                                                                                                                                                                                                                                                | See<br>Sections |

|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| Security Engine                                  | Pipelined compression, encryption,<br>authentication, and checksum/CRC/LCB<br>engine with internal DMA engines that<br>operate independently from the general<br>purpose DMA engines.                                                                                                                                                      | 2.2.1, 6        |

| General Purpose<br>DMA Engines<br>(GPDMA1-4)     | Four identical DMA engines that transfer<br>commands and data to and from the 7811<br>subsystem. In protected mode, Only the<br>source registers of GPDMA 1 and the<br>destination registers of GPDMA 4 are<br>accessible to the host; the rest are<br>controlled by the MIPS CPU.                                                         | 2.2.2           |

| Registers                                        | Configuration, control, and status registers.                                                                                                                                                                                                                                                                                              | 2.2.3, 8        |

| Random Number<br>Generator                       | A hardware random-number generator used in public-key cryptography.                                                                                                                                                                                                                                                                        | 2.2.4           |

| PCI Interface                                    | Bus-mastering 33-MHz/32-bit PCI<br>interface. All features of the 7811 are<br>available to the host through PCI<br>accesses, provided the 7811 is in<br>unprotected mode. In protected mode,<br>very little of the 7811 can be accessed<br>through PCI. In addition to being a bus<br>master, the 7781 is also an efficient PCI<br>target. | 2.2.5           |

| Local CPU<br>Interface                           | Glueless interface to a MIPS processor.<br>All features of the 7811 are available to<br>the MIPS processor through memory-<br>mapped accesses.                                                                                                                                                                                             | 2.2.6           |

| EEPROM Interface                                 | Controls an external 93C46 EEPROM<br>containing configuration data, including<br>encryption engine unlock codes that vary<br>according exportability requirements.                                                                                                                                                                         | 2.2.7           |

| General Purpose<br>SDRAM<br>(GPRAM)<br>Interface | Controls external SDRAM containing<br>data buffers, general purpose storage, and,<br>optionally, code for the MIPS processor.<br>(GPRAM is also called "packet<br>SDRAM.") Supports up to 64 MB of<br>SDRAM in the same chip configurations<br>as context SDRAM.                                                                           | 2.2.8           |

| Context SDRAM<br>Interface                       | Controls external SDRAM containing<br>per-session compression, encryption, and<br>authentication state (such as keys and<br>compression histories). Supports up to 64<br>MB of SDRAM. Four-bank SDRAM<br>devices in 8Mx8, 16Mx8, 4Mx16,<br>8Mx16, and 16Mx16 configurations are<br>supported.                                              | 0               |

| Figure 4. Functional | units in | the 7811 |

|----------------------|----------|----------|

|----------------------|----------|----------|

### 1.4 Specification Summary

#### Packet Protocols

- IPSec. The following are supported in both transport and tunnel modes:

- AH, ESP, AH+ESP, AH+IPPCP, ESP+IPPCP, AH+ESP+IPPCP

- PPP transforms:

- CCP, ECP, CCP+ECP

- **PPTP**

- L2TP

#### **Encryption Algorithms**

• DES, 3DES, RC4

#### Authentication Algorithms

• SHA, MD5

#### Compression Algorithms

• LZS, MPPC

#### Performance

- IPSec performance

- 246 Mbps with 3DES encryption and SHA-1 authentication

- 100 Mbps with 3DES encryption, SHA-1 authentication, and LZS compression

- Peak Performance is shown below:

| Mode                       | Speed    |

|----------------------------|----------|

| LZS compression            | 100 Mbps |

| LZS decompression          | 200 Mbps |

| MPPC compression           | 80 Mbps  |

| MPPC decompression         | 200 Mbps |

| 3DES encryption/decryption | 252 Mbps |

| RC4 encryption/decryption  | 200 Mbps |

| SHA authentication         | 301 Mbps |

| MD5 authentication         | 376 Mbps |

#### Packaging

352-pin TBGA

#### Power

LVTTL CMOS device with 5V-tolerant PCI I/O. Maximum power dissipation is 3.0 watts measured at 3.6V.

The 7811 has a unique power saving feature when the MIPS interface is left unused (When used in the 7751 mode, without the GPRAM and MIPS). Pulling up the pin AD2 (signal TEST1) to VDD will ensure this low power mode. Maximum power dissipation in this mode would be 2.3W measured at 3.6V.

## **Device Architecture**

## 2.1 Data and Control Flow

2

The 7811 has a security core that is based on the 7751 Security processor. Unlike the 7751, however, it is not necessary for the host to issue low-level commands to the Security Engine directly. Instead, the host sends packet streams and high-level commands to the 7811, and the 7811's local MIPS processor performs the header processing required to process the packets and issues the Security Engine commands.

By using a relatively inexpensive local processor, the intelligence of the security subsystem is greatly increased. The advantages of this are much lower host CPU and PCI bus overhead, more efficient utilization of the Security Engine, reduced host software complexity, and the ability to create a security boundary.

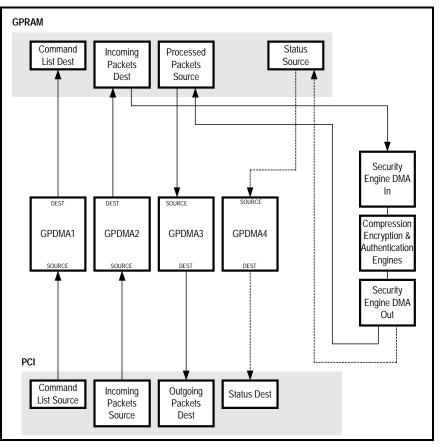

In general, the 7811 uses its GPDMA units to move data and command streams from host memory to GPRAM. The MIPS processor executes the commands through a combination of Security Engine commands and software (for example, while compression and encryption are performed entirely in hardware, header manipulation is generally performed in software). The Security Engine generally uses GPRAM for both input and output, as this gives the highest performance. When the security operations are finished, the MIPS processor queues the fully processed packets to be sent by a GPDMA unit to a buffer in host memory. This is normally system memory, but could be a memory-mapped device.

To the host, security subsystems using more than one 7811 look the same as a single-7811 implementation by using the same I/O and control model regardless of the number of 7811's.

# 2.2 Functional Units

#### 2.2.1 Security Engine

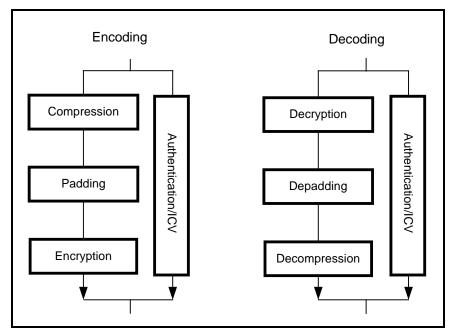

The Security Engine is a fully pipelined unit that performs security and compression processing on packets. It encodes by performing compression, encryption, padding, and authentication field generation. It decodes by performing decryption, decompression, depadding, and authentication header testing.

The Security Engine is compatible with the Hi/fn 7751, containing functionally equivalent units and using the same registers, DMA engines, and command structures. Performance, however, has been significantly enhanced, and the memory and PCI interfaces have been merged with the higher-performance 7811 equivalents.

New functionality of the 7811 is controlled by additional registers, generally at higher addresses than those of the 7751.

Figure 5 shows the engine configurations for encoding and decoding.

Authentication and checksum/CRC/LCB processing take place in parallel with other operations.

For details of the operation of the Security Engine, see chapter 7.

Figure 5. Pipeline configurations for encryption and decryption

# 2.2.2 General Purpose DMA Units (GPDMA1-GPDMA4)

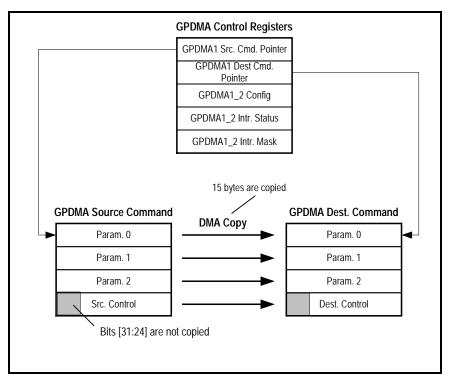

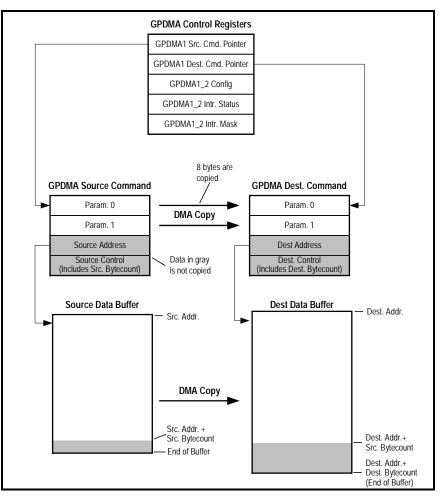

The 7811 has four general purpose DMA units, GPDMA1 through GPDMA4. These units move data from one portion of memory and/or PCI address space to another, using 128-byte burst transfers for maximum efficiency.

The units are identical in structure, and in unprotected mode they are interchangeable. In protected mode, however, the host processor only has access to the Source registers of GPDMA1 and the Destination register of GPDMA4, allowing the host to specify little more than the source of data being sent to the 7811 and the destination of data coming out of the 7811.

For more information about the GPDMA units, see chapter 6.

# 2.2.3 Registers

The 7811 contains a variety of internal registers for initialization, status, and test purposes. These registers are partitioned into two groups. Group 0 contains Security Engine registers. Group 1 contains registers from all of the 7811's functional units. When accessed over PCI, each register group occupies 4KB of memory and has its own base address register. Group 0 uses BAR0, while Group 1 uses BAR1. When accessed by the MIPS processor, each register group has a programmable starting address.

In protected mode, most of these registers are inaccessible to PCI, though they are accessible to the MIPS processor.

# Group 0 Registers

| Register                           | Offset | Reference |

|------------------------------------|--------|-----------|

| Security Engine Data               | 0x00   | Figure 57 |

| Security Engine Control            | 0x04   | Figure 58 |

| Security Engine Interrupt Status   | 0x08   | Figure 59 |

| Security Engine Configuration      | 0x0C   | Figure 60 |

| Security Engine Interrupt Enable   | 0x10   | Figure 61 |

| Security Engine Status             | 0x14   | Figure 62 |

| Security Engine FIFO Status        | 0x18   | Figure 63 |

| Security Engine FIFO Configuration | 0x1C   | Figure 64 |

## Figure 6. Group 0 registers

## Group 1 Registers

| Register                  | Offset | Description                 | Ref.      |

|---------------------------|--------|-----------------------------|-----------|

| Security Engine           | 0x0C   | Address of the next         | Figure 65 |

| Command Ring Address      | UXUC   | command descriptor.         |           |

| Security Engine Source    | 0x1C   | Address of the next         | Figure 66 |

| Ring Address              | UXIC   | source descriptor.          |           |

| Security Engine Result    | 0x2C   | Address of the next         | Figure 67 |

| Ring Address              | 0x2C   | result descriptor.          |           |

| Security Engine Dest      | 0x3C   | Address of the next         | Figure 68 |

| Ring Address              | UXJC   | destination descriptor.     |           |

| Security Engine Status    |        | Status and configuration    | Figure 69 |

| and Control               | 0x40   | bits for the Security       |           |

|                           |        | Engine.                     |           |

| Security Engine Interrupt | 0x44   | Enables interrupts on       | Figure 70 |

| Enable                    | 0444   | various conditions.         |           |

| Security Engine DMA       | 0x48   | Configures the Security     | Figure 71 |

| Configuration             | 0740   | Engine's DMA units.         |           |

|                           |        | Renders low GPRAM           | Figure 72 |

| PCI Address "OR" Mask     | 0x4C   | memory inaccessible to      |           |

|                           |        | PCI                         |           |

| PCI Interrupt             | 0x50   | Routes MIPS interrupts      | Figure 73 |

|                           | 0400   | to the PCI bus              |           |

|                           |        | Enables the interrupts      | Figure 74 |

| PCI Int. Mask             | 0x54   | defined by the PCI          |           |

|                           |        | Interrupt register          |           |

| MIPS Interrupt            | 0x58   | Routes PCI interrupts to    | Figure 75 |

|                           | 0.100  | the MIPS processor          |           |

|                           |        | Enables the interrupts      | Figure 76 |

| MIPS Int. Mask            | 0x5C   | defined by the MIPS         |           |

|                           |        | Interrupt register          |           |

| RNG Enable                | 0x60   | Enables the random          | Figure 77 |

|                           |        | number generator            |           |

| RNG Config                | 0x64   | Sets RNG parameters         | Figure 78 |

| RNG Data                  | 0x68   | Random data                 | Figure 80 |

| RNG Status                | 0x6C   | RNG state information       | Figure 81 |

|                           |        | Starting address of default | Figure 82 |

| MIPS SDRAM1 Address       | 0x70   | mapping of GPRAM in         |           |

|                           |        | the MIPS address space.     |           |

7811 Network Security Processor

| Register                      | Offset | Description                             | Ref.          |

|-------------------------------|--------|-----------------------------------------|---------------|

| 110510101                     | Gilber | Starting address of the                 | Figure 83     |

|                               | 0x74   | secondary mapping of                    | i igui e os   |

| MIPS SDRAM2 Address           |        | GPRAM in the MIPS                       |               |

|                               |        | address space. Used in                  |               |

|                               |        | multi-7811 systems.                     |               |

| MIPS Group 1 Register         |        | Starting address for the                | Figure 84     |

| Address                       | 0x78   | Group 1 registers in the                |               |

| Address                       |        | MIPS address space                      |               |

| MIPS Group 0 Register         |        | Starting address for the                | Figure 85     |

| Address                       | 0x7C   | Group 0 registers in the                |               |

| 11441400                      |        | MIPS address space                      |               |

| MIPS PCI1 Register            | 0.00   | Starting address for PCI-               | Figure 86     |

| Address                       | 0x80   | mapped accesses in the                  |               |

|                               |        | MIPS address space                      | F. 07         |

| MIDS DC12 Descistor           |        | Starting address for a                  | Figure 87     |

| MIPS PCI2 Register<br>Address | 0x84   | second PCI-mapped<br>region in the MIPS |               |

| Address                       |        | address space                           |               |

|                               |        | Upper address bits to                   | Figure 88     |

| MIPS PCI1 Address             |        | convert a MIPS address                  | I iguie oo    |

| Translation                   | 0x88   | to PCI for the PCI1                     |               |

| Translation                   |        | region                                  |               |

|                               |        | Upper address bits to                   | Figure 89     |

| MIPS PCI2 Address             | 0.00   | convert a MIPS address                  | 8             |

| Translation                   | 0x8C   | to PCI for the PCI2                     |               |

|                               |        | region                                  |               |

|                               |        | MIPS Config – Big/little                | Figure 90     |

| MIPS Config                   | 0x90   | endian selection and                    |               |

|                               |        | interrupt mapping                       |               |

| MIPS Reset                    | 0x94   | Reset bits for the MIPS                 | Figure 91     |

|                               |        | processor                               |               |

| Revision ID                   | 0x98   | Silicon revision                        | Figure 92     |

| EEPROM Data                   | 0x9C   | 32-bit EEPROM data                      | Figure 93     |

| GPDMA1 Source Addr.           | 0xA0   | Source Command                          | Figure 94     |

|                               |        | Pointer for GPDMA1.                     | <b>F</b> : 05 |

| GPDMA2 Source Addr.           | 0xA4   | Source Command                          | Figure 95     |

|                               |        | Pointer for GPDMA2.                     | Eigene 06     |

| GPDMA1 Dest Addr.             | 0xA8   | Dest command pointer for GPDMA1.        | Figure 96     |

|                               |        | Dest command pointer                    | Figure 97     |

| GPDMA2 Dest Addr.             | 0xAC   | for GPDMA2.                             | Figure 97     |

|                               |        | Time-slice control for                  | Figure 98     |

| GPDMA1 2 Arbitration          | 0xB0   | GPDMA1 and                              | 1 15010 70    |

|                               | 0/100  | GPDMA2.                                 |               |

|                               |        | Mode config for                         | Figure 99     |

| GPDMA1 2 Config               | 0xB4   | GPDMA1 and                              | 6             |

| _ 0                           |        | GPDMA2.                                 |               |

| CDDMA1 2 States               | 0      | Interrupt status for                    | Figure        |

| GPDMA1_2 Status               | 0xB8   | GPDMA1 and GPDMA2                       | 100           |

| GPDMA1_2 Interrupt            | 0xBC   | Interrupt enables for                   | Figure        |

| Enable                        | UXDC   | GPDMA1 and GPDMA2                       | 101           |

7811 Network Security Processor

| Register             | Offset | Description                                                             | Ref.       |

|----------------------|--------|-------------------------------------------------------------------------|------------|

| PCI BAR0 Shadow      | 0xC0   | Read Only copy of<br>BAR0 (4KB region<br>holding Group 0<br>registers)  | Figure 102 |

| PCI BAR1 Shadow      | 0xC4   | Read Only copy of<br>BAR1. (4KB region<br>holding Group 1<br>registers) | Figure 103 |

| PCI BAR2 Shadow      | 0xC8   | Read Only copy of<br>BAR2. (Mapped to<br>GPRAM, up to 64 MB in<br>size) | Figure 104 |

| SDRAM Config         | 0xCC   | Read Only copy of SDRAM parameters                                      | Figure 105 |

| GPDMA3 Source Addr.  | 0xD0   | Source Command<br>Pointer for GPDMA3.                                   | Figure 106 |

| GPDMA4 Source Addr.  | 0xD4   | Source Command<br>Pointer for GPDMA4.                                   | Figure 107 |

| GPDMA3 Dest Addr.    | 0xD8   | Dest command pointer for GPDMA3.                                        | Figure 108 |

| GPDMA4 Dest Addr.    | 0xDC   | Dest command pointer for GPDMA4.                                        | Figure 109 |

| GPDMA3_4 Arbitration | 0xE0   | Time-slice config for<br>GPDMA3 and<br>GPDMA4.                          | Figure 110 |

| GPDMA3_4 Config      | 0xE4   | Mode config for<br>GPDMA3 and<br>GPDMA4.                                | Figure 111 |

| GPDMA3_4 Status      | 0xE8   | Interrupt status for<br>GPDMA3 and<br>GPDMA4.                           | Figure 112 |

| GPDMA3_4 Enable      | 0xEC   | Interrupt enables for<br>GPDMA3 and<br>GPDMA4.                          | Figure 113 |

| Global Status        | 0xF0   | Engine, DMA, and interrupt status.                                      | Figure 114 |

| Test-and-Set         | 0xF8   | Test-and-Set semaphore register.                                        | Figure 115 |

Figure 7. Group 1 register summary

#### 2.2.4 Random Number Generator

Public-key cryptography depends on a reliable, high-speed source of random numbers. The 7811 contains a hardware random number generator (RNG) based on internal free-running oscillators whose frequencies drift relative to each other and to the 7811 internal clock. The phase relation of these signals is unpredictable, and this is used to provide a random bit stream. The random bits are mixed cryptographically with internal state derived from previous random bits, updating the internal state. The output mixing function uses this internal state to produce 32-bit random numbers at a programmable rate.

The results are pushed into the *random number FIFO*, which is a 4-element FIFO, 32 bits wide. The FIFO can be read from the RNG Data register.

It is possible to use random numbers more quickly or slowly than they can be generated (hence the FIFO). The Random Number Ready bit in the RNG Status register is set when the random number generator contains at least two random numbers. An interrupt can also be asserted when the Random Number Ready bit is set. If the host underflows the FIFO, the RNG Underflow bit will be set.

On reset, the random number generator is disabled. It must be re-enabled through the RNG Enable register. If the random number FIFO is read while the random number generator is disabled, the result is undefined.

At its maximum speed, the random number generator operates at about 2.8 Mb/s at a 90 MHz clock. For computations refer to Figure 78. RNG Config register.

## 2.2.5 PCI Interface

The PCI interface is a 33 MHz/32-bit PCI bus master designed for maximum-performance DMA transfers.

The PCI interface is generally used by the 7811's four DMA interfaces, with the 7811 as the bus master. GPDMA transfers use 128-byte bursts whenever possible, while the Security Engine DMA units use 64-byte bursts. The 7811 is also an efficient PCI target in situations where the host or another PCI bus master needs to access the 7811's registers or GPRAM. It supports posted writes and a single active delayed read. The 7751-compatible Security Engine is also capable of becoming a PCI bus master.

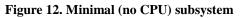

Three base-address registers are used, BAR0-BAR2. BAR0 and BAR1 are used for register access, while BAR2 provides access to GPRAM. In protected mode, access to registers and memory is restricted. See section 5.1 for the PCI memory map.

The PCI configuration space provides 64 bytes of header information to the host system. All header values have reset defaults. Many can be loaded from the external EEPROM. See section 5.4 for the PCI configuration space mapping and section 5.3 for the EEPROM mapping.

The 7811 can assert PCI interrupts under a variety of conditions, and can also route PCI interrupts to the MIPS processor.

## 2.2.6 Local CPU Interface

The CPU interface connects to an optional external processor that controls the 7811. This 32-bit interface is compatible with specified MIPS processors. From the point of view of the MIPS processor, the 7811 is a memory-mapped slave device.

The local MIPS CPU adds intelligence to the security subsystem, relieving the host of low-level tasks. The local CPU is used by the Hi/fn Security Platform software to create a packet-oriented subsystem. The host hands off input packets and session numbers to the security subsystem, and software running on the MIPS CPU issues the appropriate 7811 commands to process the input packet. It then assembles an output packet from the results and sends it back to the host. This greatly reduces the involvement of the host in the operation of the security subsystem, simplifying the host software and reducing PCI bus traffic.

In addition to packet-oriented processing, the MIPS CPU performs subsystem initialization, session setup, and session tear-down.

The MIPS processor can execute code out of memory on its local bus, GPRAM, or PCI memory. Execution from GPRAM or PCI memory degrades the MIPS and 7811 performance and is not recommended for use in systems requiring very high performance.

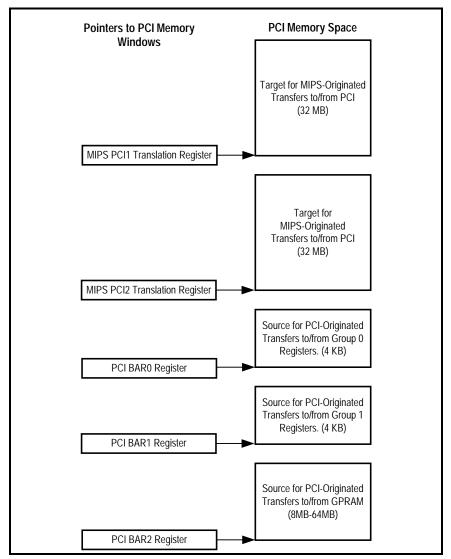

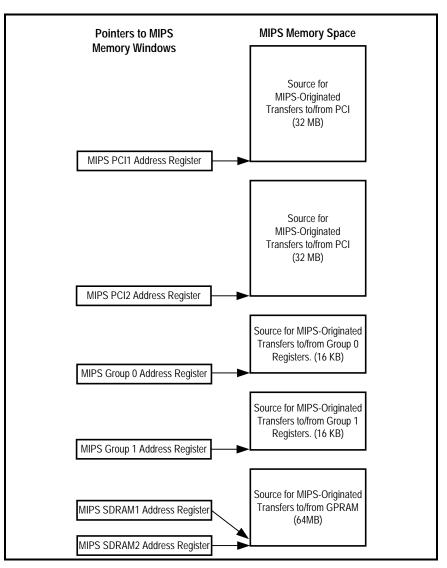

The 7811 memory spaces and functional units are mapped into the MIPS memory space through a set of address pointer registers. See section 5.2 for the MIPS memory map.

The MIPS processor can run in either big-endian or little-endian mode. The MIPS\_BIGENDIAN input on the 7811 informs the 7811 of the endianness of the MIPS CPU.

The 7811 supports fast writes and MIPS-style sub-block bursting. These features are controlled by the MIPS\_Config register. See Figure 90.

MIPS interrupts are supported by the 7811. The 7811 can interrupt the MIPS on a variety of user-selectable conditions.

Supported processors are the R4300 and R4310 from NEC, RV4640 and 64V474 from IDT and the RM5230 from QED.

#### 2.2.7 EEPROM Interface

The EEPROM interface allows the storage of PCI configuration information, export-control information, and system setup information in an external 93C46 EEPROM.

#### 2.2.8 GPRAM Interface

The GPRAM interface controls an external 16-bit SDRAM. GPRAM is used for I/O buffering of both incoming and outgoing packet data. The MIPS processor uses it for data memory and can also use it for program memory. GPRAM contains input and output packet buffers, and the Security Engine's Source, Destination, Command, and Result rings. GPRAM has greater bandwidth and lower latency than the PCI bus, allowing the 7811 to run at higher performance with less bus overhead.

Regions of GPRAM can be made inaccessible to the outside world, placing them inside the 7811's security boundary. The 7811 can support GPRAM to the extent of 64MB.

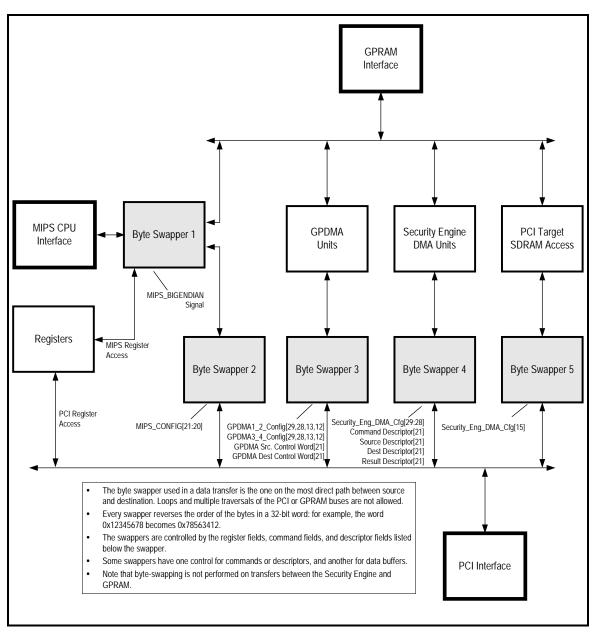

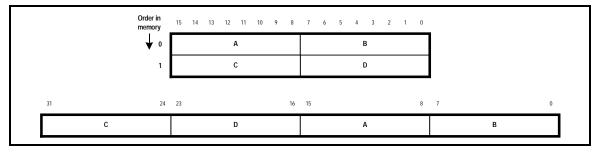

## Big-Endian/Little-Endian Conversion

To support big-endian/little-endian conversion, the 7811 contains five different byte-swapping units. These are shown in Figure 8. Internally, the 7811's Security Engine operates in little-endian mode. The operating principle of 7811 endian-conversion is to store data in GPRAM in little-endian mode, regardless of source. For byte-swapping to occur, the data must flow through a path that includes one of the byte swappers, as show in Figure 8.

The byte swappers are independently controlled, as shown in the diagram. They are affected by register bits, command and descriptor bits, and an input pin, MIPS\_BIGENDIAN. In the case of the GPDMA and Security Engine DMA units, the endianness of data buffers, commands, descriptors, and Write32 transfers are controlled independently.

The byte-swappers do simple endian-conversion. When a byte-swapper is enabled, the order of the bytes within each 32-bit word is reversed. Bits [31:24] become bits [7:0] on output, bits [23:16] become bits [15:8], bits [15:8] become bits [23:16], and bits [7:0] become bits [31:24]. When a byte-swapper is disabled, data passes through unmodified.

## Endianness Override

This affects the MIPS interface. It allows the MIPS processor to access data in either endianness simultaneously, which avoids software byte reordering. The following six registers are affected: SDRAM1 Address, SDRAM2 Address, MIPS Group 1 Address, MIPS Group 0 Address, MIPS PCI1 Address, and MIPS

Page 20

PCI2 Address (Base-1 + 0x70 to Base-1+0x84). Each of these Group-1 registers is affected in the same way. In the production version of the 7811, if bit 0 of any of the above registers is set, then it effectively complements the state of the MIPS\_BIGENDIAN pin for accesses through that register. This provides the ability to utilize a different endianness for each of the six address spaces defined by these registers.

## 2.2.9 Context SDRAM Interface

The context memory interface is another 16-bit SDRAM interface. Context memory contains session context information for the Security Engine. It cannot be accessed directly by the rest of the 7811. The 7811 can support SDRAM to the extent of 64MB.

#### 7811 Network Security Processor

## 3

# **Subsystem Configurations**

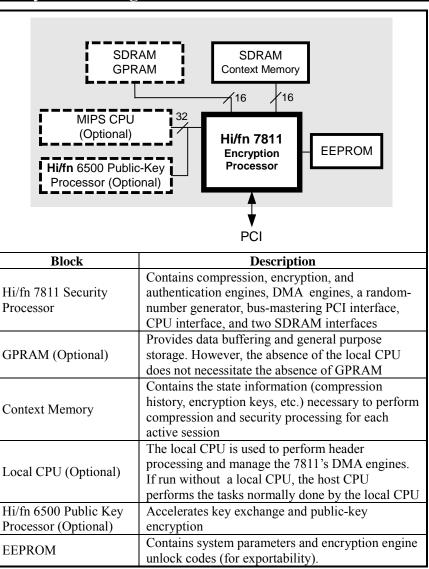

#### Figure 9. Elements of a 7811 subsystem

#### 3.1 Subsystem Variants

#### 3.1.1 Typical Subsystem

#### Figure 10. Typical subsystem

A typical 7811 implementation will make use of all the supported features, using the MIPS CPU for local packet processing and a 50 MHz Hi/fn 6500 for publickey encryption. Such a system can also be made FIPS 140-1, Level 3 compliant if operated in protected mode and rendered physically inaccessible to probing (typically by potting it in plastic).

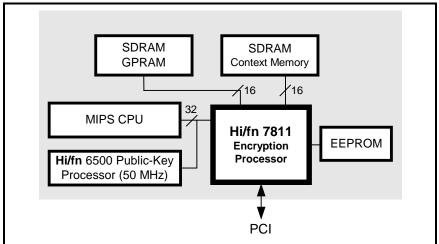

#### 3.1.2 High Performance Subsystem

For maximum performance, two 7811's can be used in the same subsystem, with each serviced by its own MIPS processor. In a two-7811 subsystem, one 7811 is used for incoming packets, and the other for outgoing packets. This is shown in Figure 11. Each 7811 has its own SDRAM and EEPROM interfaces. To the host system, each 7811 is a distinct PCI device, but the host software will see very little difference between single-7811 and multiple-7811 configurations. A 100 MHz Hi/fn 6500 is provided for maximum public-key performance. Like the typical system, the high-performance system can be made FIPS 140-1, Level 3 compliant.

Figure 11. High Performance Subsystem

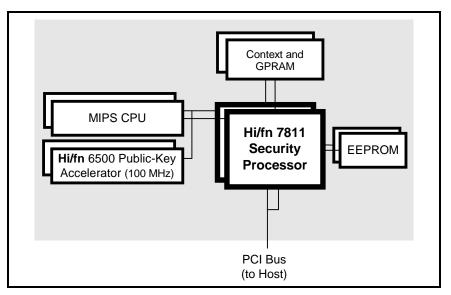

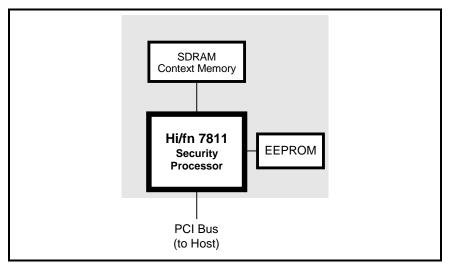

# 3.1.3 Minimal Subsystem (7751 Compatibility Mode)

A low cost implementation might eliminate the local CPU, GPRAM, and the Hi/fn 6500. Such a subsystem would use the host processor to perform all CPU functions. Without the MIPS CPU, the 7811 operates as an enhanced 7751. That is, it provides the same features as the Hi/fn 7751, with the addition of a random number generator, an increase in the maximum number of sessions to 32768, the use of SDRAM for context memory, and higher engine performance. This subsystem cannot be made FIPS 140-1 Level 3 compliant. This configuration is shown in Figure 12. Greater performance would be obtained if GPRAM were added.

(The Security Engine of the 7811 is compatible with the Hi/fn 7751. This means that 7751 compatibility is not a backwards-compatibility mode that is turned on and off, but an integral feature of the device.)

#### 3.1.4 Protected and Unprotected Modes

When the local MIPS CPU is used, the 7811 has two modes of operation: *unprotected mode* and *protected mode*, controlled by the PROTECT# input signal.

*Unprotected mode*. When running in unprotected mode, the full state of the 7811 is accessible across the PCI bus.

**Protected mode.** The goal of protected mode is to render security-relevant data items inaccessible. Such items include encryption keys, session keys, and access control information. In protected mode, very little of the 7811's state is accessible over PCI. Most of the 7811's registers are completely inaccessible (writes to the registers are ignored; reads return zeroes). By default, the 7811's GPRAM is inaccessible to the host. It can be partially or completely unlocked by the MIPS processor by setting bits [13:12] of the Security Engine DMA Configuration register. The host is left with almost no access to the 7811 except for the ability to tell the 7811 where to find input and output command and data buffers. In short, protected mode gives the 7811 a *security boundary*, a barrier that renders security-relevant data items inaccessible even to software that has gained complete control over the host.

The local MIPS processor retains full access to the 7811 at all times, and serves as a firewall. The software conventions used by Hi/fn are designed with protected mode in mind.

*FIPS Compliance.* The 7811 was designed with FIPS 140-1 Level 3 compliance in mind. FIPS 140-1 is an NIST standard for cryptographic modules. Such compliance requires security measures on a variety of levels, including physical barriers to data theft. While some of these measures depend on the system designer, the 7811 facilitates FIPS 140-1 Level 3 compliance by including all of the necessary circuit-level features.

Protected mode and FIPS 140-1 Level 3 compliance should not be confused with one another.

#### 4

# **Signal Description**

The 7811's signals are listed on the following pages.

If the MIPS processor is not used, the MIPS interface pins should be terminated as shown in Figure 14. If GPRAM is not used, the GPRAM interface pins should be left floating.

| Signal                | Туре           | Polarity    | Description                                                                                                                                                   |  |  |

|-----------------------|----------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Context SDRAM Signals |                |             |                                                                                                                                                               |  |  |

| CADDR[12:0]           | Output         | -           | Context SDRAM multiplexed row/column address output bus.                                                                                                      |  |  |

| CBA[1:0]              | Output         | -           | Context SDRAM bank-select outputs.                                                                                                                            |  |  |

| CCAS#                 | Output         | Active-Low  | Context SDRAM column-address strobe output.                                                                                                                   |  |  |

| CCLK                  | Output         | Rising Edge | Context SDRAM clock output.                                                                                                                                   |  |  |

| CCS#                  | Output         | Active-Low  | Context SDRAM chip-select output                                                                                                                              |  |  |

| CDATA[15:0]           | I/O            | -           | Context SDRAM data I/O bus.                                                                                                                                   |  |  |

| CDQMH                 | Output         | Active-High | Context SDRAM data mask output for bits 15:8.                                                                                                                 |  |  |

| CDQML                 | Output         | Active-High | Context SDRAM data mask output for bits 7:0.                                                                                                                  |  |  |

| CRAS#                 | Output         | Active-Low  | Context SDRAM row-address strobe.                                                                                                                             |  |  |

| CWE#                  | Output         | Active-Low  | Context SDRAM write enable.                                                                                                                                   |  |  |

| EEPROM Signals        | EEPROM Signals |             |                                                                                                                                                               |  |  |

| EEPROM_CS             | Output         | Active-High | EEPROM chip select                                                                                                                                            |  |  |

| EEPROM_DI             | Input          | Active-High | EEPROM data in                                                                                                                                                |  |  |

| EEPROM_DO             | Output         | Active-High | EEPROM data out                                                                                                                                               |  |  |

| EEPROM_SK             | Output         | Rising Edge | e EEPROM clock                                                                                                                                                |  |  |

| MIPS Signals          |                |             |                                                                                                                                                               |  |  |

| MIPS_AD[31:0]         | I/O            | -           | MIPS SysAD bus. Multiplexed 32-bit address/data bus for<br>the MIPS processor.                                                                                |  |  |

| MIPS_BIGENDIAN        | Input          | Active-High | *                                                                                                                                                             |  |  |

| MIPS_CLK              | Input          | Rising Edge | Clock input. This is the MIPS bus clock. A frequency-<br>doubled clock internally derived from MIPS_CLK drives t<br>Security Engine and the SDRAM interfaces. |  |  |

| MIPS_CMD[8:0]         | I/O            | -           | MIPS SysCmd bus. Carries command/data identifier code<br>between the MIPS processor and the 7811.                                                             |  |  |

| MIPS_COLDRESET#       | Output         | Active-Low  | MIPS ColdReset output.                                                                                                                                        |  |  |

| MIPS_EOK#             | Output         | Active-Low  | is capable of accepting a processor request.                                                                                                                  |  |  |

| MIPS_EOK_EXT#         | Input          | Active-Low  | MIPS external EOK input. EOK signal for external (non-<br>7811) accesses.                                                                                     |  |  |

| MIPS_EREQ#            | Output         | Active-Low  | MIPS EReq output. Asserted when the 7811 is requesting the MIPS interface bus.                                                                                |  |  |

| Signal         | Туре                     | Polarity    | Description                                                                                                                       |  |

|----------------|--------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------|--|

| MIPS_EVALID#   | Output                   | Active-Low  | MIPS EValid output. Asserted when the 7811 is driving a valid address or valid data on the MIPS_SYSAD[31:0] bus                   |  |

| MIPS_INT[2:0]# | Output                   | Active-Low  | MIPS interrupt bus. Three independent interrupt request pins.                                                                     |  |

| MIPS_PMASTER#  | Input                    | Active-Low  | MIPS PMaster input. Asserted when the MIPS processor is the master on the MIPS bus.                                               |  |

| MIPS_PREQ#     | Input                    | Active-Low  | MIPS PReq. Asserted when the MIPS processor is requesting<br>the MIPS bus.                                                        |  |

| MIPS_PVALID#   | Input                    | Active-Low  | MIPS PValid input. Asserted when the MIPS processor is<br>driving a valid address or valid data onto the<br>MIPS_SYSAD[31:0] bus. |  |

| MIPS_RESET#    | Output                   | Active-Low  | MIPS reset output. Initiates a soft reset of the MIPS processor.                                                                  |  |

| GPRAM Signals  |                          |             |                                                                                                                                   |  |

| PADDR[12:0]    | Output                   | -           | GPRAM multiplexed row/column address output bus.                                                                                  |  |

| PBA[1:0]       | Output                   | -           | GPRAM bank-select outputs.                                                                                                        |  |

| PCAS#          | Output                   | Active-Low  | GPRAM column-address strobe output.                                                                                               |  |

| PCLK           | Output                   | Rising Edge | GPRAM clock output.                                                                                                               |  |

| PCS#           | Output                   | Active-Low  | GPRAM chip-select output                                                                                                          |  |

| PDATA[15:0]    | I/O                      | -           | GPRAM data I/O bus.                                                                                                               |  |

| PDQMH          | Output                   | Active-High | GPRAM data mask output for bits 15:8.                                                                                             |  |

| PDQML          | Output                   | Active-High | GPRAM data mask output for bits 7:0.                                                                                              |  |

| PRAS#          | Output                   | Active-Low  | GPRAM row-address strobe.                                                                                                         |  |

| PWE#           | Output                   | Active-Low  | GPRAM write enable.                                                                                                               |  |

| PCI Signals    | •                        | •           |                                                                                                                                   |  |

| PCI_AD[31:0]   | I/O                      | -           | PCI address/data bus.                                                                                                             |  |

| PCI_CBE[3:0]#  | I/O                      | Active-Low  | PCI command/byte-enable bits.                                                                                                     |  |

| PCI_CLK        | Input                    | Rising Edge | PCI clock. This clock is completely asynchronous to MIPS_CLK.                                                                     |  |

| PCI_DEVSEL#    | I/O                      | Active-Low  | -                                                                                                                                 |  |

| PCI_FRAME#     | I/O                      | Active-Low  | PCI cycle frame.                                                                                                                  |  |

| PCI_GNT#       | Input                    | Active-Low  | PCI bus grant.                                                                                                                    |  |

| PCI_IDSEL#     | Input                    | Active-Low  | PCI initialization device select.                                                                                                 |  |

| PCI_INTA#      | Open-<br>Drain<br>Output | Active-Low  | PCI interrupt request.                                                                                                            |  |

| PCI_IRDY#      | I/O                      | Active-Low  | PCI initiator ready.                                                                                                              |  |

| PCI_LOCK#      | I/O                      | Active-Low  | PCI bus lock.                                                                                                                     |  |

| PCI_PAR        | I/O                      | Active-High | PCI bus parity                                                                                                                    |  |

| Signal                | Туре   | Polarity   | Description                                                                                                                                                                                                                                      |  |

|-----------------------|--------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PCI_PERR#             | I/O    | Active-Low | PCI bus parity error.                                                                                                                                                                                                                            |  |

| PCI_REQ#              | Output | Active-Low | PCI bus request.                                                                                                                                                                                                                                 |  |

| PCI_RST#              | Input  | Active-Low | PCI reset.                                                                                                                                                                                                                                       |  |

| PCI_STOP#             | I/O    | Active-Low | PCI transfer stop.                                                                                                                                                                                                                               |  |

| PCI_TRDY#             | I/O    | Active-Low | PCI target ready.                                                                                                                                                                                                                                |  |

| PLL Signals           |        |            |                                                                                                                                                                                                                                                  |  |

| PLL_AGD               | Ground | -          | PLL analog ground. Should be isolated from digital ground.                                                                                                                                                                                       |  |

| PLL_DGN               | Ground | -          | PLL digital ground. Should be connected directly to VSS.                                                                                                                                                                                         |  |

| PLL_DVD               | Power  | -          | PLL digital VDD. Should be connected directly to VDD.                                                                                                                                                                                            |  |

| PLL_VAA               | Power  | -          | PLL analog VDD. Should be isolated from digital VDD.                                                                                                                                                                                             |  |

| Test Signals          |        | 1          |                                                                                                                                                                                                                                                  |  |

| TEST_PLLIN0           | Input  | -          | Reserved. Must be pulled down to VSS through a 1 K $\Omega$ resistor                                                                                                                                                                             |  |

| TEST_PLLIN1           | Input  | _          | Reserved. Must be pulled down to VSS through a 1 K $\Omega$ resistor                                                                                                                                                                             |  |

| TEST_PLLOUT0          | Output | -          | PLL lock detect.                                                                                                                                                                                                                                 |  |

| TEST_PLLOUT1          | Output |            | Test output. Maybe left unconnected or brought to a test point                                                                                                                                                                                   |  |

| TEST_PLLOUT2          | NC     |            | No function currently                                                                                                                                                                                                                            |  |