### Intel386™ SXSA EMBEDDED MICROPROCESSOR

- Static Intel386<sup>™</sup> CPU Core

- Low Power Consumption

- Operating Power Supply 4.5V to 5.5V - 25 and 33 MHz 4.75V to 5.25V - 40 MHz

- Operating Frequency SA-40 = 40 MHz

SA-33 = 33 MHz

SA-25 = 25 MHz

- Clock Freeze Mode Allows Clock Stopping at Any Time

- Full 32-bit Internal Architecture

- 8-, 16-, 32-bit Data Types

- 8 General Purpose 32-bit Registers

- Runs Intel386 Architecture Software in a Cost-effective, 16-bit Hardware Environment

- Runs Same Applications and Operating Systems as the Intel386 SX and Intel386 DX Processors

- Object Code Compatible with 8086, 80186, 80286, and Intel386 Processors

- TTL-Compatible Inputs

- High-performance 16-bit Data Bus

Two-clock Bus Cycles

- Address Pipelining Allows Use of Slower, Inexpensive Memories

- Integrated Memory Management Unit (MMU)

- Virtual Memory Support

- Optional On-chip Paging

- 4 Levels of Hardware-Enforced Protection

- MMU Fully Compatible with 80286 and Intel386 DX Processors

- Virtual 8086 Mode Allows Execution of 8086 Software in a Protected and Paged System

- Large Uniform Address Space

- 16 Megabyte Physical

- 64 Terabyte Virtual

- 4 Gigabyte Maximum Segment Size

- Numerics Support Intel387<sup>™</sup> SX and Intel387<sup>™</sup> SL Math Coprocessors

- On-chip Debugging Support Including Breakpoint Registers

- Complete System Development Support

- High Speed CHMOS Technology

- 100-Pin Plastic Quad Flatpack Package

The Intel386<sup>™</sup> SXSA embedded microprocessor is a 5-volt, 32-bit, fully static CPU with a 16-bit external data bus and a 24-bit external address bus. The Intel386 SXSA CPU brings the vast software library of the Intel386 architecture to embedded systems. It provides the performance benefits of 32-bit programming with the cost savings associated with 16-bit hardware systems.

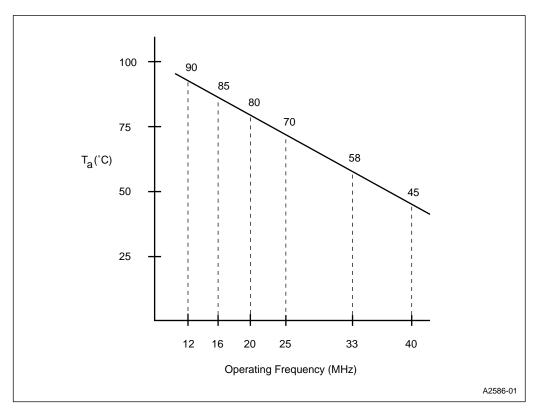

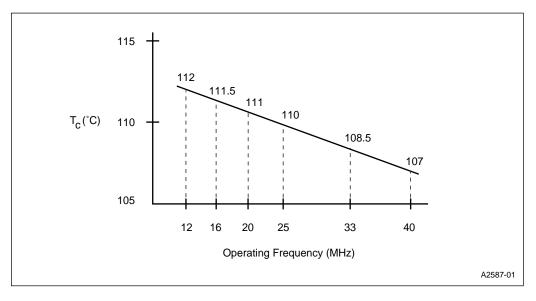

The Intel386 SXSA microprocessor is manufactured on Intel's 0.8-micron CHMOS V process. This process provides high performance and low power consumption for power-sensitive applications. Figure 3 and Figure 4 illustrate the flexibility of low power devices with respect to temperature and frequency relationships.

Information in this document is provided solely to enable use of Intel products. Intel assumes no liability whatsoever, including infringe-ment of any patent or copyright, for sale and use of Intel products except as provided in Intel's Terms and Conditions of Sale for such products. Information contained herein supersedes previously published specifications on these devices from Intel.

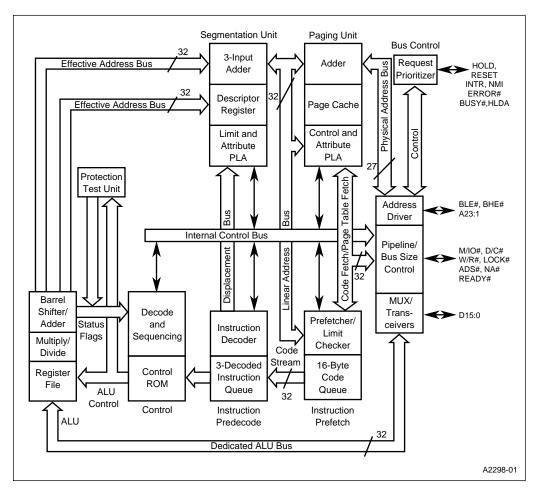

Figure 1. Intel386<sup>™</sup> SXSA Microprocessor Block Diagram

### 1.0 PIN ASSIGNMENT

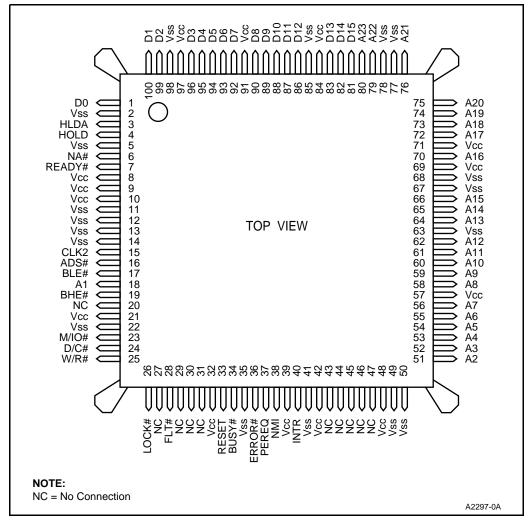

Figure 2. Intel386™ SXSA Microprocessor Pin Assignment (PQFP)

| Pin | Symbol          | Pin | Symbol          | Pin | Symbol          | Pin | Symbol          |

|-----|-----------------|-----|-----------------|-----|-----------------|-----|-----------------|

| 1   | D0              | 26  | LOCK#           | 51  | A2              | 76  | A21             |

| 2   | V <sub>SS</sub> | 27  | NC              | 52  | A3              | 77  | V <sub>SS</sub> |

| 3   | HLDA            | 28  | FLT#            | 53  | A4              | 78  | V <sub>SS</sub> |

| 4   | HOLD            | 29  | NC              | 54  | A5              | 79  | A22             |

| 5   | V <sub>SS</sub> | 30  | NC              | 55  | A6              | 80  | A23             |

| 6   | NA#             | 31  | NC              | 56  | A7              | 81  | D15             |

| 7   | READY#          | 32  | V <sub>CC</sub> | 57  | V <sub>CC</sub> | 82  | D14             |

| 8   | V <sub>CC</sub> | 33  | RESET           | 58  | A8              | 83  | D13             |

| 9   | V <sub>CC</sub> | 34  | BUSY#           | 59  | A9              | 84  | V <sub>CC</sub> |

| 10  | V <sub>CC</sub> | 35  | V <sub>SS</sub> | 60  | A10             | 85  | V <sub>SS</sub> |

| 11  | V <sub>SS</sub> | 36  | ERROR#          | 61  | A11             | 86  | D12             |

| 12  | V <sub>SS</sub> | 37  | PEREQ           | 62  | A12             | 87  | D11             |

| 13  | V <sub>SS</sub> | 38  | NMI             | 63  | V <sub>SS</sub> | 88  | D10             |

| 14  | V <sub>SS</sub> | 39  | V <sub>CC</sub> | 64  | A13             | 89  | D9              |

| 15  | CLK2            | 40  | INTR            | 65  | A14             | 90  | D8              |

| 16  | ADS#            | 41  | V <sub>SS</sub> | 66  | A15             | 91  | V <sub>CC</sub> |

| 17  | BLE#            | 42  | V <sub>CC</sub> | 67  | V <sub>SS</sub> | 92  | D7              |

| 18  | A1              | 43  | NC              | 68  | V <sub>SS</sub> | 93  | D6              |

| 19  | BHE#            | 44  | NC              | 69  | V <sub>CC</sub> | 94  | D5              |

| 20  | NC              | 45  | NC              | 70  | A16             | 95  | D4              |

| 21  | V <sub>CC</sub> | 46  | NC              | 71  | V <sub>CC</sub> | 96  | D3              |

| 22  | V <sub>SS</sub> | 47  | NC              | 72  | A17             | 97  | V <sub>CC</sub> |

| 23  | M/IO#           | 48  | V <sub>CC</sub> | 73  | A18             | 98  | V <sub>SS</sub> |

| 24  | D/C#            | 49  | V <sub>SS</sub> | 74  | A19             | 99  | D2              |

| 25  | W/R#            | 50  | V <sub>SS</sub> | 75  | A20             | 100 | D1              |

Table 1. Pin Assignment

#### 2.0 **PIN DESCRIPTIONS**

Table 2 lists the Intel386 SXSA microprocessor pin descriptions. The following definitions are used in the pin descriptions:

- # The named signal is active low.

- Input signal. L

- O Output signal.I/O Input and output signal.

- Power pin. Ρ

- G Ground pin.

| Table 2. P | n Descriptions |

|------------|----------------|

|------------|----------------|

| Symbol | Туре | Pin                                               | Name and Function                                                                                                                                                                                                                                                  |  |  |  |

|--------|------|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| A23:1  | 0    | 80–79, 76–72,<br>70, 66–64<br>62–58, 56–51,<br>18 | Address Bus outputs physical memory or port I/O addresses                                                                                                                                                                                                          |  |  |  |

| ADS#   | 0    | 16                                                | Address Status indicates that the processor is driving a valid bus-cycle definition and address onto its pins (W/R#, D/C#, M/IO#, BHE#, BLE#, and A23:1).                                                                                                          |  |  |  |

| BHE#   | 0    | 19                                                | Byte High Enable indicates that the processor is transferring a high data byte.                                                                                                                                                                                    |  |  |  |

| BLE#   | 0    | 17                                                | Byte Low Enable indicates that the processor is transferring a low data byte.                                                                                                                                                                                      |  |  |  |

| BUSY#  | I    | 34                                                | Busy indicates that the math coprocessor is busy.                                                                                                                                                                                                                  |  |  |  |

| CLK2   | I    | 15                                                | CLK2 provides the fundamental timing for the device.                                                                                                                                                                                                               |  |  |  |

| D/C#   | 0    | 24                                                | <b>Data/Control</b> indicates whether the current bus cycle is a data cycle (memory or I/O) or a control cycle (interrupt acknowledge, halt, or code fetch). When D/C# is high, the bus cycle is a data cycle; when D/C# is low, the bus cycle is a control cycle. |  |  |  |

| D15:0  | I/O  | 81–83, 86–90,<br>92–96, 99–100,<br>1              | <b>Data Bus</b> inputs data during memory read, I/O read, and interrupt acknowledge cycles and outputs data during memory and I/O write cycles.                                                                                                                    |  |  |  |

| ERROR# | I    | 36                                                | <b>Error</b> indicates that the math coprocessor has an error condition.                                                                                                                                                                                           |  |  |  |

| FLT#   | I    | 28                                                | <b>Float</b> forces all bidirectional and output signals, including HLDA, to a high-impedance state.                                                                                                                                                               |  |  |  |

| HLDA   | 0    | 3                                                 | Bus Hold Acknowledge indicates that the CPU has surren-<br>dered control of its local bus to another bus master.                                                                                                                                                   |  |  |  |

| HOLD   | I    | 4                                                 | Bus Hold Request allows another bus master to request con-<br>trol of the local bus.                                                                                                                                                                               |  |  |  |

| INTR   | I    | 40                                                | <b>Interrupt Request</b> is a maskable input that causes the CPU to suspend execution of the current program and then execute an interrupt acknowledge cycle.                                                                                                      |  |  |  |

| Symbol          | Туре | Pin                                                              | Name and Function                                                                                                                                                                                                      |

|-----------------|------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LOCK#           | 0    | 26                                                               | <b>Bus Lock</b> prevents other system bus masters from gaining control of the system bus while it is active (low).                                                                                                     |

| M/IO#           | 0    | 23                                                               | <b>Memory/IO</b> indicates whether the current bus cycle is a mem-<br>ory cycle or an input/output cycle. When M/IO# is high, the<br>bus cycle is a memory cycle; when M/IO# is low, the bus cycle<br>is an I/O cycle. |

| NA#             | 1    | 6                                                                | Next Address requests address pipelining.                                                                                                                                                                              |

| NC              |      | 20, 27, 29–31,<br>43–47                                          | <b>No Connection</b> should always be left unconnected. Connecting a NC pin may cause the processor to malfunction or cause your application to be incompatible with future steppings of the device.                   |

| NMI             | I    | 38                                                               | <b>Nonmaskable Interrupt Request</b> is a nonmaskable input<br>that causes the CPU to suspend execution of the current pro-<br>gram and execute an interrupt acknowledge function.                                     |

| PEREQ           | I    | 37                                                               | <b>Processor Extension Request</b> indicates that the math coprocessor has data to transfer to the processor.                                                                                                          |

| READY#          | I    | 7                                                                | <b>Bus Ready</b> indicates that the current bus cycle is finished and<br>the external device is ready to accept more data from the pro-<br>cessor.                                                                     |

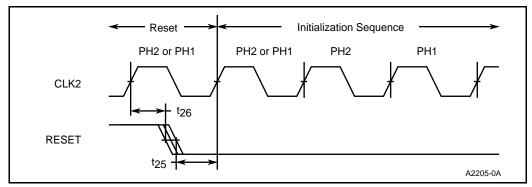

| RESET           | I    | 33                                                               | <b>Reset</b> suspends any operation in progress and places the processor into a known reset state.                                                                                                                     |

| W/R#            | 0    | 25                                                               | <b>Write/Read</b> indicates whether the current bus cycle is a write cycle or a read cycle. When W/R# is high, the bus cycle is a write cycle; when W/R# is low, it is a read cycle.                                   |

| V <sub>CC</sub> | P    | 8–10, 21, 32,<br>39, 42, 48, 57,<br>69, 71, 84, 91,<br>97        | System Power provides the nominal DC supply input.                                                                                                                                                                     |

| V <sub>SS</sub> | G    | 2, 5, 11–14, 22<br>35, 41, 49–50,<br>63, 67–68,<br>77–78, 85, 98 | <b>System Ground</b> provides the 0V connection from which all inputs and outputs are measured.                                                                                                                        |

Table 2. Pin Descriptions (Continued)

### 3.0 DESIGN CONSIDERATIONS

This section describes the Static Intel386 SXSA microprocessor instruction set, component and revision identifier, and package thermal specifications.

### 3.1. Instruction Set

The Static Intel386 SXSA microprocessor uses the same instruction set as the dynamic Intel386 SX microprocessor. However, the Static Intel386 SXSA microprocessor requires more clock cycles than the dynamic Intel386 SX microprocessor to execute some instructions. Table 4 lists these instructions and the Static Intel386 SXSA microprocessor execution times. For the equivalent dynamic Intel386 SX microprocessor execution times. For the equivalent dynamic Intel386 SX microprocessor execution times, refer to the "Instruction Set Clock Count Summary" table in the Intel386<sup>TM</sup> SX Microprocessor</sup> data sheet (order number 240187).

### 3.2. Component and Revision Identifier

To assist users, the microprocessor holds a component identifier and revision identifier in its DX register after reset. The upper 8 bits of DX hold the component identifier, 23H. (The lower nibble, 3H, identifies the Intel386 architecture, while the upper nibble, 2H, identifies the second member of the Intel386 microprocessor family.)

The lower 8 bits of DX hold the revision level identifier. The revision identifier will, in general, chronologically track those component steppings that are intended to have certain improvements or distinction from previous steppings. The revision identifier will track that of the Intel386 CPU whenever possible. However, the revision identifier value is not guaranteed to change with every stepping revision or to follow a completely uniform numerical sequence, depending on the type or intent of the revision or the manufacturing materials required to be changed. Intel has sole discretion over these characteristics of the component. The initial revision identifier for the Static Intel386 SXSA microprocessor is 09H.

### 3.3. Package Thermal Specifications

Static Intel386 SXSA microprocessor is specified for operation with case temperature ( $T_{CASE}$ ) as specified in the "DC SPECIFICATIONS" on page 9. The case temperature can be measured in any environment to determine whether the microprocessor is within the specified operating range. The case temperature should be measured at the center of the top surface opposite the pins.

An increase in the ambient temperature (T<sub>A</sub>) causes a proportional increase in the case temperature (T<sub>CASE</sub>) and the junction temperature (T<sub>J</sub>). See Figures 3 and Figures 4 for case and ambient temperature relationships to frequency. A packaged device produces thermal resistance between junction and case temperatures ( $\theta_{JC}$ ) and between junction and ambient temperatures ( $\theta_{JA}$ ). The relationships between the temperature and thermal resistance parameters are expressed by these equations (P = power dissipated as heat = V<sub>CC</sub> × I<sub>CC</sub>):

- 1.  $T_J = T_{CASE} + P \times \theta_{JC}$

- 2.  $T_A = T_J P \times \theta_{JA}$

- 3.  $T_{CASE} = T_A + P \times [\theta_{JA} \theta_{JC}]$

A safe operating temperature can be calculated from equation 1 by using the maximum safe T<sub>J</sub> of 115° C, the maximum power drawn by the chip in the specific design, and the  $\theta_{JC}$  value from Table 3. The  $\theta_{JA}$  value depends on the airflow (measured at the top of the chip) provided by the system ventilation. The  $\theta_{JA}$  values are given for reference only and are not guaranteed.

Table 3. Thermal Resistances (0°C/W) ØJA, ØJC

| Pkg      | ۵                    | $\boldsymbol{\theta}_{\text{JA}}$ versus Airflow (ft/min) |      |      |  |  |  |

|----------|----------------------|-----------------------------------------------------------|------|------|--|--|--|

| FKY      | $\theta_{\text{JC}}$ | 0                                                         | 100  | 200  |  |  |  |

| 100 PQFP | 5.1                  | 46.0                                                      | 44.8 | 41.2 |  |  |  |

|                                     |                               | Clock Count                               |                                               |  |  |  |  |  |  |

|-------------------------------------|-------------------------------|-------------------------------------------|-----------------------------------------------|--|--|--|--|--|--|

| Instruction                         | Virtual 8086 Mode<br>(Note 1) | Real Address Mode<br>or Virtual 8086 Mode | Protected Virtual<br>Address Mode<br>(Note 3) |  |  |  |  |  |  |

| POPA                                |                               | 28                                        | 35                                            |  |  |  |  |  |  |

| IN:<br>Fixed Port<br>Variable Port  | 27<br>28                      | 14<br>15                                  | 7/29<br>8/29                                  |  |  |  |  |  |  |

| OUT:<br>Fixed Port<br>Variable Port | 27<br>28                      | 14<br>15                                  | 7/29<br>9/29                                  |  |  |  |  |  |  |

| INS                                 | 30                            | 17                                        | 9/32                                          |  |  |  |  |  |  |

| OUTS                                | 31                            | 18                                        | 10/33                                         |  |  |  |  |  |  |

| REP INS                             | 31+6n (Note 2)                | 17+6n (Note 2)                            | 10+6n/32+6n (Note 2)                          |  |  |  |  |  |  |

| REP OUTS                            | 30+8n (Note 2)                | 16+8n (Note 2)                            | 10+8n/31+8n (Note 2)                          |  |  |  |  |  |  |

| HLT                                 |                               | 7                                         | 7                                             |  |  |  |  |  |  |

| MOV C0, reg                         |                               | 10                                        | 10                                            |  |  |  |  |  |  |

#### Table 4. Intel386™ SXSA Microprocessor Instruction Execution Times (in Clock Counts)

#### NOTES:

The clock count values in this column apply if I/O permission allows I/O to the port in virtual 8086 mode. If the I/O bit map denies permission, exception fault 13 occurs; see clock counts for the INT 3 instruction in the "Instruction Set Clock Count Summary" table in the Intel386<sup>™</sup> SX Microprocessor data sheet (order number 240187).

2. n = the number of times repeated.

3. When two clock counts are listed, the smaller value refers to a register operand and the larger value refers to a memory operand.

### 4.0 DC SPECIFICATIONS

#### **ABSOLUTE MAXIMUM RATINGS\***

| Storage Temperature                            | –65°C to +150°C         |

|------------------------------------------------|-------------------------|

| Case Temperature Under Bias                    | 65°C to +112°C          |

| Supply Voltage with Respect to V <sub>SS</sub> | –0.5V to 6.5V           |

| Voltage on Other Pins                          | 0.5V to $V_{CC}$ + 0.5V |

#### **OPERATING CONDITIONS\***

$\label{eq:V_CC} \begin{array}{l} \text{(Digital Supply Voltage - 25 and 33 MHz)} & ...4.5V to 5.5V \\ \text{V}_{\text{CC}} \left( \text{Digital Supply Voltage - 40 MHz} \right) & ....4.75V to 5.25V \\ \text{T}_{\text{CASE}} \text{ minimum (Case Temperature Under Bias)} & ..... 0^{\circ}\text{C} \\ \text{T}_{\text{CASE}} \text{ maximum} & .... \text{see Figure 4} \\ \text{Operating Frequency} & .... 0 \text{ MHz to 40 MHz} \end{array}$

**NOTICE**: This document contains information on products in the sampling and initial production phases of development. The specifications are subject to change without notice. Verify with your local Intel Sales office that you have the latest data sheet before finalizing a design.

\*WARNING: Stressing the device beyond the "Absolute Maximum Ratings" may cause permanent damage. These are stress ratings only. Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.

| Symbol           | Parameter                                                                                                            | Min.                         | Max.                  | Unit           | Test Condition                                                           |

|------------------|----------------------------------------------------------------------------------------------------------------------|------------------------------|-----------------------|----------------|--------------------------------------------------------------------------|

| V <sub>IL</sub>  | Input Low Voltage                                                                                                    | -0.3                         | +0.8                  | V              |                                                                          |

| V <sub>IH</sub>  | Input High Voltage                                                                                                   | 2.0                          | V <sub>CC</sub> + 0.3 | V              |                                                                          |

| V <sub>ILC</sub> | CLK2 Input Low Voltage                                                                                               | -0.3                         | +0.8                  | V              |                                                                          |

| V <sub>IHC</sub> | CLK2 Input High Voltage                                                                                              | V <sub>CC</sub> - 0.8        | V <sub>CC</sub> + 0.3 | V              |                                                                          |

| V <sub>OL</sub>  | Output Low Voltage                                                                                                   |                              | 0.45                  | V              | I <sub>OL</sub> = 5 mA                                                   |

| V <sub>OH</sub>  | Output High Voltage                                                                                                  | 2.4<br>V <sub>CC</sub> – 0.5 |                       | V<br>V         | I <sub>OH</sub> = -1 mA<br>I <sub>OH</sub> = -0.2 mA                     |

| l <sub>u</sub>   | Input Leakage Current<br>(for all pins except PEREQ,<br>BUSY#, FLT#, ERROR#)                                         |                              | ±15                   | μA             | $0 \le V_{IN} \le V_{CC}$                                                |

| Ι <sub>ΙΗ</sub>  | Input Leakage Current<br>(PEREQ)                                                                                     |                              | 150                   | μA             | V <sub>IH</sub> = 2.4V (Note 1)                                          |

| I <sub>IL</sub>  | Input Leakage Current<br>(BUSY#, FLT#, ERROR#)                                                                       |                              | -120                  | μA             | V <sub>IL</sub> = 0.45V (Note2)                                          |

| I <sub>LO</sub>  | Output Leakage Current                                                                                               |                              | ±15                   | μA             | $0.45V \le V_{OUT} \le V_{CC}$                                           |

| I <sub>CC</sub>  | Supply Current<br>CLK2 = 80 MHz, CLK = 40<br>MHz<br>CLK2 = 66 MHz, CLK = 33<br>MHz<br>CLK2 = 50 MHz, CLK = 25<br>MHz |                              | 275<br>225<br>175     | mA<br>mA<br>mA | (Notes 3, 4)<br>typical = 200 mA<br>typical = 175 mA<br>typical = 140 mA |

| I <sub>CCF</sub> | Standby Current (Freeze Mode)                                                                                        |                              | 150                   | μA             | typical = 10 µA (Notes 3 4)                                              |

| C <sub>IN</sub>  | Input Capacitance                                                                                                    |                              | 10                    | pF             | F <sub>C</sub> = 1 MHz (Note 5)                                          |

| C <sub>OUT</sub> | Output or I/O Capacitance                                                                                            |                              | 12                    | pF             | F <sub>C</sub> = 1 MHz (Note 5)                                          |

| C <sub>CLK</sub> | CLK2 Capacitance                                                                                                     |                              | 20                    | pF             | F <sub>C</sub> = 1 MHz (Note 5)                                          |

#### Table 5. DC Characteristics

#### NOTES:

1. PEREQ input has an internal weak pull-down resistor.

2. BUSY#, FLT# and ERROR# inputs each have an internal weak pull-up resistor.

3.  $I_{CC}$  max measurement at worst-case frequency,  $V_{CC},$  and temperature with reset active.

4. I<sub>CC</sub> typical and I<sub>CCF</sub> typical are measured at nominal V<sub>CC</sub> and are not fully tested.

5. Not fully tested.

Figure 3. Ambient Temperature vs. Frequency at Zero Air Flow and  $T_{\rm J}$  = 115° C

Figure 4. Case Temperature vs. Frequency at  $T_{\rm J}$  = 115° C

### 5.0 AC SPECIFICATIONS

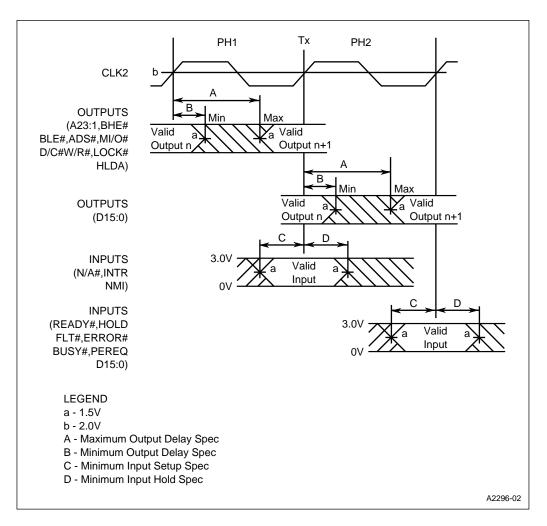

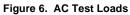

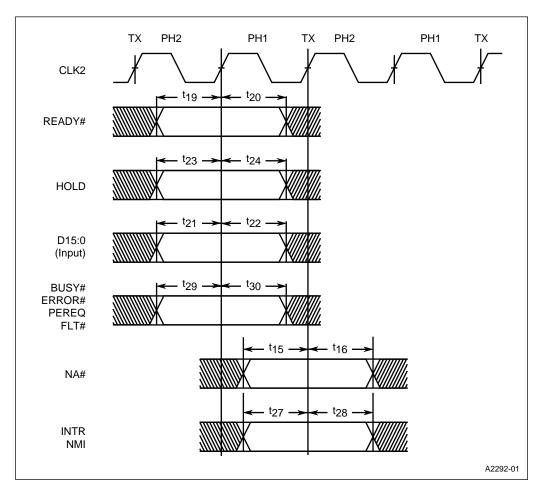

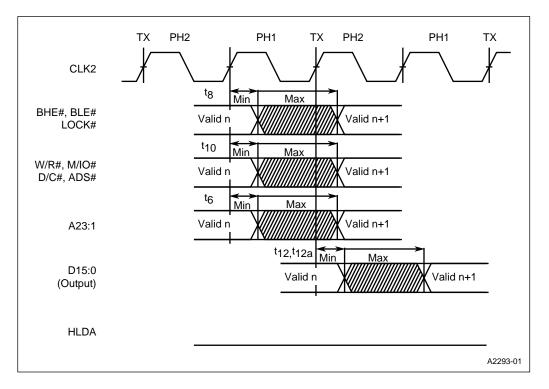

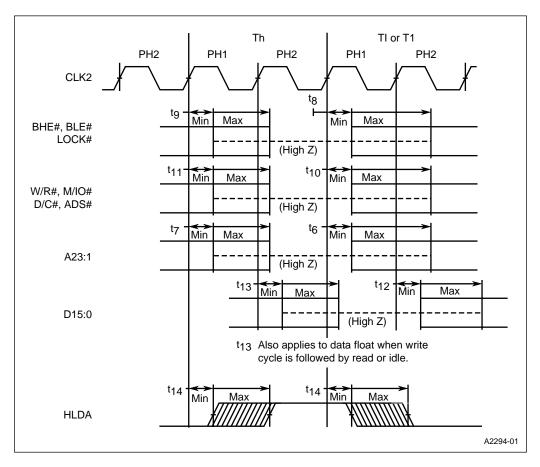

Table 6 lists output delays, input setup requirements, and input hold requirements. All AC specifications are relative to the CLK2 rising edge crossing the 2.0V level.

Figure 5 shows the measurement points for AC specifications. Inputs must be driven to the indicated voltage levels when AC specifications are measured. Output delays are specified with minimum and maximum limits measured as shown. The minimum delay times are hold times provided to external circuitry. Input setup and hold times are specified as minimums, defining the smallest

acceptable sampling window. Within the sampling window, a synchronous input signal must be stable for correct operation.

Outputs ADS#, W/R#, D/C#, MI/O#, LOCK#, BHE#, BLE#, A23:A1 and HLDA change only at the beginning of phase one. D15:0 (write cycles) change only at the beginning of phase two.

The READY#, HOLD, BUSY#, ERROR#, PEREQ, FLT# and D15:0 (read cycles) inputs are sampled at the beginning of phase one. The NA#, INTR and NMI inputs are sampled at the beginning of phase two.

Figure 5. Drive Levels and Measurement Points for AC Specifications

|        |                                        | 40 I         | MHz          | 33           | MHz         | 25           | MHz          |                                    |

|--------|----------------------------------------|--------------|--------------|--------------|-------------|--------------|--------------|------------------------------------|

| Symbol | Parameter                              | Min.<br>(ns) | Max.<br>(ns) | Min.<br>(ns) | Max<br>(ns) | Min.<br>(ns) | Max.<br>(ns) | Test Condition                     |

|        | Operating Frequency                    | 0            | 40           | 0            | 33          | 0            | 25           | MHz (Note 1)                       |

| t1     | CLK2 Period                            | 12.5         |              | 15           |             | 20           |              |                                    |

| t2a    | CLK2 High Time                         | 4.5          |              | 6.25         |             | 7            |              | (Note 2)                           |

| t2b    | CLK2 High Time                         | 3.5          |              | 4            |             | 4            |              | (Note 2)                           |

| t3a    | CLK2 Low Time                          | 4.5          |              | 6.25         |             | 7            |              | (Note 2)                           |

| t3b    | CLK2 Low Time                          | 3.5          |              | 4.5          |             | 5            |              | (Note 2)                           |

| t4     | CLK2 Fall Time                         |              | 4            |              | 4           |              | 7            | (Note 2)                           |

| t5     | CLK2 Rise Time                         |              | 4            |              | 4           |              | 7            | (Note 2)                           |

| t6     | A23:1 Valid Delay                      | 4            | 13           | 4            | 15          | 4            | 17           | C <sub>L</sub> = 50 pF             |

| t7     | A23:1 Float Delay                      | 4            | 20           | 4            | 20          | 4            | 30           | (Note 3)                           |

| t8     | BHE#, BLE#,<br>LOCK# Valid Delay       | 4            | 13           | 4            | 15          | 4            | 17           | C <sub>L</sub> = 50 pF             |

| t9     | BHE#, BLE#,<br>LOCK# Float Delay       | 4            | 20           | 4            | 20          | 4            | 30           | (Note 3)                           |

| t10    | W/R#, M/IO#, D/C#,<br>ADS# Valid Delay | 4            | 13           | 4            | 15          | 4            | 17           | C <sub>L</sub> = 50 pF             |

| t11    | W/R#, M/IO#, D/C#,<br>ADS# Float Delay | 4            | 20           | 4            | 20          | 4            | 30           | (Note 3)                           |

| t12    | D15:0 Write Data<br>Valid Delay        | 7            | 18           | 7            | 23          | 7            | 23           | C <sub>L</sub> = 50 pF<br>(Note 5) |

| t12a   | D15:0 Write Data<br>Hold Time          | 2            |              | 2            |             | 2            |              | C <sub>L</sub> = 50 pF             |

| t13    | D15:0 Write Data<br>Float delay        | 4            | 17           | 4            | 17          | 4            | 22           | (Note 3)                           |

| t14    | HLDA Valid Delay                       | 4            | 17           | 4            | 20          | 4            | 22           | C <sub>L</sub> = 50 pF             |

| t15    | NA# Setup Time                         | 5            |              | 5            |             | 5            |              |                                    |

| t16    | NA# Hold Time                          | 2            |              | 2            |             | 3            |              |                                    |

| t19    | READY#Setup Time                       | 7            |              | 7            |             | 9            |              |                                    |

| t20    | READY#Hold Time                        | 4            |              | 4            |             | 4            |              |                                    |

| t21    | D15:0 Read Setup<br>Time               | 4            |              | 5            |             | 7            |              |                                    |

Table 6. AC Characteristics

#### NOTES:

1. Tested at maximum operating frequency and guaranteed by design characterization at lower operating frequencies.

2. These are not tested. They are guaranteed by characterization.

3. Float condition occurs when maximum output current becomes less than  $I_{LO}$  in magnitude. Float delay is not fully tested.

4. These inputs may be asynchronous to CLK2. The setup and hold specifications are given for testing purposes to ensure recognition within a specific CLK2 period.

5. Minimum time not 100% tested.

|        |                                             | 40 M         | ٨Hz          | 33           | MHz         | 25 MHz       |              |                |

|--------|---------------------------------------------|--------------|--------------|--------------|-------------|--------------|--------------|----------------|

| Symbol | Parameter                                   | Min.<br>(ns) | Max.<br>(ns) | Min.<br>(ns) | Max<br>(ns) | Min.<br>(ns) | Max.<br>(ns) | Test Condition |

| t22    | D15:0 Read Hold<br>Time                     | 3            |              | 3            |             | 5            |              |                |

| t23    | HOLD Setup Time                             | 4            |              | 9            |             | 9            |              |                |

| t24    | HOLD Hold Time                              | 2            |              | 2            |             | 3            |              |                |

| t25    | RESET Setup Time                            | 4            |              | 5            |             | 8            |              |                |

| t26    | RESET Hold Time                             | 2            |              | 2            |             | 3            |              |                |

| t27    | NMI, INTR Setup<br>Time                     | 5            |              | 5            |             | 6            |              | (Note 4)       |

| t28    | NMI, INTR Hold Time                         | 5            |              | 5            |             | 6            |              | (Note 4)       |

| t29    | PEREQ, ERROR#,<br>BUSY#, FLT# Setup<br>Time | 5            |              | 5            |             | 6            |              | (Note 4)       |

| t30    | PEREQ, ERROR#,<br>BUSY#, FLT# Hold<br>Time  | 4            |              | 4            |             | 5            |              | (Note 4)       |

Table 6. AC Characteristics (Continued)

#### NOTES:

1. Tested at maximum operating frequency and guaranteed by design characterization at lower operating frequencies.

2. These are not tested. They are guaranteed by characterization.

3. Float condition occurs when maximum output current becomes less than  $I_{LO}$  in magnitude. Float delay is not fully tested.

4. These inputs may be asynchronous to CLK2. The setup and hold specifications are given for testing purposes to ensure recognition within a specific CLK2 period.

5. Minimum time not 100% tested.

Figure 7. CLK2 Waveform

Figure 8. AC Timing Waveforms — Input Setup and Hold Timing

Figure 9. AC Timing Waveforms — Output Valid Delay Timing

Figure 10. AC Timing Waveforms — Output Float Delay and HLDA Valid Delay Timing

Figure 11. AC Timing Waveforms - RESET Setup and Hold Timing and Internal Phase

### 6.0 REVISION HISTORY

This -003 data sheet contains the following changes from the -002 version.

- Changed V<sub>cc</sub> at 40 MHz to 4.75V to 5.25V (Pages 1 and 9)

- Renamed "Powerdown Mode" to "Clock Freeze Mode" on page one.

- Added clarifications to Figure 1.

- Corrected pin numbering for A23:1 in Table 2

- Changed the first sentence in Section 3.3 from "...on page 12" to "...on page 9."

- Changed the first sentence on page 12 from "Table 7 lists..." to "Table 6..." Also changed the first sentence

of the fourth paragraph on page 12 from "...A25:1" to "...A23:1."