82C862

Dual Controller

Quad Port USB

# Preliminary Data Book CONFIDENTIAL

912-2000-030 Revision 1.0

#### Copyright

Copyright © 1999 OPTi Inc. All rights reserved. No part of this publication may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, manual, or otherwise, without the prior written permission of OPTi Inc., 1440 McCarthy Blvd. Milpitas, CA 95035.

#### **Disclaimer**

OPTi Inc. makes no representations or warranties with respect to the design and documentation herein described and especially disclaims any implied warranties of merchantability or fitness for any particular purpose. Further, OPTi Inc. reserves the right to revise the design and associated documentation and to make changes from time to time in the content without obligation of OPTi Inc. to notify any person of such revisions or changes.

#### **Trademarks**

OPTi and OPTi Inc. are registered trademarks of OPTi Inc. All other trademarks and copyrights are the property of their respective holders.

**OPTi Inc.**

1440 McCarthy Blvd. Milpitas, CA 95035 Tel: (408) 486-8000 Fax: (408) 486-8001 WWW: http://www.opti.com

# **TABLE OF CONTENTS**

| 1.0 | FEATURES                                                     | 1          |

|-----|--------------------------------------------------------------|------------|

| 2.0 | OVERVIEW                                                     | 1          |

| 3.0 | SIGNAL DEFINITIONS                                           | 3          |

|     | 3.1.1 Terminology/Nomenclature Conventions                   |            |

| 3.2 | Numerical Pin Cross-Reference List                           |            |

| 3.3 | SIGNAL DESCRIPTIONS                                          |            |

|     | 3.3.1 Clock and Reset Interface Signals                      | $\epsilon$ |

|     | 3.3.2 PCI Bus Interface Signals                              |            |

|     | 3.3.3 USB Interface Signals                                  |            |

| _   | 3.3.4 Host Controller shared signals: PME#, SMI#, REQ#, GNT# |            |

| _   | 3.3.5 Legacy and Interrupt Interface Signals                 |            |

| _   | 3.3.6 Power and Ground Pins                                  |            |

|     | 2.3.7 Strap Options                                          |            |

| 4.0 | FUNCTIONAL DESCRIPTION                                       | 13         |

| 4.1 | Universal Serial Bus (USB)                                   |            |

| 4.2 | PCI Controller                                               | 14         |

| 4.3 | CLOCK GENERATION                                             |            |

| 4.4 | Power Management Features                                    | 15         |

| 4.  | 1.4.1 Putting FireLink into USBSuspend State                 |            |

| 4.  | 1.4.2 Powering Down the USB I/O Cells                        |            |

| 4.  | 1.4.3 Stopping the 48MHz USB Clock                           |            |

| 4.  | !.4.4 Using CLKRUN#                                          |            |

| 4.  | 4.4.5 Stopping the Internal PCI Clocks                       |            |

| 4.  | 4.4.6 Power Control Modes                                    |            |

| 4.5 | Host Controller                                              | 19         |

| 4.  | 4.5.1 Legacy Support                                         | 20         |

| 4.  | 1.5.2 Intercept Port 60h and 64h Accesses                    | 20         |

| 4.6 | GENERAL PURPOSE PINS                                         | 21         |

| 5.0 | REGISTER DESCRIPTIONS                                        |            |

| 5.1 | PCICFG REGISTER SPACE                                        | 23         |

|     | 5.1.1 Programming Differences from 82C861 Component          | 23         |

| _   | 5.1.2 PCICFG 00h-FFh                                         |            |

| 5.2 |                                                              |            |

| _   | 5.2.1 MEMOFST 00h-5Ch                                        |            |

| _   | i.2.2 Legacy Support Registers                               |            |

| 5.  | 5.2.3 MEMOFST 100h-1Fh (Legacy Support Registers)            |            |

| 6.0 | ELECTRICAL RATINGS                                           |            |

| 6.1 | ABSOLUTE MAXIMUM RATINGS                                     |            |

| 6.2 |                                                              |            |

| 6.3 | AC CHARACTERISTICS (PRELIMINARY)                             |            |

| _   | 3.3.1 PCI Bus AC Timings                                     |            |

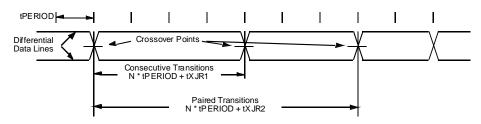

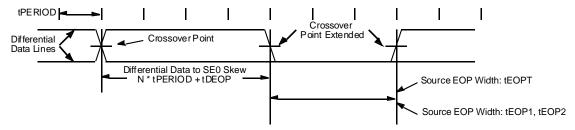

| _   | 3.3.2 USB AC Timings: Full Speed Source                      |            |

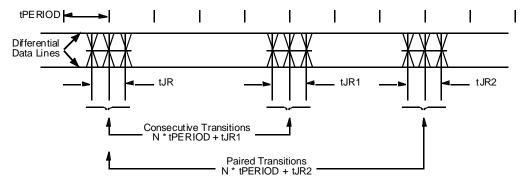

| _   | 3.3.3 USB AC Timings: Low Speed Source                       |            |

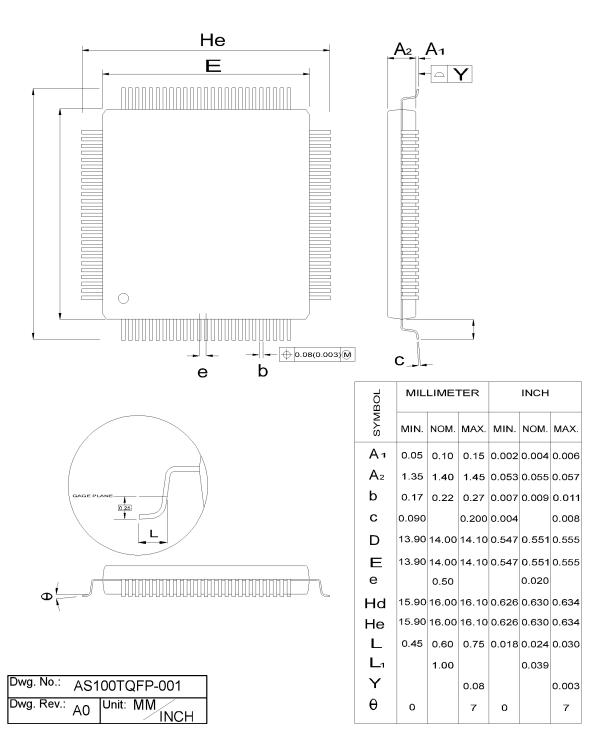

| 7.0 | MECHANICAL PACKAGE OUTLINES                                  | 46         |

|     | NAME THE TEST MORE                                           | 4-         |

# FireLink USB 82C862

#### 1.0 Features

- Compliant with USB rev. 1.1 specification

- Fully compatible with USB OHCI specification

- Two independent host controllers, two ports each, making FireLink USB a multi-function PCI device

- · Second host controller can be disabled if not used

- Clock input can be derived from either a 12MHz crystal or a 48MHz oscillator

- · Clocks can be turned off when not in use to save power

- Core operates at 3.3V; PCI inputs are 5V-tolerant

- Incorporates PCI Power Management, supporting very low power standby modes

- Implements CLKRUN# pin to support hardwareenforced power-down

- Packaged as 100-pin LQFP (Low-profile Quad Flat Pack)

- Supported by Windows 98, Windows 2000, and Windows CE

#### 2.0 Overview

This document describes the OPTi FireLink USB (82C862) controller.

This PCI-to-USB bridge is unique in that it consists of two independent dual-port controllers, each sharing only the common PCI bus connection. This arrangement allows for a total Universal Serial Bus bandwidth of 24Mb/s, divided into 12Mb/s for each pair of ports.

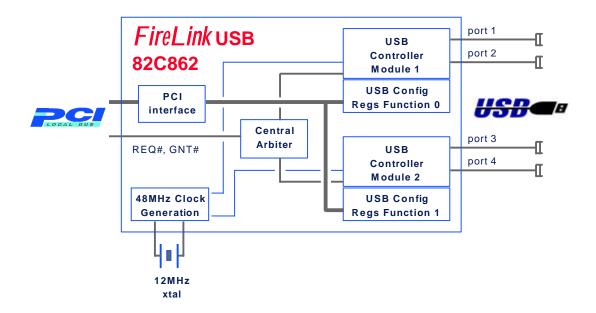

Figure 1 provides a block diagram of the overall functionality of the chip.

Figure 1. 82C862 FireLink USB Block Diagram

912-2000-030 Page 1

Revision: 1.0

# FireLink USB 82C862

## 3.0 Signal Definitions

#### 3.1 Terminology/Nomenclature Conventions

The "#" symbol at the end of a signal name indicates that the active, or asserted state occurs when the signal is at a low voltage level. When "#" is not present after the signal name, the signal is asserted when at the high voltage level.

The terms assertion and negation are used extensively. This is done to avoid confusion when working with a mixture of active low and active high signals. The term assert, or assertion indicates that a signal is active, independent of whether that level is represented by a high or low voltage. The term negate, or negation indicates that a signal is inactive.

The tables in this section use several common abbreviations. Table 1 lists the mnemonics and their meanings. Note that TTL/CMOS/Schmitt-trigger levels pertain to inputs only. Outputs are driven at CMOS levels.

Table 1. Signal Definitions Legend

| Mnemonic | Description              |

|----------|--------------------------|

| Analog   | Analog-level compatible  |

| CMOS     | CMOS-level compatible    |

| Dcdr     | Decoder                  |

| Diff     | Differential signal pair |

| Ext      | External                 |

| G        | Ground                   |

| I        | Input                    |

| Int      | Internal                 |

| I/O      | Input/Output             |

| Mux      | Multiplexer              |

| NIC      | No Internal Connection   |

| 0        | Output                   |

| OD       | Open drain               |

| Р        | Power                    |

| PD       | Pull-down resistor       |

| PU       | Pull-up resistor         |

| S        | Schmitt-trigger          |

| S/T/S    | Sustain Tristate         |

| TTL      | TTL-level compatible     |

Page 3

## 82C862

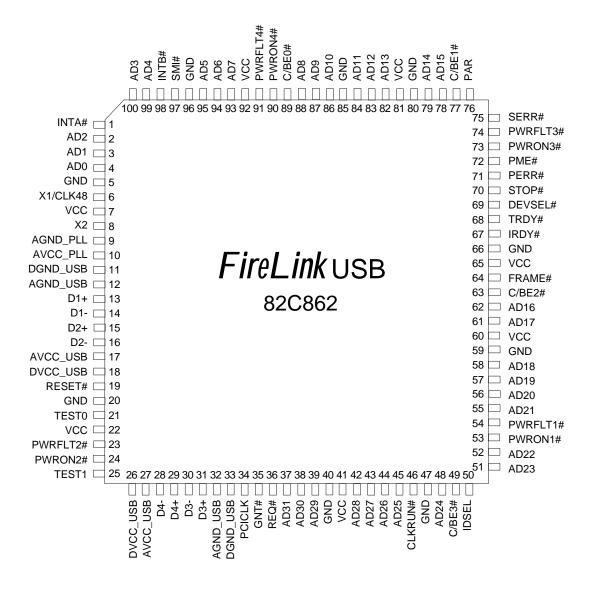

#### Figure 2. LQFP Pin Diagram (Note)

**Note:** Figure 3-1 shows a pin diagram of the 82C862 packaged in an LQFP (Low-profile Quad Flat Pack, square). Refer to Section 6.0, "Mechanical Package Outlines" for details regarding packaging.

#### **Numerical Pin Cross-Reference List** 3.2

| Pin<br>No. | Signal Name | Power Plane |

|------------|-------------|-------------|

| 1          | INTA#       | VCC         |

| 2          | AD2         |             |

| 3          | AD1         |             |

| 4          | AD0         |             |

| 5          | GND         |             |

| 6          | X1/CLK48    |             |

| 7          | VCC         |             |

| 8          | X2          |             |

| 9          | AGND_PLL    | AVCC_PLL    |

| 10         | AVCC_PLL    |             |

| 11         | DGND_USB    | DVCC_USB    |

| 12         | AGND_USB    | AVCC_USB    |

| 13         | D1+         |             |

| 14         | D1-         |             |

| 15         | D2+         |             |

| 16         | D2-         |             |

| 17         | AVCC_USB    |             |

| 18         | DVCC_USB    | DVCC_USB    |

| 19         | RESET#      | VCC         |

| 20         | GND         |             |

| 21         | TEST0       |             |

| 22         | VCC         |             |

| 23         | PWRFLT2     |             |

| 24         | PWRON2      |             |

| 25         | TEST1       |             |

| 26         | DVCC_USB    | DVCC_USB    |

| 27         | AVCC_USB    | AVCC_USB    |

| 28         | D4-         |             |

| 29         | D4+         |             |

| 30         | D3-         |             |

| 31         | D3+         |             |

| 32         | AGND_USB    |             |

| 33         | DGND_USB    | DVCC_USB    |

| 34         | PCICLK      | VCC         |

| Pin<br>No. | Signal Name | Power Plane |

|------------|-------------|-------------|

| 35         | GNT#        | VCC         |

| 36         | REQ#        |             |

| 37         | AD31        |             |

| 38         | AD30        |             |

| 39         | AD29        |             |

| 40         | GND         |             |

| 41         | VCC         |             |

| 42         | AD28        |             |

| 43         | AD27        |             |

| 44         | AD26        |             |

| 45         | AD25        |             |

| 46         | CLKRUN#     |             |

| 47         | GND         |             |

| 48         | AD24        |             |

| 49         | C/BE3#      |             |

| 50         | IDSEL       |             |

| 51         | AD23        |             |

| 52         | AD22        |             |

| 53         | PWRON1#     |             |

| 54         | PWRFLT1#    |             |

| 55         | AD21        |             |

| 56         | AD20        |             |

| 57         | AD19        |             |

| 58         | AD18        |             |

| 59         | GND         |             |

| 60         | VCC         |             |

| 61         | AD17        |             |

| 62         | AD16        |             |

| 63         | C/BE2#      |             |

| 64         | FRAME#      |             |

| 65         | VCC         |             |

| 66         | GND         |             |

| 67         | IRDY#       |             |

| 68         | TRDY#       |             |

| Pin<br>No. | Signal Name | Power Plane |

|------------|-------------|-------------|

| 69         | DEVSEL#     | VCC         |

| 70         | STOP#       |             |

| 71         | PERR#       |             |

| 72         | PME#        |             |

| 73         | PWRON3#     |             |

| 74         | PWRFLT3#    |             |

| 75         | SERR#       |             |

| 76         | PAR         |             |

| 77         | C/BE1#      |             |

| 78         | AD15        |             |

| 79         | AD14        |             |

| 80         | GND         |             |

| 81         | VCC         |             |

| 82         | AD13        |             |

| 83         | AD12        |             |

| 84         | AD11        |             |

| 85         | GND         |             |

| 86         | AD10        |             |

| 87         | AD9         |             |

| 88         | AD8         |             |

| 89         | C/BE0#      |             |

| 90         | PWRON4#     |             |

| 91         | PWRFLT4#    |             |

| 92         | VCC         |             |

| 93         | AD7         |             |

| 94         | AD6         |             |

| 95         | AD5         |             |

| 96         | GND         |             |

| 97         | SMI#        |             |

| 98         | INTB#       |             |

| 99         | AD4         |             |

| 100        | AD3         |             |

## 3.3 Signal Descriptions

## 3.3.1 Clock and Reset Interface Signals

| Signal Name    | Pin<br>No. | Pin<br>Type | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------|------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCICLK         | 34         | I           | <b>PCI Clock:</b> This input provides timing for all cycles on the host PCI bus; normally 33MHz. All other PCI signals are sampled on the rising edge of PCLK (timing parameters refer to this edge).                                                                                                                                                                                                                                                               |

| X1/CLK48<br>X2 | 6<br>8     | 0           | <b>USB Clock:</b> The CLK48 input provides timing for USB data signals; this clock must be 48MHz for proper USB operation. As an option, a 12MHz crystal can be connected across X1 and X2, in which case an internal PLL will develop the 48MHz signal. Refer to the TEST0-TEST1 strap options for selecting the mode of operation.                                                                                                                                |

| RESET#         | 19         | 0           | Reset: If RESET# is asserted for a minimum of 1µs while PCICLK is stable at 33MHz, it causes the 82C862 to enter its default state (all registers are set to their default values).                                                                                                                                                                                                                                                                                 |

|                |            |             | AD[31:0], C/BE[3:0]#, and PAR are always driven low by the 82C862 synchronously from the leading edge of RESET# and are always tristated from the trailing edge of RESET#. FRAME#, IRDY#, TRDY#, STOP#, and DEVSEL# are tristated from the leading edge of RESET# and remain so until driven as either a master or slave by the 82C862. RESET# may be asynchronous to PCICLK when asserted or negated, however, negation must occur with a clean, bounce-free edge. |

## 3.3.2 PCI Bus Interface Signals

| Signal Name | Pin<br>No.                                                                                                | Pin<br>Type | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------|-----------------------------------------------------------------------------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD[31:0]    | 37:39,<br>42:45,<br>49, 51,<br>55:58,<br>61:62,<br>78:79,<br>82:84,<br>86:88,<br>93:95,<br>99:100,<br>2:1 | I/O         | Address and Data Lines 31 through 0: This bus carries the address and/or data during a PCI bus cycle. A PCI bus cycle has two phases - an address phase which is followed by one or more data phases. During the initial clock of the bus cycle, the AD bus contains a 32-bit physical byte address. AD[7:0] is the least significant byte (LSB) and AD[31:24] is the most significant byte (MBS). After the first clock of the cycle, the AD bus contains data.  When the 82C862 is the target, AD[31:0] are inputs during the address phase. For the data phase(s) that follow, the 82C862 may supply data on AD[31:0] in the case of a read or accept data in the case of a write.  When the 82C862 is the master, it drives a valid address on AD[31:2] during the address phase, and drives write or accepts read data on AD[31:0] during the data phase. As a master, the 82C862 always drives AD[1:0] low. |

| C/BE[3:0]#  | 49, 63,<br>77, 89                                                                                         | I/O         | Bus Command and Byte Enables 3 through 0: These signals provide the command type information during the address phase and carry the byte enable information during the data phase. C/BE0# corresponds to byte 0, C/BE1# to byte 1, C/BE2# to byte 2, and C/BE3# to byte 3. If the 82C862 is the initiator of a PCI bus cycle, it drives C/BE[3:0]#. When it is the target, it samples C/BE[3:0]#.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| PAR    | 76 | 0              | <b>Even Parity:</b> The 82C862 calculates PAR for both the address and data phases of PCI cycles. PAR is valid one PCI clock after the associated address or data phase, but may or may not be valid for subsequent clocks. It is calculated based on 36 bits - AD[31:0] plus C/BE[3:0]#. "Even" parity means that the sum of the 36 bit values plus PAR is always an even number, even if one or more bits of C/BE[3:0]# indicate invalid data. |

|--------|----|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FRAME# | 64 | I/O<br>(s/t/s) | <b>Cycle Frame:</b> This signal is driven by the current PCI bus master to indicate the beginning and duration of an access. The master asserts FRAME# at the beginning of a bus cycle, sustains the assertion during data transfers, and then negates FRAME# in the final data phase.                                                                                                                                                           |

|        |    |                | FRAME# is an input when the 82C862 is the target and an output when it is the initiator.                                                                                                                                                                                                                                                                                                                                                         |

|        |    |                | FRAME# is tristated from the leading edge of RESET# and remains tristated until driven as either a master or slave by the 82C862.                                                                                                                                                                                                                                                                                                                |

| IRDY#  | 67 | I/O<br>(s/t/s) | <b>Initiator Ready:</b> IRDY#, along with TRDY#, indicates whether the 82C862 is able to complete the current data phase of the cycle. IRDY# and TRDY# are both asserted when a data phase is completed.                                                                                                                                                                                                                                         |

|        |    |                | During a write, the 82C862 asserts IRDY# to indicate that it has valid data on AD[31:0]. During a read, the 82C862 asserts IRDY# to indicate that it is prepared to accept data.                                                                                                                                                                                                                                                                 |

|        |    |                | IRDY# is an input when the 82C862 is a target and an output when it is the initiator.                                                                                                                                                                                                                                                                                                                                                            |

|        |    |                | IRDY# is tristated from the leading edge of RESET# and remains tristated until driven as either a master or a slave by the 82C862.                                                                                                                                                                                                                                                                                                               |

| TRDY#  | 68 | I/O<br>(s/t/s) | <b>Target Ready:</b> TRDY#, along with IRDY#, indicates whether the 82C862 is able to complete the current data phase of the cycle. TRDY# and IRDY# are both asserted when a data phase is completed.                                                                                                                                                                                                                                            |

|        |    |                | When the 82C862 is acting as the target during read and write cycles, it performs in the following manner:                                                                                                                                                                                                                                                                                                                                       |

|        |    |                | 1. During a read, the 82C862 asserts TRDY# to indicate that it has placed valid data on AD[31:0].                                                                                                                                                                                                                                                                                                                                                |

|        |    |                | 2. During a write, the 82C862 asserts TRDY# to indicate that is prepared to accept data.                                                                                                                                                                                                                                                                                                                                                         |

|        |    |                | TRDY# is an input when the 82C862 is the initiator and an output when it is the target.                                                                                                                                                                                                                                                                                                                                                          |

|        |    |                | TRDY# is tristated from the leading edge of RESET# and remains so until driven as either a master or a slave by the 82C862.                                                                                                                                                                                                                                                                                                                      |

| STOP#  | 70 | I/O<br>(s/t/s) | <b>Stop:</b> STOP# is an output when the 82C862 is the target and an input when it is the initiator. As the target, the 82C862 asserts STOP# to request that the master stop the current cycle. As the master, the assertion of STOP# by a target forces the 82C862 to stop the current cycle.                                                                                                                                                   |

|        |    |                | STOP# is tristated from the leading edge of RESET# and remains so until driven by the 82C862 acting as a slave.                                                                                                                                                                                                                                                                                                                                  |

# 82C862

| DEVSEL# | 69 | I/O<br>(s/t/s) | <ul> <li>Device Select: The 82C862 claims a PCI cycle via positive decoding by asserting DEVSEL#. As an output, the 82C862 drives DEVSEL# for two different reasons:</li> <li>1. If the 82C862 samples IDSEL active in configuration cycles, DEVSEL# is asserted.</li> <li>2. When the 82C862 decodes an internal address or when it subtractively decodes a cycle, DEVSEL# is asserted</li> <li>When DEVSEL# is an input, it indicates the target response to an 82C862 master-initiated cycle. DEVSEL# is tristated from the leading edge of RESET# and remains so until driven by the 82C862 acting as a slave.</li> </ul> |

|---------|----|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IDSEL   | 50 | I              | Initialization Device Select: This signal is the "chip select" during configuration read and write cycles. IDSEL is sampled by the 82C862 during the address phase of a cycle. If IDSEL is found to be active and the bus command is a configuration read or write, the 82C862 claims the cycle with DEVSEL#.                                                                                                                                                                                                                                                                                                                 |

| PERR#   | 71 | I/O            | Parity Error: The 82C862 uses this line to report data parity errors during any PCI cycle except a Special Cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SERR#   | 75 | I              | <b>System Error:</b> The 82C862 uses this line to report address parity errors and data parity errors on the Special Cycle command, or any other system error where the result will be catastrophic.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| REQ#    | 36 | 0              | <b>Bus Request:</b> REQ# is asserted by the 82C862 to request ownership of the PCI bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| GNT#    | 35 | I              | <b>Bus Grant:</b> GNT# is sampled by the 82C862 for an active low assertion, which indicates that it has been granted use of the PCI bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| CLKRUN# | 46 | I/O            | Clock Run: The CLKRUN# function is available on this pin and can be used to reduce chip power consumption during idle periods. It is an I/O sustained tristate signal and follows the PCI 2.1 defined protocol.                                                                                                                                                                                                                                                                                                                                                                                                               |

| GPIO2   |    |                | General Purpose I/O pin 2: These pins can be written or read by specific application software. Refer to PCICFG 53-55h for information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

## 3.3.3 USB Interface Signals

| Signal Name                                  | Pin<br>No.           | Pin<br>Type | Signal Description                                                                                                                                                                                                                            |

|----------------------------------------------|----------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D1+/D1-                                      | 13/14                | diff        | USB Port 1 Differential Data Pair: This pair comes from the first controller.                                                                                                                                                                 |

| D2+/D2-                                      | 15/16                | diff        | USB Port 2 Differential Data Pair: This pair comes from the first controller.                                                                                                                                                                 |

| D3+/D3-                                      | 28/29                | diff        | USB Port 3 Differential Data Pair: This pair comes from the second controller.                                                                                                                                                                |

| D4+/D4-                                      | 30/31                | diff        | USB Port 4 Differential Data Pair: This pair comes from the second controller.                                                                                                                                                                |

| PWRON1#<br>PWRON2#<br>PWRON3#<br>PWRON4#     | 53<br>24<br>73<br>90 | 0           | <b>Power On Lines 1, 2, 3 and 4:</b> These outputs are used to switch port VCC for the respective USB port. The controlled VCC is used only by the device connected to the port, and is not used by the 82C862 controller.                    |

| PWRFLT1#<br>PWRFLT2#<br>PWRFLT3#<br>PWRFLT4# | 54<br>23<br>74<br>91 | I           | <b>Power Fault Lines 1, 2, 3 and 4</b> : These inputs indicate that an over-current fault has occurred on the respective USB port. Their polarity can be both strap- and software-controlled: Refer to the Strap Options section for details. |

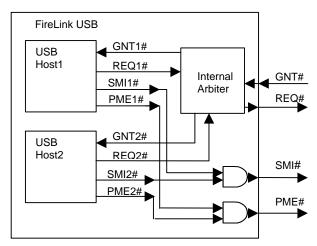

#### 3.3.4 Host Controller shared signals: PME#, SMI#, REQ#, GNT#

Several other signals are shared by both host controllers in addition to the bused PCI signals. The shared signals are all active low. The diagram below best explains the internal connections of the 82C862 device.

## 3.3.5 Legacy and Interrupt Interface Signals

| Signal Name | Pin<br>No. | Pin<br>Type | Signal Description                                                                                                                                                                                                         |

|-------------|------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SMI#        | 97         | 0           | System Management Interrupt: This signal is used to request a System Management Mode (SMM) interrupt. It can be connected to a spare EPMI pin on the host chipset.                                                         |

| GPIO4       |            |             | General Purpose I/O pin 4: These pins can be written or read by specific application software. Refer to PCICFG 53-55h for information.                                                                                     |

| PME#        | 72         | special     | <b>Power Management Event:</b> This signal is used to wake up the system from a PCI Power Management (PCI/PM) power saving mode. This pin is normally tristated and is driven low when active.                             |

|             |            |             | <b>Note:</b> When unpowered, the PME# driver output circuit will not be damaged if PME# is powered from another source. Moreover, once power is removed from the chip, this pin does not present a current path to ground. |

| GPIO3       |            |             | General Purpose I/O pin 3: These pins can be written or read by specific application software. Refer to PCICFG 53-55h for information.                                                                                     |

| INTA#       | 1          | 0           | PCI Interrupt A: This signal can be connected to a PCI interrupt line.                                                                                                                                                     |

| TEST0       | 21         | I/O         | <b>TEST Pin 0:</b> This pin is sampled by the chip at reset time to put the logic into a test mode if needed. See the STRAP OPTIONS section for details.                                                                   |

| GPIO0       |            |             | <b>General Purpose I/O pin 0:</b> These pins can be written or read by specific application software. Refer to PCICFG 53-55h for information.                                                                              |

| TEST1       | 25         | I/O         | <b>TEST Pin 1:</b> This pin is sampled by the chip at reset time to put the logic into a test mode if needed. See the STRAP OPTIONS section for details.                                                                   |

| GPIO1       |            |             | General Purpose I/O pin 1: These pins can be written or read by specific application software. Refer to PCICFG 53-55h for information.                                                                                     |

# 82C862

## 3.3.6 Power and Ground Pins

| Signal Name | Pin<br>No.                       | Pin<br>Type | Signal Description                                                                                                                 |

|-------------|----------------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------|

| VCC         | 7, 22, 41,<br>60, 65,<br>81, 92, | Р           | <b>3.3V Power Connection:</b> Core voltage is always 3.3V. However, the PCI interface can be 5V as the PCI inputs are 5V-tolerant. |

| AVCC_PLL    | 10                               | Р           | PLL Analog Power: Connect to low-noise 3.3V.                                                                                       |

| AVCC_USB    | 17, 27                           | Р           | USB I/O Analog Power: Connect to low-noise 3.3V.                                                                                   |

| DVCC_USB    | 18, 26                           | Р           | USB I/O Digital Power: Connect to 3.3V.                                                                                            |

| GND         | 20,40,47,<br>59,66,80,<br>85,96  | G           | Core Digital Ground: Connect to board ground.                                                                                      |

| AGND_PLL    | 9                                | G           | PLL Analog Ground: Connect to same board ground as GND.                                                                            |

| AGND_USB    | 12, 32                           | G           | USB I/O Analog Ground: Connect to same board ground as GND.                                                                        |

| DGND_USB    | 11, 33                           | G           | USB I/O Digital Ground: Connect to same board ground as GND.                                                                       |

### 3.3.7 Strap Options

The 82C862 component offers several operating mode choices at power-up time. These choices are selected through a strap resistor that pulls the related pin either up or down to the required level. A 4.7k ohm resistor is recommended.

**Table 2. Strap Selected Options**

| Pin     |                                                                                                                                                                                                                                                                                                                                  | Mode                                                                                                                                                                                                                                                                                                               |  |  |  |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PWRON3# |                                                                                                                                                                                                                                                                                                                                  | Enable/Disable Second Host                                                                                                                                                                                                                                                                                         |  |  |  |

|         | 1                                                                                                                                                                                                                                                                                                                                | Enable Second USB Host Controller (Function 1) [DEFAULT]                                                                                                                                                                                                                                                           |  |  |  |

|         | 0                                                                                                                                                                                                                                                                                                                                | Disable Second USB Host Controller. All clocks going to the logic for the second host are stopped to reduce power consumption.                                                                                                                                                                                     |  |  |  |

| TEST0   | TEST1                                                                                                                                                                                                                                                                                                                            | Mode Operation                                                                                                                                                                                                                                                                                                     |  |  |  |

| 0       | 0                                                                                                                                                                                                                                                                                                                                | PLL Operational Mode using 12 MHz crystal on X1 and X2 [DEFAULT]                                                                                                                                                                                                                                                   |  |  |  |

| 0       | 1                                                                                                                                                                                                                                                                                                                                | 48 MHz clock Operation Mode. X1 connects to 48 MHz clock, X2 no-connect.                                                                                                                                                                                                                                           |  |  |  |

| 1       | 1                                                                                                                                                                                                                                                                                                                                | NAND Tree test mode                                                                                                                                                                                                                                                                                                |  |  |  |

| 1       | 0                                                                                                                                                                                                                                                                                                                                | Tristate test mode                                                                                                                                                                                                                                                                                                 |  |  |  |

| SI      | VII#                                                                                                                                                                                                                                                                                                                             | PCI Power Management PME# function / Reference USB clock                                                                                                                                                                                                                                                           |  |  |  |

|         | 0                                                                                                                                                                                                                                                                                                                                | PME# becomes 48 MHz reference clock output from PLL. Used for testing PLL. Also disables PCI power management, PCICFG 06h[4] = 0.                                                                                                                                                                                  |  |  |  |

|         | 1                                                                                                                                                                                                                                                                                                                                | Enables PME# function and PCI power management, PCICFG 06h[4]=1. [DEFAULT]                                                                                                                                                                                                                                         |  |  |  |

| PWR     | ON2#                                                                                                                                                                                                                                                                                                                             | Global/Individual Power Control                                                                                                                                                                                                                                                                                    |  |  |  |

|         | Individual PWRON# and PWRFLT# for each port: [DEFAULT] HcRhDescA NoPowerSwitching=0 (MEMOFST 49h[1]) HcRhDescA PowerSwitchingMode=1 (MEMOFST 49h[0]) HcRhDescB PortPowerControlMask bit1,bit2=1,1 (MEMOFST4Eh[1,2]) HcRhDescA NoOvercurrentProtection=0 (MEMOFST 49h[4]) HcRhDescA OvercurrentProtectionMode=1 (MEMOFST 49h[3]]) |                                                                                                                                                                                                                                                                                                                    |  |  |  |

|         | 0                                                                                                                                                                                                                                                                                                                                | Global PWRON# and PWRFLT# for each port: HcRhDescA NoPowerSwitching=0 (MEMOFST 49h[1]) HcRhDescA PowerSwitchingMode=0 (MEMOFST 49h[0]) HcRhDescB PortPowerControlMask bit1,bit2=0,0 (MEMOFST4Eh[1,2]) HcRhDescA NoOvercurrentProtection=0 (MEMOFST 49h[4]) HcRhDescA OvercurrentProtectionMode=0 (MEMOFST 49h[3]]) |  |  |  |

# FireLink USB 82C862

## 4.0 Functional Description

#### 4.1 Universal Serial Bus (USB)

The 82C862 controller supports a PCI-based implementation of Universal Serial Bus utilizing the OpenHCI core developed by Compaq. The logic core consists of two USB host controller modules (making the 82C862 part a multi-function PCI device), and a PCI interface controller.

Each USB host controller module contains an integrated root hub that supports two downstream USB hubs or devices. Keyboard and mouse legacy support are also included for DOS compatibility with USB devices. This legacy support operates in conjunction with the primary host controller module as described later in this document.

This document must be used along with the following public domain reference documents to get the complete functional description of the USB core implementation.

- USB Specification, Revision 1.1

- OpenHCI Specification, Revision 1.0a

- PCI Specification, Version 2.1

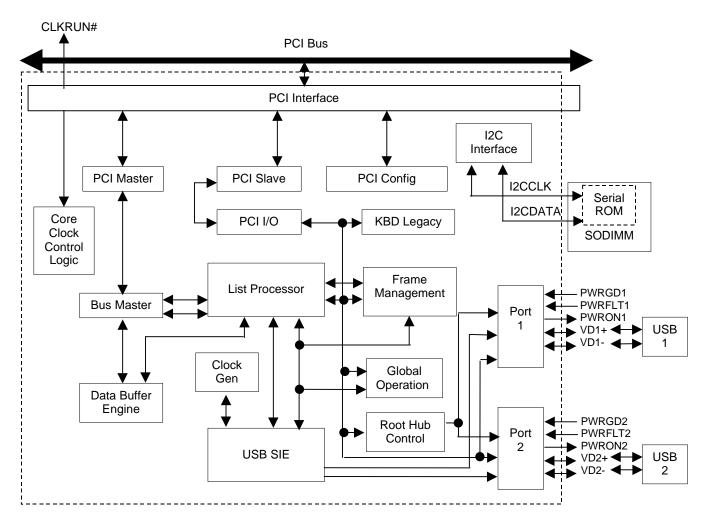

A functional block diagram of one of the two USB controller modules is given in Figure 4-1. The other is identical.

Figure 4-1 USB Functional Block Diagram

912-2000-030 Revision: 1.0

# FireLink USB 82C862

#### 4.2 PCI Controller

The PCI controller interfaces the host controller to the PCI bus. As a master, the PCI controller is responsible for running cycles on the PCI bus on behalf of the host controller. As a target, the PCI controller monitors the cycles on the PCI bus and determines when to respond to these cycles. A USB host controller module is a PCI target when it decodes cycles to its internal PCI configuration registers or to its internal PCI memory mapped I/O registers. The PCI controller asserts DEVSEL# in medium decode timing to claim a PCI transaction.

Since two PCI-interfaced USB controller modules reside on-chip, the logic includes an internal arbiter to select between the two modules when one or both make a bus mastering request.

The PCI configuration space of the primary USB host controller module is accessed as Device #X, Function #0, where Device #X depends on which AD line is connected to the IDSEL input. For the secondary USB host controller module, PCI configuration register space is accessed as Function #1 instead. PCI configuration space is hereafter referred to as PCICFG.

Table 3 gives a register map of the PCICFG register space (duplicated for each of the two functions). Refer to Section 5.1, "PCICFG Register Space" for detailed bit information.

Table 3. PCI Controller Register Map

| PCICFG  | R/W | Register Name           |  |  |

|---------|-----|-------------------------|--|--|

| 00h-01h | RO  | Vendor ID               |  |  |

| 02h-03h | RO  | Device ID               |  |  |

| 04h-05h | R/W | Command                 |  |  |

| 06h-07h | R/W | Status                  |  |  |

| 08h     | RO  | Revision ID             |  |  |

| 09h-0Bh | RO  | Class Code              |  |  |

| 0Ch     | R/W | Cache Line Size         |  |  |

| 0Dh     | R/W | Master Latency Timer    |  |  |

| 0Eh     | RO  | Header Type             |  |  |

| 0Fh     |     | Reserved                |  |  |

| 10h-13h | R/W | Base Address Register 0 |  |  |

| 14h-2Bh |     | Reserved                |  |  |

| 2Ch-2Dh | RO  | Subsystem Vendor        |  |  |

| 2Eh-2Fh | RO  | Subsystem ID            |  |  |

| 30h-3Bh |     | Reserved                |  |  |

| 3Ch     | R/W | Interrupt Line          |  |  |

| 3Dh     | R/W | Interrupt Pin           |  |  |

| 3Eh     | R/W | Minimum Grant           |  |  |

| PCICFG  | R/W | Register Name             |  |

|---------|-----|---------------------------|--|

| 3Fh     | R/W | Maximum Latency           |  |

| 40h-45h |     | Reserved for factory test |  |

| 46h-4Bh |     | Reserved                  |  |

| 4Ch     | R/W | Interrupt Pin Selection   |  |

| 4Dh     | R/W | Miscellaneous Control     |  |

| 4Eh-4Fh |     | Reserved                  |  |

| 50h     | R/W | PCI Host Feature Control  |  |

| 51h     |     | Reserved                  |  |

| 52h     | R/W | Strap Option Override     |  |

| 53h     | R/W | GPIO Select               |  |

| 54h     | R/W | GPIO Output Enable        |  |

| 55h     | R/W | GPIO Data                 |  |

| 56h-7Bh |     | Reserved                  |  |

| 7Ch-7Fh | R/W | Subsystem ID Restore      |  |

| 80h-EFh |     | Reserved                  |  |

| F0h-F5h | R/W | PCI Power Management      |  |

| F6h-FFh |     | Reserved                  |  |

#### 4.3 Clock Generation

The USB core requires an accurate 48MHz internal clock for proper operation. This clock can be obtained either by connecting an external 48MHz oscillator, or by connecting a 12MHz crystal.

To use the external 48MHz clock, connect the clock source to the X1 pin and strap TEST1 high. The X2 pin is not used in this configuration and must be left floating. This clock must be accurate to +/- 0.2%, or 2000ppm.

To use a 12MHz crystal, connect it to the X1 and X2 pins and strap TEST1 low. An internal PLL develops the required 48MHz clock. This PLL can be powered down when not in use through the PCI Power Management registers. Since the 12MHz clock generated is used to develop 48MHz internally, its accuracy must be within +/- 0.05%, or 500ppm.

#### 4.4 Power Management Features

FireLink USB 82C862 implements new power management features which can reduce the overall power consumed in mobile USB applications. Key features are as follows.

The OS can put each USB controller module individually into USBSuspend state.

Once in USBSuspend state, the BIOS can turn off the USB I/O cells on each port for further power savings.

The external PCI clock can be stopped if system hardware is designed to use the CLKRUN# pin from the 82C862 chip, which can also be used to awaken the system.

The external 48MHz USB clock can also be stopped along with the PCICLK when the system will be put into a Standby mode.

USB clocks to each of the internal modules can be stopped independently through the PCI power management registers. Each of these features is described in the sections below.

#### 4.4.1 Putting FireLink into USBSuspend State

Before a host system goes into a suspend state, the operating system should put the OHCI USB controller into USBSuspend mode by writing to register MEMOFST 04h[7:6] = 11.

#### 4.4.2 Powering Down the USB I/O Cells

Once in USBSuspend state, the USB I/O cells can be disabled to reduce power by setting PCICFG 50h[1:0] = 11. If this feature is used, the I/O cells should be disabled by the BIOS before going into system-level Suspend, and re-enabled by the BIOS before giving control back to the operating system.

#### 4.4.3 Stopping the 48MHz USB Clock

After the controller is put into USBSuspend state, still another step can be taken to further reduce power consumption: stop the 48MHz USB clock. If this route is taken, the USB clock must be stopped and started in a glitch free manner. The usual means of effecting this control would be through software control of the system clock generator circuit.

Once the USB clock is stopped, the system can be awakened by using PME#, which will be asserted on a USB wake up event (resume signalling, connect, disconnect). This system event should be designed to restart the 48MHz clock to the USB controller.

#### 4.4.4 Using CLKRUN#

The CLKRUN# pin is always operational in the 82C862 part; no enabling is required. The PCI Mobile Design Guide, available from the PCISIG, describes the operation of CLKRUN# in detail. Briefly, connected devices monitor this pin to see if it goes high, indicating that the host wants to stop the system PCICLKs. If the line goes high, connected devices are allowed to momentarily drive the pin low. The host will then take over driving this pin low until it wants to try again to stop the clocks.

The host system uses CLKRUN# to determine whether or not the 82C862 USB controller requires a PCI clock by releasing CLKRUN#, which is always pulled high with a resistor. The USB controller power management logic will drive this pin low again as required by the CLKRUN# specification if the controller is using the clock, i.e. whenever a USB device is attached. If the controller does not drive the clock low, the system is free to slow or stop the PCI clock.

## 82C862

### 4.4.5 Stopping the Internal USB Clocks

The 82C862 device is equipped with PCI Power Management registers. When either function is set to D3hot mode, its internal USB clock is switched off to effect a significant reduction in power consumption. Returning the system to D0 will restart the internal USB clock.

#### 4.4.6 Power Control Modes

The 82C862 pinout includes the following signals for controlling and monitoring USB power for the respective USB port:

- PWRON1-4# are active-low outputs to turn USB power on.

- PWRFLT1-4# are active-low inputs to detect over current.

At design time, it must be decided whether these control and monitoring signals will be used independently on a per-port basis (ideal situation), or paired together (for lower component cost). Consequently, the chip can strap into one of two power control modes:

- Individual PWRON# and PWRFLT# entered when PWRON2# is sensed high at reset

- Global PWRON# and PWRFLT# entered when PWRON2# is sensed low at reset.

The 82C862 part supports two modes for turning on power to the respective USB ports: Global and Individual (per-port). This logic is contained in the Root Hub partition of each USB controller module, and consists of a portion for the Root Hub itself as well as portions for each individual port. The operation of Global and Individual power switching is explained below.

**Global Power Switching** is the mode that is supported in the original 82C861 design. In this mode either PWRON1# or PWRON2# can be used to turn on power for both ports on USB Host 1, and either PWRON3# or PWRON4# can be used to turn on power for both ports USB Host 2. When supporting this mode the following registers are of significance:

| Register                           | Field                                                                    | Value or Function                                                                        |

|------------------------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| HcRhDescriptorA                    | NoPowerSwitching<br>MEMOFST 49h[1]                                       | 0: Ports are power switched                                                              |

| HcRhDescriptorA                    | PowerSwitchingMode<br>MEMOFST 49h[0]                                     | 0: All ports are powered at the same time                                                |

| HcRhDescriptorB                    | PortPowerControlMask<br>MEMOFST 4Eh[2:1]                                 | Not Used                                                                                 |

| HcRhStatus                         | ClearGlobalPower (write)<br>MEMOFST 50h[0]                               | This bit is written to '1' to turn OFF power to all ports.                               |

| HcRhStatus                         | SetGlobalPower (write)<br>MEMOFST 52h[0]                                 | This bit is written to '1' to turn ON power to all ports.                                |

| HcRhPort1Status<br>HcRhPort2Status | PortPowerStatus (read)<br>MEMOFST 55h[0] port 1<br>MEMOFST 59h[0] port 2 | 0=port power is off<br>1=port power is on<br>Only Set/ClearGlobalPower controls this bit |

# FireLink USB 82C862

Individual Power Switching is the mode in which the power to the USB ports can be controlled individually by using the Port Status registers for each port, or can also be controlled globally depending on the value in the PowerControlMask register. When strapping into this mode, the PowerControlMask registers will be set. All four signals, PWRON1#, PWRON2#, PWRON3#, and PWRON4# will be used to turn on the respective USB ports power and will be independently controlled. When supporting this mode the following registers are of significance:

| Register                                          | Field                                                                    | Value or Function                                                                                                                                                                                                                 |  |  |

|---------------------------------------------------|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| HcRhDescriptorA NoPowerSwitching MEMOFST 49h[1]   |                                                                          | 0: Ports are power switched                                                                                                                                                                                                       |  |  |

| HcRhDescriptorA PowerSwitchingMode MEMOFST 49h[0] |                                                                          | Each port is powered individually. This mode allows the port to be either global or individual controlled depending on value in PortPowerControlMask.                                                                             |  |  |

| HcRhDescriptorB                                   | PortPowerControlMask<br>MEMOFST 4Eh[2:1]                                 | This register determines if the ports power is controlled individually by the Port Status register, or globally by the Root Hub Status register.  0=port uses global Set/ClearGlobalPower 1=port uses per-port Set/ClearPortPower |  |  |

| HcRhStatus                                        | ClearGlobalPower (write)<br>MEMOFST 50h[0]                               | This bit is written to '1' to turn off power to ports whose PortPowerControlMask=0.                                                                                                                                               |  |  |

| HcRhStatus                                        | SetGlobalPower (write)<br>MEMOFST 52h[0]                                 | This bit is written to '1' to turn on power to ports whose PortPowerControlMask=0.                                                                                                                                                |  |  |

| HcRhPort1Status<br>HcRhPort2Status                | PortPowerStatus (read)<br>MEMOFST 55h[0] port 1<br>MEMOFST 59h[0] port 2 | 0=port power is off 1=port power is on If per-port switching is enabled for this port, then only Set/ClearPortPower affect this bit. If global mode is enabled, then Set/ClearGlobalPower control this bit.                       |  |  |

| HcRhPort1Status<br>HcRhPort2Status                | SetPortPower (write)<br>MEMOFST 55h[0] port 1<br>MEMOFST 59h[0] port 2   | sets PortPowerStatus     Only valid if port is enabled for per-port switching.                                                                                                                                                    |  |  |

| HcRhPort1Status<br>HcRhPort2Status                | ClearPortPower (write)<br>MEMOFST 55h[1] port 1<br>MEMOFST 59h[1] port 2 | clear PortPowerStatus     Only valid if port is enabled for per-port switching.                                                                                                                                                   |  |  |

# 82C862

The 82C862 logic also supports both Global and per-port overcurrent detection as follows.

**Global overcurrent mode** – either PWRFLT1# or PWRFLT2# can be used to detect an overcurrent condition on any port on USB Host 1, and either PWRFLT3# or PWRFLT4# can be used to detect an overcurrent condition on any port on USB Host 2. For example, if PWRFLT1# is asserted, it means an overcurrent condition exists on USB Host 1, resulting in power shutoff for both ports on USB Host 1, and setting of the appropriate global overcurrent indicator bits.

| Register                           | Field                                                                            | Value or Function                                                                     |  |

|------------------------------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--|

| HcRhDescriptorA                    | NoOvercurrentProtection<br>MEMOFST 49h[4]                                        | 0: Over-current status is reported                                                    |  |

| HcRhDescriptorA                    | OverCurrentProtectionMode 0: Global - Over-current re collectively for all ports |                                                                                       |  |

| HcRhStatus                         | OverCurrentIndicator<br>MEMOFST 50h[1]                                           | Global over-current exists     power operations normal                                |  |

| HcRhStatus                         | OverCurrentIndicatorChange<br>MEMOFST 52h[1]                                     | Set by hardware when OverCurrentIndicator bit changes. Write a '1' to clear this bit. |  |

| HcRhPort1Status<br>HcRhPort2Status | PortOverCurrentIndicator<br>MEMOFST 54h[3] port 1<br>MEMOFST 58h[3] port 2       | Not used, set to '0' for global over-<br>current.                                     |  |

| HcRhPort1Status<br>HcRhPort2Status | PortOverCurrentIndicatorChange<br>MEMOFST 56h[3] port 1<br>MEMOFST 5Ah[3] port 2 | Not used, set to '0' for global over-<br>current.                                     |  |

**Per-Port overcurrent mode** – PWRFLT1 #, PWRFLT2#, PWRFLT3#, and PWRFLT4# are all used to monitor each port individually. If an overcurrent condition exists on one port, power is only shut off to that port.

| Register                           | Field                                                                            | Value or Function                                                                         |  |

|------------------------------------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--|

| HcRhDescriptorA                    | NoOvercurrentProtection<br>MEMOFST 49h[4]                                        | 0: Over-current status is reported                                                        |  |

| HcRhDescriptorA                    | OverCurrentProtectionMode<br>MEMOFST 49h[3]                                      | 1: Over-current is reported on a perport basis                                            |  |

| HcRhStatus                         | OverCurrentIndicator<br>MEMOFST 50h[1]                                           | Not used, always '0' for per-port over-current mode.                                      |  |

| HcRhStatus                         | OverCurrentIndicatorChange<br>MEMOFST 52h[1]                                     | Not used, always '0' for per-port over-current mode.                                      |  |

| HcRhPort1Status<br>HcRhPort2Status | PortOverCurrentIndicator<br>MEMOFST 54h[3] port 1<br>MEMOFST 58h[3] port 2       | 0: no over-current condition 1: over-current condition exists                             |  |

| HcRhPort1Status<br>HcRhPort2Status | PortOverCurrentIndicatorChange<br>MEMOFST 56h[3] port 1<br>MEMOFST 5Ah[3] port 2 | Set by hardware when PortOverCurrentIndicator bit changes. Write a '1' to clear this bit. |  |

#### 4.5 Host Controller

This block is the operational control block in the USB core. It is responsible for the host controller operational states (Suspend, Disabled, Enabled), special USB signaling (Reset, Resume), status, interrupt control, and host controller configuration information.

The host controller (HC) interface registers are PCI memory mapped I/O, hereafter referred to as MEMOFST. Table 4-2 gives a register map for the MEMOFST register space. Refer to Section 5.2, "Host Controller Register Space" for detailed bit information.

Table 4. Host Controller Register Map

| MEMOFST | R/W | Register Name       |

|---------|-----|---------------------|

| 00h-03h | RO  | HcRevision          |

| 04h-07h | R/W | HcControl           |

| 08h-0Bh | R/W | HcCommandStatus     |

| 0Ch-0Fh | R/W | HcInterruptStatus   |

| 10h-13h | R/W | HcInterrupt Enable  |

| 14h-17h | R/W | HcInterrupt Disable |

| 18h-1Bh | R/W | HcHCCA              |

| 1Ch-1Fh | R/W | HcPeriodCurrentED   |

| 20h-23h | R/W | HcControlHeadED     |

| 24h-27h | R/W | HcControlCurrentED  |

| 28h-2Bh | R/W | HcBulkHeadED        |

| 2Ch-2Fh | R/W | HcBulkCurrentED     |

| 30h-33h | R/W | HcDoneHead          |

| 34h-37h | R/W | HcFmInterval        |

| 38h-3Bh | R/W | HcFrameRemaining    |

| 3Ch-3Fh | R/W | HcFmNumber          |

| 40h-43h | R/W | HcPeriodicStart     |

| 44h-47h | R/W | HcLSThreshold       |

| 48h-4Bh | R/W | HcRhDescriptorA     |

| 4Ch-4Fh | R/W | HcRhDescriptorB     |

| 50h-53h | R/W | HcRhStatus          |

| 54h-57h | R/W | HcRhPort1Status     |

| 58h-5Bh | R/W | HcRhPort2Status     |

### 82C862

#### 4.5.1 Legacy Support

Four registers are provided for legacy support:

- 1. HceControl

- -- Used to enable and control the emulation hardware and report various status information.

- HceInput

- -- Emulation side of the legacy Input Buffer register.

- 3. HceOutput

- -- Emulation side of the legacy Output Buffer register where keyboard and mouse data is to be written by software.

- 4. HceStatus

- -- Emulation side of the legacy Status register.

These registers are located in the Host Controller Register Space; from MEMOFST 100h through 10Fh. Table 4-3 shows a register map of these registers. Refer to Section 5.2.2, "Legacy Support Registers" for detailed bit information.

Table 5. Legacy Support Register Map

| MEMOFST   | R/W | Register Name |

|-----------|-----|---------------|

| 100h-103h | R/W | HceControl    |

| 104h-107h | R/W | HceInput      |

| 108h-10Bh | R/W | HceOutput     |

| 10Ch-10Fh | R/W | HceStatus     |

#### 4.5.2 Intercept Port 60h and 64h Accesses

The HceStatus, HceInput, and HceOutput registers are accessible at I/O Ports 60h and 64h when emulation is enabled. Reads and writes to these registers using the I/O Ports do have some side effects as shown in Table 4-4. However, accessing these registers directly through their memory address produces no side effects.

When emulation is enabled, I/O accesses of Ports 60h and 64h must be handled by the Host Controller (HC). The HC must be positioned in the system so that it can do a positive decode of accesses to Ports 60h and 64h on the PCI bus. If a keyboard controller is present in the system, it must either use subtractive decode or have provisions to disable its decode of Ports 60h and 64h. If the legacy keyboard controller uses positive decode and is turned off during emulation, it must be possible for the emulation code to quickly re-enable and disable the legacy keyboard controller Port 60h and 64h decode. This is necessary to support a mixed operating environment.

Table 6. Emulated Registers and Side Effects

| Register Contents<br>Accessed/Modified | Side Effect                                                                                                          |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| HceOutput                              | A read from Port 60h will set the Output Full bit (MEMOFST 10Ch[0]) to 0.                                            |

| HceInput                               | A write to Port 60h will set the Input Full bit (MEMOFST 10Ch[1]) to 1 and the Cmd Data bit (MEMOFST 10Ch[3]) to 0.  |