# HIGH SPEED MULTIPORT MEMORY 82S12 (8x4 MULTIPORT RAM) 82S112

# DIGITAL 8000 SERIES TTL/MEMORY

#### DESCRIPTION

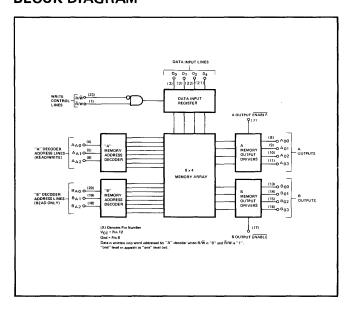

The 82S12/112 is a Schottky TTL 32 bit multiport memory organized in 8 words of 4 bits each. The device is ideally suited for high speed accumulators and buffer memories.

Stored data is addressed through 2 independent sets of 3-input decoders, and read out when the corresponding output enable line is low. Two separate word locations can, therefore, be read at the same time by enabling both the A and B output drivers. In addition, data can be read and written at the same time by utilizing the "A" address to specify the location of the word to be written, and the "B" address to specify the word to be read.

The 82S12/112 can be used in larger memory arrays since it includes all the control logic required to disable the chip and the outputs are open-collector devices suitable for "Wire-ORing."

# **FEATURES**

- LOW CURRENT INPUT BUFFERS (-25μA TYPICAL)

- SEPARATE INPUT DECODERS FOR EACH WORD

- SEPARATE OUTPUT ENABLE LINES FOR EACH WORD

- OPEN COLLECTOR (82S12) OR TRI-STATE (82S112) **OUTPUTS**

- **2 WRITE ENABLE LINES**

- FAST ACCESS (20 ns TYPICAL)

- **USEFUL 8 × 4 ORGANIZATION**

- TTL COMPATIBLE

- NON INVERTING DATA LINES

# **BLOCK DIAGRAM**

#### **APPLICATIONS**

**SCRATCH PAD MEMORY BUFFER MEMORY ACCUMULATOR REGISTER GENERAL REGISTER**

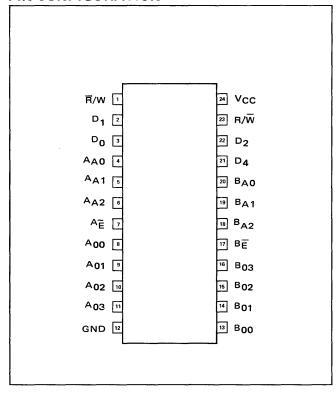

#### PIN CONFIGURATION

## **TRUTH TABLE**

| R/W                                       | R/W                                  | A<br>OUTPUT<br>ENABLE                | B<br>OUTPUT<br>ENABLE                | MODE                                                            | OUTPUTS                                              |                                                       |

|-------------------------------------------|--------------------------------------|--------------------------------------|--------------------------------------|-----------------------------------------------------------------|------------------------------------------------------|-------------------------------------------------------|

|                                           |                                      |                                      |                                      |                                                                 | Α                                                    | В                                                     |

| 0<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>1 | X<br>X<br>X<br>1<br>1<br>1<br>0<br>0 | 1<br>1<br>0<br>0<br>1<br>1<br>0<br>0 | 1<br>0<br>1<br>0<br>1<br>0<br>1<br>0 | Outputs Disabled Read Read Read Read Read Read Read Write Write | "1" Data Data "1" Data Data "1" Data Data "1" "1"    | "1" Data "1" Data "1" Data "1" Data "1" Data "1" Data |

| 1                                         | 0                                    | 0                                    | 1                                    | Write<br>Write                                                  | Data<br>Being<br>Written<br>Data<br>Being<br>Written | "B"<br>Address<br>"1"                                 |

# OBJECTIVE ELECTRICAL SPECIFICATIONS $0^{\circ}C \leqslant T_{A} \leqslant 75^{\circ}C$ ; -4.75 V $\leqslant V_{CC} \leqslant 5.25$ V.

| CHARACTERISTICS                     |      | LIMITS  |         |       |                                               |  |

|-------------------------------------|------|---------|---------|-------|-----------------------------------------------|--|

| CHARACTERISTICS                     | MIN. | TYP.    | MAX.    | UNITS | TEST CONDITIONS                               |  |

| Input "0" Current                   |      |         | -250    | μΑ    | V <sub>in</sub> = 0.45 V                      |  |

| Input "1" Current                   |      |         | 25      | μΑ    | V <sub>in</sub> = 5.5 V                       |  |

| Input "0" Threshold Voltage         | 1    |         | 0.85    | v     |                                               |  |

| Input "1" Threshold Voltage         | 2.0  |         |         | V     |                                               |  |

| Input Clamp Voltage                 | -1.2 |         |         | V     | l <sub>in</sub> = -18 mA                      |  |

| Output "0" Current                  | 16   | j       |         | mA    | V <sub>out</sub> = 0.5 V                      |  |

| Output "0" Current                  | 9.6  |         |         |       | V <sub>out</sub> = 0.45 V                     |  |

| Output "1" Voltage (825112)         | 2.6  |         |         | Volts | $I_{out} = -3.2 \text{ mA}$                   |  |

| Output Off Current (82S12)          |      |         | 40      | μΑ    | V <sub>out</sub> ≤ 5.5 V                      |  |

| Output Off Current (82S112)         | -40  |         | +40     | μΑ    | $0.45 \le V_{Out} \le 5.5 \text{ V}$          |  |

| Power Consumption                   |      | 110/550 | 160/840 | mA/mW | Outputs Enabled                               |  |

| Write Pulse Width T1                |      | 15      | 30      | ns    | TA = 25°C Only                                |  |

| Т1                                  |      | Ĭ       | 45      | ns    | $0^{\circ}C \leq T_{\Delta} \leq 75^{\circ}C$ |  |

| Address Set Up Time T <sub>2</sub>  |      | 10      |         | ns    | A                                             |  |

| Address Hold Time T <sub>3</sub>    |      | 0       |         | ns    |                                               |  |

| Data Input Hold Time T <sub>4</sub> |      | 15      |         | ns    |                                               |  |

| Write Access Time T5                |      | 30      |         | ns    |                                               |  |

| Data Input Set Up Time T6           |      | 5       |         | ns    |                                               |  |

| Output Enable Time T7               |      | 10      | 20      | ns    |                                               |  |

| Output Disable Time T8              |      | 10      | 20      | ns    |                                               |  |

| Address Access Time Tg              |      | 20      | 30      | ns    |                                               |  |

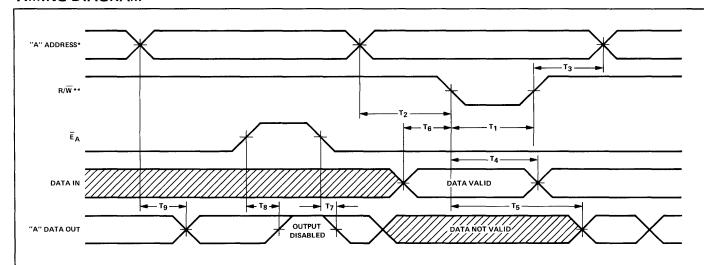

## **TIMING DIAGRAM**

- $T_1$  WRITE PULSE WIDTH Width of write pulse (when R/W="1" and R/W="0")

- T<sub>2</sub> ADDRESS SETUP TIME Required delay between beginning of valid Address and beginning of Write pulse.

- ${\rm T_3}$   $\,$  ADDRESS HOLD TIME Required delay between end of Write pulse and end of valid Address.

- T<sub>4</sub> DATA INPUT HOLD TIME Required delay between start of Write pulse and end of Valid Data input.

- T<sub>5</sub> WRITE ACCESS TIME Delay between beginning of Write pulse and Data Out at new value.

- T<sub>6</sub> DATA INPUT SET-UP TIME Required delay between beginning ov Valid Data Input and start of Write pulse.

- T<sub>7</sub> OUTPUT ENABLE TIME Delay between beginning of Output Enable high and when Data Output becomes valid.

- $\rm T_8$   $\,$  OUTPUT DISABLE TIME Delay between when Output Enable becomes low and Data Output is in off state.

- Tg ADDRESS ACCESS TIME Delay between beginning of Valid Address (with Output Enable high, R/W high and R/W low) and when Data Output becomes valid.

## NOTES

<sup>\*&</sup>quot;B" Address functions identically in read mode. No write mode through B address decoder.

<sup>\*\*</sup>R/W input is either the reverse of R/W or held high.

Outputs can be disabled during write cycle to penetrate a known output state during write.