# **Digital Audio Interface Transceiver**

# DESCRIPTION

The WM8802 is a digital audio interface transceiver conforming to IEC 60958/61937 and EIAJ CP-1201. The device supports data sampling input rates of up to 192 kHz. Data input to the serial digital audio data input pin can also be modulated. The WM8802 features up to 6 data inputs and 1 data output.

Data can be demodulated using the on-board PLL or with the use of an external clock source.

The WM8802 is controlled via a 4-wire CCB compatible control interface. This interface provides access to the channel status bits. The WM8802 also provides a number of flag outputs including PCM data valid, de-emphasis, lock and IEC 61937, DTS-CD/LD detection.

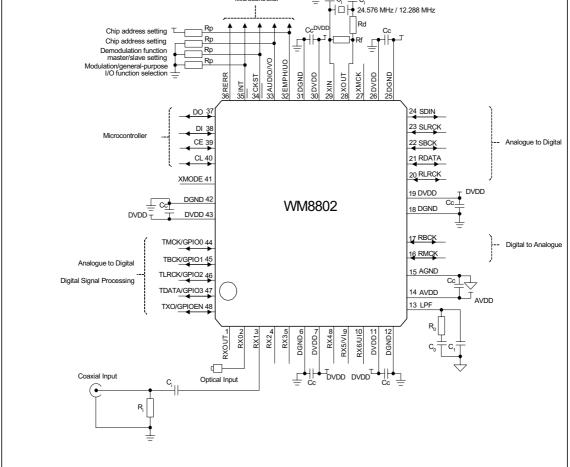

The device is available in a small 48-pin SQFP package.

# **FEATURES**

- PLL circuit for synchronization with transferred input biphase mark signal.

- Input sampling frequency: 32kHz to 192kHz

- Outputs clocks: fs, fs/2, 2fs, 32fs, 64fs, 128fs, 256fs, 384fs, and 512fs.

- 4-Wire CCB MPU Serial Control or Hardware Default Interface

- Master or Slave Clocking Mode

- Programmable Audio Data Interface Modes

- I<sup>2</sup>S, Left, Right Justified

- 16/20/24/32 bit Word Lengths

- 3.3V Digital supply Operation

- 5V tolerant digital input ports

# APPLICATIONS

- DVD Receivers

- AV Amplifiers

- DVD Recorders

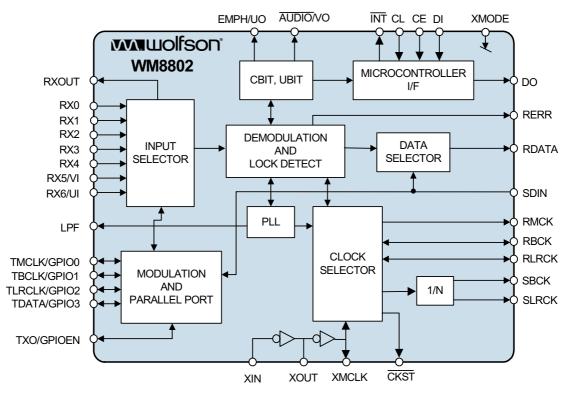

**BLOCK DIAGRAM**

WOLFSON MICROELECTRONICS plc

Product Preview, April 2004, Rev 1.1

# TABLE OF CONTENTS

| DESCRIPTION                                                                     | 1    |

|---------------------------------------------------------------------------------|------|

| FEATURES                                                                        | 1    |

| APPLICATIONS                                                                    | 1    |

| BLOCK DIAGRAM                                                                   | 1    |

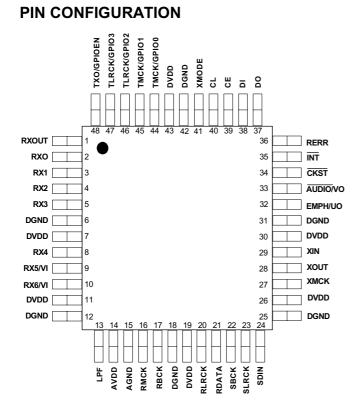

| PIN CONFIGURATION                                                               | 3    |

| ORDERING INFORMATION                                                            | 3    |

| PIN DESCRIPTION                                                                 |      |

| ABSOLUTE MAXIMUM RATINGS                                                        |      |

| RECOMMENDED OPERATING CONDITIONS                                                | 7    |

| ELECTRICAL CHARACTERISTICS                                                      | 7    |

| DC CHARACTERISTICS                                                              | 7    |

| AC CHARACTERISTICS                                                              |      |

| MICROCONTROLLER INTERFACE AC CHARACTERISTICS                                    |      |

| DEVICE DESCRIPTION                                                              |      |

| INITIAL SYSTEM SETTINGS                                                         |      |

| SYSTEM RESET (XMODE)                                                            |      |

| CHIP ADDRESS SETTINGS (EMPHA/UO, AUDIO /VO)                                     |      |

| DEMODULATION FUNCTION MASTER/SLAVE SETTINGS ( $\overline{CKST}$ )               |      |

| MODULATION FUNCTION AND GENERAL-PURPOSE I/O PORT SWITCHING ( $\overline{INT}$ ) |      |

| DESCRIPTION OF DEMODULATION FUNCTION                                            |      |

| CLOCKS                                                                          | . 13 |

| BI-PHASE SIGNAL INPUT / OUTPUT                                                  |      |

|                                                                                 |      |

| ERROR OUTPUT PROCESSING<br>CHANNEL STATUS OUTPUT                                |      |

| OTHER OUTPUTS                                                                   |      |

| IEC61937, DTS-CD/LD DETECTION FLAG OUTPUT                                       |      |

| <b>DESCRIPTION OF MODULATION FUNCTION AND GENERAL-PURPOSE I/OS</b>              |      |

| MODULATION FUNCTION USAGE METHOD.                                               |      |

| GENERAL PURPOSE I/O (GPIO0, GPIO1, GPIO2, GPIO3, GPIOEN)                        | . 36 |

| MICRO-CONTROLLER INTERFACE (INT, CL, CE, DI, DO)                                |      |

| DESCRIPTION OF MICRO-CONTROLLER INTERFACE                                       |      |

| WRITE DATA                                                                      |      |

| READ DATA                                                                       |      |

| BURST PREAMBLE PC FIELD                                                         | . 61 |

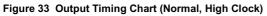

| RECOMMENDED EXTERNAL COMPONENTS                                                 |      |

| SAMPLE APPLICATION<br>RECOMMENDED EXTERNAL COMPONENTS VALUES                    | .62  |

|                                                                                 |      |

| PACKAGE DRAWING                                                                 |      |

| IMPORTANT NOTICE                                                                |      |

|                                                                                 | . 05 |

# **ORDERING INFORMATION**

| DEVICE       | DEVICE TEMPERATURE RANGE PACK |             | PEAK SOLDERING<br>TEMPERATURE |

|--------------|-------------------------------|-------------|-------------------------------|

| WM8802SCFT/V | 0 to +70oC                    | 48-pin SQFP | 240°C                         |

# **PIN DESCRIPTION**

| PIN | NAME       | TYPE                       | DESCRIPTION                                                                                            |  |  |

|-----|------------|----------------------------|--------------------------------------------------------------------------------------------------------|--|--|

| 1   | RXOUT      | Digital Output             | Input bi-phase selection data output pin                                                               |  |  |

| 2   | RX0        | Digital Input <sub>1</sub> | TTL-compatible digital data input pin                                                                  |  |  |

| 3   | RX1        | Digital Input              | Coaxial-compatible digital data input pin with built-in amplifier                                      |  |  |

| 4   | RX2        | Digital Input <sub>1</sub> | TTL-compatible digital data input pin                                                                  |  |  |

| 5   | RX3        | Digital Input <sub>1</sub> | TTL-compatible digital data input pin                                                                  |  |  |

| 6   | DGND       | Supply                     | Digital GND                                                                                            |  |  |

| 7   | DVDD       | Supply                     | Digital power supply                                                                                   |  |  |

| 8   | RX4        | Digital Input <sub>1</sub> | TTL-compatible digital data input pin                                                                  |  |  |

| 9   | RX5/VI     | Digital Input <sub>1</sub> | TTL-compatible digital data. Validity flag input pin for modulation.                                   |  |  |

| 10  | RX6/UI     | Digital Input <sub>1</sub> | TTL-compatible digital data. User data input pin for modulation.                                       |  |  |

| 11  | DVDD       | Supply                     | PLL digital power supply                                                                               |  |  |

| 12  | DGND       | Supply                     | PLL digital GND                                                                                        |  |  |

| 13  | LPF        | Analogue Output            | PLL loop filter connection pin                                                                         |  |  |

| 14  | AVDD       | Supply                     | PLL analog power supply                                                                                |  |  |

| 15  | AGND       | Supply                     | PLL analog GND                                                                                         |  |  |

| 16  | RMCK       | Digital Output             | R system clock output pin (256fs, 512fs, XIN, VCO)                                                     |  |  |

| 17  | RBCK       | Digital Output/Input       | R bit clock input/output pin (64fs)                                                                    |  |  |

| 18  | DGND       | Supply                     | Digital GND                                                                                            |  |  |

| 19  | DVDD       | Supply                     | Digital power supply                                                                                   |  |  |

| 20  | RLRCK      | Digital Output/Input       | R LR clock input/output pin (fs)                                                                       |  |  |

| 21  | RDATA      | Digital Output             | Serial audio data input pin                                                                            |  |  |

| 22  | SBCK       | Digital Output             | S bit clock output pin (32fs, 64fs, 128fs)                                                             |  |  |

| 23  | SLRCK      | Digital Output             | S LR clock output pin (fs/2, fs, 2fs)                                                                  |  |  |

| 24  | SDIN       | Digital Input <sub>1</sub> | Serial audio data input pin                                                                            |  |  |

| 25  | DGND       | Supply                     | Digital GND                                                                                            |  |  |

| 26  | DVDD       | Supply                     | Digital power supply                                                                                   |  |  |

| 27  | XMCK       | Analogue Output            | Oscillation amplifier output pin                                                                       |  |  |

| 28  | XOUT       | Analogue Output            | Crystal resonator connection output pin                                                                |  |  |

| 29  | XIN        | Analogue Input             | Crystal resonator connection, external supply clock input pin (24.576 MHz o 12.288 MHz)                |  |  |

| 30  | DVDD       | Supply                     | Digital power supply                                                                                   |  |  |

| 31  | DGND       | Supply                     | Digital GND                                                                                            |  |  |

| 32  | EMPH/UO    | Digital Input/Output       | Emphasis information, U data output. Chip address setting pin <sup>2</sup> .                           |  |  |

| 33  | AUDIO/VO   | Digital Input/Output       | Non-PCM output, V flag output. Chip address setting pin <sup>2</sup> .                                 |  |  |

| 34  | CKST       | Digital Input/Output       | Clock switch transition period signal. Demodulation master or slave function switch pin <sup>3</sup> . |  |  |

| 35  | ĪNT        | Digital Input/Output       | Micro-controller interrupt output. Modulation or general-purpose I/O switch pin <sup>4</sup> .         |  |  |

| 36  | RERR       | Digital Output             | PLL clock error, data error flag output                                                                |  |  |

| 37  | DO         | Digital Output             | Micro-controller I/F read data output pin (3-state)                                                    |  |  |

| 38  | DI         | Digital Input <sub>1</sub> | Micro-controller I/F write data input pin                                                              |  |  |

| 39  | CE         | Digital Input <sub>1</sub> | Micro-controller I/F chip enable input pin                                                             |  |  |

| 40  | CL         | Digital Input              | Micro-controller I/F clock input pin                                                                   |  |  |

| 41  | XMODE      | Digital Input <sub>1</sub> | System reset input pin                                                                                 |  |  |

| 42  | DGND       | Supply                     | Digital GND                                                                                            |  |  |

| 43  | DVDD       | Supply                     | Digital power supply                                                                                   |  |  |

| 44  | TMCK/GPIO0 | Digital Input/Output       | Modulation 256fs system clock input. General-purpose I/O input/output pin.                             |  |  |

### WM8802

| PIN | NAME        | TYPE                 | DESCRIPTION                                                               |

|-----|-------------|----------------------|---------------------------------------------------------------------------|

| 45  | TBCK/GPIO1  | Digital Input/Output | Modulation 64fs bit clock input. General-purpose I/O input/output pin.    |

| 46  | TLRCK/GPIO2 | Digital Input/Output | Modulation fs clock input. General-purpose I/O input/output pin.          |

| 47  | TDATA/GPIO3 | Digital Input/Output | Modulation serial audio data input. General-purpose I/O input/output pin. |

| 48  | TXO/GPIOEN  | Digital Output/Input | Modulation data output. General-purpose I/O enable input pin.             |

Notes:

1. Input/output I or O = -0.3 to 3.6V, except annotated pins: -0.3 to +5.5V

2. Pins 32 and 33 are latch address setting input pins when pin 41 = Low.

3. Pin 34 is the demodulation function master or slave setting input pin when pin 41 = Low.

4. Pin 35 is the modulation function or general-purpose I/O function switch setting input pin when pin 41 = Low.

5. Perform ON/OFF for all power supplies with the same timing as a latch-up countermeasure.

# **ABSOLUTE MAXIMUM RATINGS**

Absolute Maximum Ratings are stress ratings only. Permanent damage to the device may be caused by continuously operating at or beyond these limits. Device functional operating limits and guaranteed performance specifications are given under Electrical Characteristics at the test conditions specified.

ESD Sensitive Device. This device is manufactured on a CMOS process. It is therefore generically susceptible to damage from excessive static voltages. Proper ESD precautions must be taken during handling and storage of this device.

| CONDITION                     | SYMBOL                         | CONDITIONS | MIN-MAX            |

|-------------------------------|--------------------------------|------------|--------------------|

| Maximum supply voltage        | AVDD <sub>max</sub>            | 1          | –0.3 to 4.6V       |

| Maximum supply voltage        | <b>DVDD</b> <sub>max</sub>     | 2          | –0.3 to 4.6V       |

| Input voltage 1               | V <sub>i1</sub>                | 3          | -0.3 to DVDD +0.3V |

| Input voltage 2               | V <sub>i2</sub>                | 4          | –0.3 to 5.8V       |

| Output voltage                | Vo                             | 5          | -0.3 to DVDD +0.3V |

| Storage ambient temperature   | T <sub>stg</sub>               |            | –55 to 125°C       |

| Operating ambient temperature | T <sub>opg</sub>               |            | –30 to 70 °C       |

| Maximum input/output current  | T <sub>i,</sub> T <sub>o</sub> | 6          | ±20mA              |

#### Notes:

- 1. AVDD pin

- 2. DVDD pin

- RX1, RBCK, RLRCK, XIN pins TMCK/GPI00, TBCK/GPI01, TLRCK/GPI02, TDATA/GPI03, TXO/GPI0EN pins

- 4. RX0, RX2, RX3, RX4, RX5/VI, RX6/UI pins SDIN, DI, CE, CL, XMODE pins

- 5. RXOUT, RMCK, RBCK, RLRCK, SBCK, SLRCK, RDATA pins

XMCK, XOUT, EMPHA/UO,  $\overline{\text{AUDIO}}$  /VO,  $\overline{\text{CKST}}$  ,  $\overline{\text{INT}}$  , RERR, DO pins

TMCK/GPIO0, TBCK/GPIO1, TLRCK/GPIO2, TDATA/GPIO3, TXO/GPIOEN pins

6. Per input/output pin

# **RECOMMENDED OPERATING CONDITIONS**

| PARAMETER             | SYMBOL           | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|-----------------------|------------------|-----------------|-----|-----|-----|------|

| Supply voltage        | AVDD, DVDD       |                 | 3.0 | 3.3 | 3.6 | V    |

| Input voltage range 1 | V <sub>IN1</sub> | 1               | 0   | 3.3 | 3.6 | V    |

| Input voltage range 2 | V <sub>IN2</sub> | 2               | 0   | 3.3 | 5.5 | V    |

| Operating temperature | V <sub>opq</sub> |                 | -30 | -   | 70  | °C   |

Notes:

1. RX1, RBCK, RLRCK, XIN pins

TMCK/GPIO0, TBCK/GPIO1, TLRCK/GPIO2, TDATA/GPIO3, TXO/GPIOEN pins

2. RX0, RX2, RX3, RX4, RX5/VI, RX6/UI pins SDIN, DI, CE, CL, XMODE pins

# **ELECTRICAL CHARACTERISTICS**

# DC CHARACTERISTICS

#### **Test Conditions**

DC Characteristics at  $T_a = 25^{\circ}$ C, AVDD = DVDD = 3.3V, AGND = DGND = 0V

| PARAMETER           | SYMBOL           | TEST CONDITIONS | MIN     | ТҮР | MAX    | UNIT |

|---------------------|------------------|-----------------|---------|-----|--------|------|

| Input, High         | V <sub>IH</sub>  | 1               | 0.7VDD  | -   | -      | V    |

| Input, Low          | V <sub>IL</sub>  |                 | -       | -   | 0.2VDD | V    |

| Input, High         | V <sub>IH</sub>  | 2               | 2.0     | -   | 5.8    | V    |

| Input, Low          | V <sub>IL</sub>  |                 | -0.3    | -   | 0.8    | V    |

| Output, High        | V <sub>OH</sub>  | 3               | VDD-0.8 | -   | -      | V    |

| Output, Low         | Vol              |                 | -       | _   | 0.4    | V    |

| Output, High        | V <sub>OH</sub>  | 4               | VDD-0.8 | _   | -      | V    |

| Output, Low         | Vol              |                 | -       | _   | 0.4    | V    |

| Output, High        | V <sub>OH</sub>  | 5               | VDD-0.8 | _   | -      | V    |

| Output, Low         | V <sub>OL</sub>  |                 | -       | -   | 0.4    | V    |

| Output, High        | V <sub>OH</sub>  | 6               | VDD-0.8 | -   | -      | V    |

| Output, Low         | V <sub>OL</sub>  |                 | -       | -   | 0.4    | V    |

| Input amplitude     | V <sub>PP</sub>  | 7               | 200     | -   | -      | mV   |

| Consumption current | V <sub>DD1</sub> | 8               | _       | 1.7 | 3.4    | mA   |

| Consumption current | V <sub>DD1</sub> | 9               | -       | 17  | 34     | mA   |

| Consumption current | V <sub>DD1</sub> | 10              | -       | 19  | 38     | mA   |

#### Notes:

- 1. CMOS levels: RX1, RBCK, RLRCK, XIN pins

- 2. TTL levels: Pins other than those listed above

- 3.  $I_{OH} = -12mA$ ,  $I_{OL} = 8mA$ : RMCK pin

- 4.  $I_{OH} = -8mA$ ,  $I_{OL} = 8mA$ : XMCK, XOUT pins

- 5.  $I_{OH} = -4mA$ ,  $I_{OL} = 4mA$ : RXOUT, RBCK, RLRCK, RDATA, SBCK pins SLRCK, TMCK/GPI00, TBCK/GPI01, TLRCK/GPI02 pins TDATA/GPI03, TXO/GPI0EN pins

- 6.  $I_{OH}$  = -2mA,  $I_{OL}$  = 2mA: Pins other than those listed above

- 7. Before capacitance of RX1 input pin

- 8. Demodulation function and oscillation amplifier stopped, modulation only, output sampling frequency = 96kHz

- 9. XIN continuous 24.576MHz oscillation, demodulation only, input sampling frequency = 96kHz

- 10. XIN continuous 24.576MHz oscillation, modulation, input/output sampling frequency = 96kHz

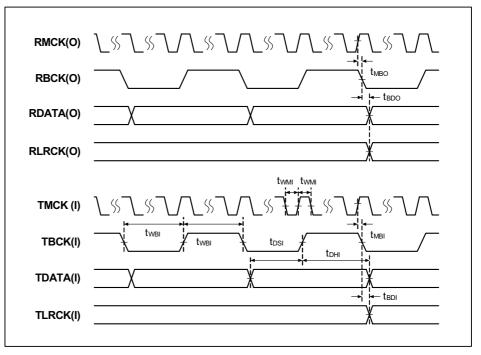

# **AC CHARACTERISTICS**

#### **Test Conditions**

AC Characteristics at  $T_a = 25^{\circ}$ C, AVDD = DVDD = 3.3V, AGND = DGND = 0V

| PARAMETER                        | SYMBOL           | TEST CONDITIONS | MIN | TYP    | MAX | UNIT |

|----------------------------------|------------------|-----------------|-----|--------|-----|------|

| RX0 TO RX6 sampling<br>frequency | f <sub>RFS</sub> |                 | 28  | _      | 195 | kHz  |

| XIN clock frequency              | f <sub>XF1</sub> | 1               | 8   | 12.288 | 19  | MHz  |

| XIN clock frequency              | f <sub>XF2</sub> | 2               | 20  | 24.576 | 30  | MHz  |

| RMCK clock frequency             | f <sub>RCK</sub> |                 | 4   | -      | 100 | MHz  |

| RMCK clock jitter                | tj               |                 | _   | 200    | -   | ps   |

| RMCK, RBCK delay                 | t <sub>MBO</sub> |                 | _   | -      | 10  | ns   |

| RBCK, RDATA delay                | t <sub>BDO</sub> |                 | _   | -      | 10  | ns   |

| RMCK, SBC delay                  | t <sub>MBO</sub> | 3               | _   | -      | 10  | ns   |

| SMCK, RDATA delay                | t <sub>BDO</sub> | 4               | _   | -      | 10  | ns   |

| TMCK input pulse width           | t <sub>WMI</sub> |                 | 10  | -      | -   | ns   |

| TBCK input pulse width           | t <sub>WBI</sub> |                 | 40  | -      | -   | ns   |

| TLRCK sampling frequency         | f <sub>TFS</sub> |                 | 28  | -      | 195 | kHz  |

| TBCK, TDATA setup                | t <sub>DSI</sub> |                 | _   | 20     | -   | ns   |

| TBCK, TDATA hold                 | t <sub>DHI</sub> |                 | _   | 20     | _   | ns   |

| TMCK, TBCK delay                 | t <sub>MBI</sub> |                 | _   | -      | 10  | ns   |

| TBCK, TDATA delay                | t <sub>BDI</sub> |                 | _   | _      | 10  | ns   |

#### Notes:

1. XINSEL = "0" setting, 12.288MHz must be set when calculating input sampling frequency

2. XINSEL = "1" setting, 24.576MHz must be set when calculating input sampling frequency

3. When RMCK and SBCK source clocks are the same

4. When SBCK is the PLL source clock

Figure 1 AC Characteristics

# WM8802

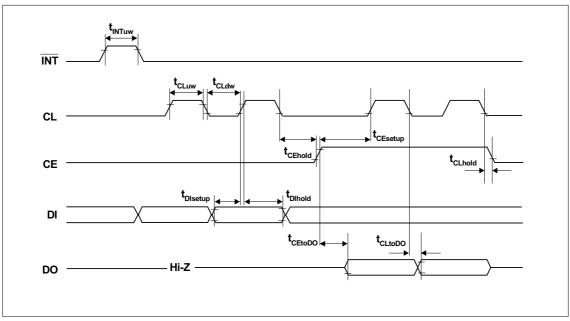

# MICROCONTROLLER INTERFACE AC CHARACTERISTICS

## **Test Conditions**

| I/F AC Characteristics at T <sub>a</sub> = 25°C, AVDD = DVDD = 3.3V, AGND = DGND = 0V |                       |                 |     |      |     |      |

|---------------------------------------------------------------------------------------|-----------------------|-----------------|-----|------|-----|------|

| PARAMETER                                                                             | SYMBOL                | TEST CONDITIONS | MIN | TYP  | MAX | UNIT |

| XMODE pulse width, Low                                                                | t <sub>RST dw</sub>   |                 | 200 | -    | -   | μs   |

| INT pulse width, Low                                                                  | t <sub>INT uw</sub>   | 1               | 5   | 1/fs | 36  | μs   |

| CL pulse width, Low                                                                   | t <sub>CL dw</sub>    |                 | 100 | -    | -   | ns   |

| CL pulse width, High                                                                  | t <sub>CL uw</sub>    |                 | 100 | -    | -   | ns   |

| CL, CE setup time                                                                     | t <sub>CL setup</sub> |                 | 50  | -    | -   | ns   |

| CL, CE hold time                                                                      | t <sub>CE hold</sub>  |                 | 50  | -    | -   | ns   |

| CL, DI setup time                                                                     | t <sub>DI setup</sub> |                 | 50  | _    | -   | ns   |

| CL, DE hold time                                                                      | t <sub>DI hold</sub>  |                 | 50  | -    | -   | ns   |

| CL, CE hold time                                                                      | t <sub>CL hold</sub>  |                 | 50  | -    | -   | ns   |

| CL, DO delay time                                                                     | t <sub>CL to DO</sub> |                 | -   | _    | 20  | ns   |

| CE, DO delay time                                                                     | t <sub>CE to DO</sub> |                 | _   | _    | 20  | ns   |

## Notes:

1. When INTOPF is set to "1", fs = input sampling frequency

## Figure 2 Micro-controller Interface AC Characteristics

# **DEVICE DESCRIPTION**

# **INITIAL SYSTEM SETTINGS**

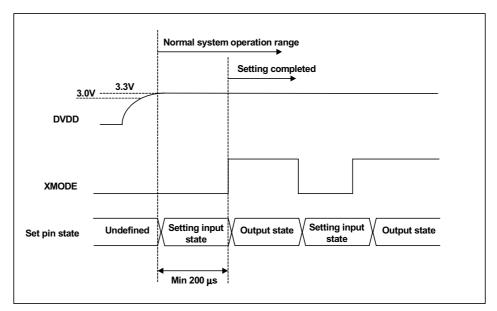

# SYSTEM RESET (XMODE)

The system operates normally when XMODE is set to High after applying a supply voltage of 3.0V or greater. Following power ON, the system is reset by setting XMODE to Low again.

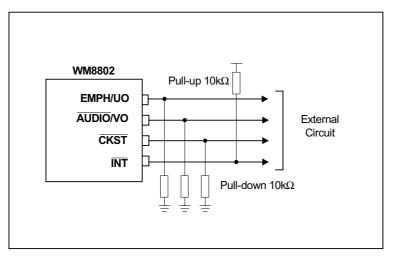

A 10k $\Omega$  pull-down or pull-up resistor can be used to set EMPHA/UO, AUDIO/VO, CKST and INT for the following:

- chip address

- demodulation function master or slave

- modulation function or general-purpose I/O function settings

If EMPHA/UO,  $\overline{\text{AUDIO}}$  /VO,  $\overline{\text{CKST}}$ , and  $\overline{\text{INT}}$  are not pulled up or down, their state is undefined. A pull-up or pull-down resistor should always be connected to these pins.

| SETTING                                                 | PINS               |

|---------------------------------------------------------|--------------------|

| Chip address                                            | EMPHA/UO, AUDIO/VO |

| Demodulation function master or slave                   | CKST               |

| Modulation function or general-<br>purpose I/O function | INT                |

Table 1 Pin Names and Settings

Figure 3 Setting Timing Chart of Function Setting Input Pins

# CHIP ADDRESS SETTINGS (EMPHA/UO, AUDIO /VO)

The WM8802 comes with a function to set a unique chip address to allow the use of several WM8802 on the same micro-controller bus.

A 10k $\Omega$  pull-down or pull-up resistor is used to set EMPHA/UO and AUDIO /VO as the chip address settings. This allows up to set 4 chip addresses.

Chip addresses in the micro-controller interface can be set with CAL and CAU provided that they are first two bits on the LSB side. CAL and CAU corresponds to the lower and higher chip address respectively.

Address writing to a particular device is enabled by making the chip address setting, using EMPHA/UO and AUDIO /VO, the same as the chip addresses sent from the micro-controller.

The chip address setting must be performed even when using only one WM8802 in the system. The chip address is undefined and control from the micro-controller cannot be performed if the chip address setting is not performed. While XMODE is Low and the micro-controller is not used the state of the chip address setting pin is undefined,. Be sure to connect either A pull-down resistor or a pullup resistor should be connected to EMPHA/UO and AUDIO /VO.

| AUDIO /VO | EMPHA/UO  | CAU | CAL |

|-----------|-----------|-----|-----|

| Pull-down | Pull-down | 0   | 0   |

| Pull-down | Pull-up   | 0   | 1   |

| Pull-up   | Pull-down | 1   | 0   |

| Pull-up   | Pull-up   | 1   | 1   |

Table 2 Chipset Address Settings

Figure 4 Function Setting Input Pin Setting Example

#### Notes:

3.

Chip address setting 1.

- => CAL = CAU = 0

- 2. Demodulation function master or slave setting

- => Master

- Modulation function or general purpose I/O port switch => General purpose I/O port

- function

# DEMODULATION FUNCTION MASTER/SLAVE SETTINGS (CKST)

A master/slave function allows multi-channel synchronized transfer using multiple WM8802 devices. A 10k $\Omega$  pull-down or a pull-up resistor should be connected to CKST to set this function.

Set the master mode when using only one WM8802. When using multiple WM8802 devices, set one to the master mode and the others to slave mode.

In order to perform multi-channel transfer when using multiple WM8802 devices, RBCK and RLRCK (output) should be connected as the master and RLRCK (input) as the slave. XMCK of the master device should be connected to XIN of the slave device. The same polarity should be set for RBCK and RLRCK and the same frequency for XIN and XMCK.

Some of the output data maybe dropped or read twice on the slave side if the input data sampling frequency or the phase between the master and slave differ. This can also be true if the clock sources differ even though the sampling frequencies are the same. This phenomenon can be checked using the  $\overline{\rm INT}$  pin and the micro-controller interface.

| CKST      | MODE        |

|-----------|-------------|

| Pull-down | Master mode |

| Pull-up   | Slave mode  |

Table 3 Master/Slave Switching

| PIN   | MASTER MODE | SLAVE MODE |

|-------|-------------|------------|

| RMCK  | Output      | Low        |

| RBCK  | Output      | Input      |

| RLRCK | Output      | Input      |

Table 4 Clock Pin State

# MODULATION FUNCTION AND GENERAL-PURPOSE I/O PORT SWITCHING (INT)

The modulation function and the general-purpose I/O function share the same pin and therefore cannot be used simultaneously.

A 10k $\Omega$  pull-down or pull-up resistor can be connected to  $\overline{\text{INT}}$  to select the function listed in Table 5.

| INT STATE | FUNCTION             |

|-----------|----------------------|

| pull-down | Modulation f unction |

| Pull-up   | General-purpose I/O  |

Table 5 Modulation Function and General-Purpose I/O Switching

# DESCRIPTION OF DEMODULATION FUNCTION

The demodulation function operation settings are performed using RXOPR.

CLOCKS

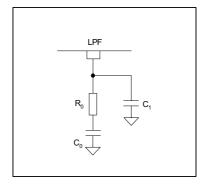

# PLL (LPF)

The VCO (Voltage Controlled Oscillator) can be stopped if PLLOPR is set. Synchronization to frequencies from 32kHz to 192kHz and RMCK of 4MHz to 25MHz can be selected.

The PLL clock frequency is selected with PLLSEL. For systems with an input data sampling frequency of 105kHz or lower, the initial setting of 512fs is recommended. Since the system clock RMCK output initial value is set to 1/2 of PLLSEL, the RMCK output is 256fs when a PLL clock frequency of 512fs is used.

For systems with an input data sampling frequency higher than 105kHz, the PLL clock frequency should be set to 256fs. RMCK will be 128fs if PRSEL0 is set to 1 and the same initial output setting (i.e. 256fs) is used,

LPF is a PLL loop filter pin. Resistances and capacitances should be selected in accordance with the frequency of the PLLSEL system clock. The PLLSEL setting should be set prior to bi-phase data input since PLLSEL switching involves a change in LPF loop filter constant.

Figure 5 Loop Filter Configuration

| PLLCK1 | PLLCK0 | R0    | C0      | C1       |

|--------|--------|-------|---------|----------|

| 0      | 0      | 150Ω  | 0.047µF | 0.0068µF |

| 0      | 1      | 13022 | 0.047μΡ | 0.0000μΓ |

| 1      | 0      |       | 0.000 5 | 0.0047 E |

| 1      | 1      | 220Ω  | 0.068µF | 0.0047µF |

Table 6 Loop Filter Component Values

#### DEMODULATION FUNCTION WITHOUT USING PLL (TMCK)

The WM8802 has a function to process input bi-phase data using an external clock (external synchronization function). In normal demodulation processing, the clock is generated in synchronization with data by the built-in PLL; the data processing is performed using this clock. It is possible to perform data processing by supplying a data synchronized clock instead of the clock generated by the PLL via an independent transmission path.

The demodulation function can be used to set external synchronization function without using the PLL by EXSYNC. PLLSEL should be set to 256fs and PRSEL0 should be set to 1 (setting frequency to 1/1). The 256fs clock should then be synchronized with the input data to TMCK. As a result of these settings, the same operation occurs as PLL demodulation processing with a 256fs clock. LPF should remain unconnected as no loop filter is required.

The external synchronization function settings should be completed prior to bi-phase data input (paying attention to the bandwidth of clock transmission path).

A high-precision clock system using an external PLL can also be configured by using the external synchronization function.

#### **OSCILLATION AMPLIFIERS (XIN, XOUT, MCK)**

The WM8802 features a built-in oscillation amplifier. An oscillation circuit can be configured by connecting a crystal resonator, feedback resistor and load capacitance across XIN and XOUT. When connecting a crystal resonator, use a fundamental crystal resonator. Note that the load capacitance depends on the crystal resonator characteristics.

The output of an external clock supply source should be connected to XIN if the built-in oscillation amplifier is not used as the clock source. In this configuration it is not necessary to connect a feedback resistor between XIN and XOUT.

A 12.288MHz or 24.576MHz clock can be supplied to XIN by setting XINSEL. If input frequency to XIN changes it is necessary to set FSERR to 1, so that when the input data sampling frequency changes, the result is not reflected in the error flag. Since the input frequency is then different to the recommended frequency operation, the encoding result cannot be used for input fs calculations. In this case, the input fs can be calculated by performing decimal division of the count value (FSDAT) with 1/2000th of the XIN input frequency. For details, see Micro-controller Interface section.

Since the XIN clock serves as the reference for internal processing, the XINSEL setting should be completed prior to bi-phase data input.

A clock should be supplied to XIN at the following times:

- (1) Detection of bi-phase data input

- (2) Clock source during PLL unlock

- (3) Input data sampling frequency calculation

- (4) Time definition during input data switching

- (5) External supply clock source (AD converter clock, etc.)

The oscillation amplifier automatically stops when the PLL is locked. However, it can also be set for continuous operation with AMPOPR set to 1. Setting the continuous operation mode enables input data detection and input sampling frequency calculation even when the PLL is locked; this has an effect on the sound quality because the oscillation amplifier and PLL clock coexist.

RERR outputs an error (High) once the PLL is locked if the oscillation amplifier is set to continuous operation by setting AMPOPR to 1. This occurs because, at the same time that the oscillation amplifier goes into the operating state, the fs calculation value that is held when operation is stopped, is reset. This error has no influence on the clock output, but RDATA is muted while this error occurs. Therefore, the AMPOPR[0:1] setting must be completed either prior to bi-phase data input or during PLL unlock.

The oscillation amplifier can be stopped if it is unnecessary. When operation is resumed it is recommended to return to the normal operation after an interval of 10ms or longer to allow the resonator oscillation to stabilise.

XMCK outputs the XIN clock. The XMCK output settings are performed with XMSEL[0:1]. The XIN clock can be set to 1/1, 1/2 or muted output.

No clock is needed for XIN when only using the modulation function. In this case, the built-in oscillation amplifier and frequency divider are used for RMCK, RBCK, and RLRCK clock generation. Input the crystal resonator frequency across XIN and XOUT (if using only the oscillation amplifier) or an external clock to XIN. The potential of digital data input pins RX0 to RX6 should be fixed. The DIR function is stopped using RXOPR and PLLOPR and should not be set at this time. The output clock may also be muted.

## MASTER CLOCK AND CLOCK SOURCE SWITCHING

The RMCK, RBCK, and RLRCK, and the SBCK and SLRCK (see below) clock sources can be selected from the following three master clocks.

| (1) | PLL source  | (256fs or 512fs)         |

|-----|-------------|--------------------------|

| (2) | XIN source  | (12.288MHz or 24.576MHz) |

| (3) | TMCK source | (256fs)                  |

Clock source switching can be done in one of two ways, either by setting the R system and the S system on an interconnected basis or fixing the S system to the XIN source and setting only the R system. This setting is performed using SELMTD, OCKSEL and RCKSEL.

The clock source is automatically switched between PLL clock and XIN clock by locking/unlocking the PLL. The continuity of the clock is maintained at this time. However, if switching the clock source with SELMTD, the continuity of the S system is not maintained.

The clock source can be switched to XIN using OCKSEL and RCKSEL, regardless of the PLL status. The clock source switch command and clock output of the R and S systems are shown below.

| SELMTD | R SYSTEM OUTPUT CLOCK | S SYSTEM OUTPUT CLOCK |

|--------|-----------------------|-----------------------|

| 0      | According to OCKSEL   | According to OCKSEL   |

| 1      | According to RCKSEL   | Fixed to XIN source   |

Table 7 Correspondence between Clock Source Switch Commands and Clock Output Pins

| SELMTD | OCKSEL RCKSEL |   | SELMTD OCKSEL RCH |          |        | M CLOCK<br>RCE |  | M CLOCK<br>IRCE |

|--------|---------------|---|-------------------|----------|--------|----------------|--|-----------------|

|        |               |   | Locked            | Unlocked | Locked | Unlocked       |  |                 |

| 0      | 0             | Х | PLL               | XIN      | PLL    | XIN            |  |                 |

| 0      | 1             | х | XIN               | XIN      | XIN    | XIN            |  |                 |

| 1      | Х             | 0 | PLL               | XIN      | XIN    | XIN            |  |                 |

| 1      | Х             | 1 | XIN               | XIN      | XIN    | XIN            |  |                 |

Table 8 Relationship between Clock Source Switch Commands and

#### Clock Sources when PLL Locked/Unlocked

The TMCK source is selected using EXSYNC. This setting results in the same operation as when 256fs is set with the PLL source (i.e. PLLSEL set to 256fs).

The various clocks are output with the TMCK source as the master clock and the PLL clock status is output if data synchronised with TMCK is input. The XIN source is switched with OCKSEL and RCKSEL. When the TMCK source is not supplied or the input data is not synchronized, the source is switched to the XIN source; this is similar to the PLL source unlocked status.

The PLL status can always be monitored with RERR even after the XIN source is switched. The processed information can also be read with the micro-controller interface regardless of the PLL status.

When the PLL changes from locked to unlocked status, the timing for switching the clock from the PLL source to the XIN source can be changed with XTWT[0:1]. It is recommended to use these commands if noise occurs during clock switching.

#### CAUTIONS ON SWITCHING CLOCK SOURCE WHILE PLL IS LOCKED

Clock continuity is maintained when switching the clock to the XIN source with SELMTD, OCKSEL, and RCKSEL. RERR outputs an error (High) when the oscillation amplifier is stopped while the PLL is locked (initial setting). The oscillation amplifier goes into the operating state at the same time that the clock is switched to the XIN source and calculation of the input fs (sampling frequency) resumes. The previous fs calculation value is then reset. The processing performs as if the fs value had changed compared to the newly calculated fs value.

The following settings must be performed in order to switch the clock source with SELMTD, OCKSEL and RCKSEL while PLL is locked and maintaining the RERR status.

- (1) Set the oscillation amplifier to the continuous operation mode with AMPOPR[0:1].

- (2) Set with FSERR the mode for not reflecting fs changes to the error flag.

By performing one of the above settings, it is possible to control the RERR change status when switching the clock source with SELMTD, OCKSEL and RCKSEL.

When switching the clock source to XIN (oscillation amplifier stopped and PLL locked), the output clock is output after the oscillation amplifier starts operating. When switching the clock source from XIN to PLL the clock continuity is maintained.

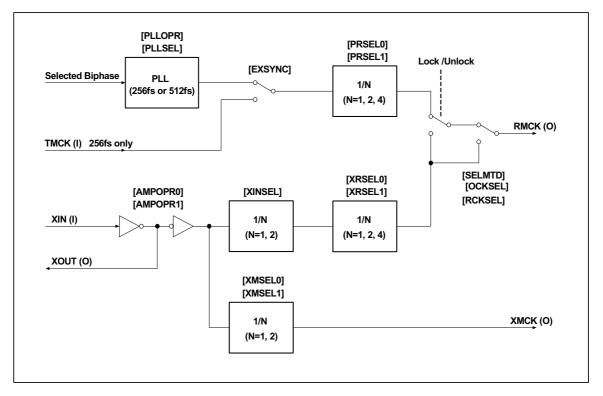

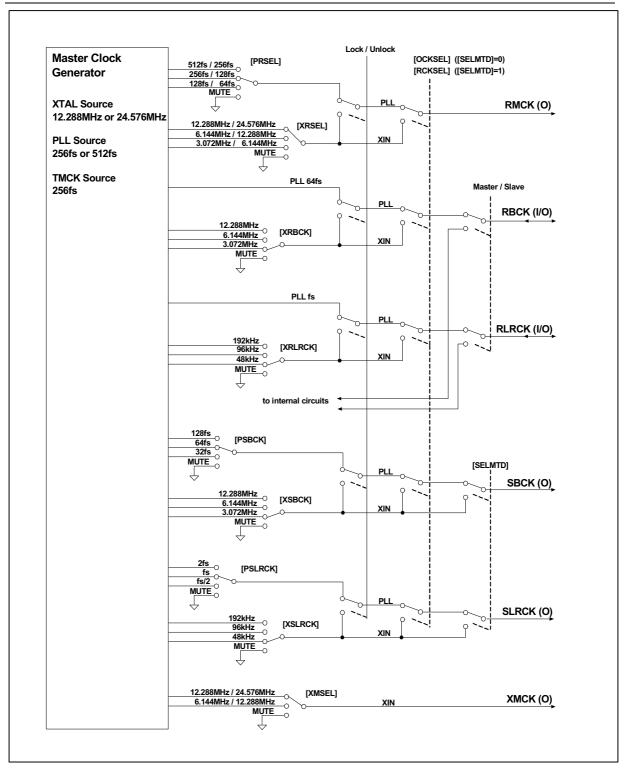

#### MASTER CLOCK BLOCK DIAGRAM (TMCK, XIN, XOUT, RMCK, XMCK)

The relationships between the three master clocks, switching and the frequency division function are shown below.

The contents in the square brackets [\*\*\*] of the switch function blocks correspond to the write command names.

Lock/Unlock switching is automatically performed through PLL locking/unlocking.

Figure 6 Master Clock Block Diagram

## OUTPUT CLOCKS (RMCK, RBCK, RLRCK, SBCK, SLRCK)

The WM8802 features two clock systems in order to supply the various clocks for the A/D converter, DSP and other peripheral devices.

The clock output settings for the R and S systems are set using PRSEL[0:1], XRSEL[0:1], XRBCK[0:1], XRLRCK[0:1], PSBCK[0:1], XRLRCK[0:1], and XSLRCK[0:1].

## (a) Setting range for clock output pins when using the PLL source

- (1) RMCK: 1/1, 1/2, and 1/4 of 512fs or 256fs

- (2) RBCK: 64fs output

- (3) RLRCK: fs output

- (4) SBCK: 128fs, 64fs, and 32fs

- (5) SLRCK: 2fs, fs, and fs/2

#### (b) Setting range for clock output pins when using the XIN source

- (1) RMCK: 1/1, 1/2, and 1/4 of 12.288MHz or 24.576MHz

- (2) RBCK: 12.288MHz, 6.144MHz, and 3.072MHz

- (3) SBCK: 12.288MHz, 6.144MHz, and 3.072MHz

- (4) RLRCK: 192kHz, 96kHz, and 48kHz

- (5) SLRCK: 192kHz, 96kHz, and 48kHz

The polarity of RBCK, RLRCK, SBCK and SLRCK can be reversed with RBCKP, RLRCKP, SBCKP and SLRCKP.

Clock switching is processed on the rising edge of the RLRCK output after the falling edge of microcontroller interface CE.

| OUTPUT PIN NAME | PLL S | OURCE | TMCK<br>SOURCE | XIN SC    | DURCE     |

|-----------------|-------|-------|----------------|-----------|-----------|

|                 | 512fs | 256fs | 256fs          | 12.288MHz | 24.576MHz |

|                 | 512fs | 256fs | 256fs          | 12.288MHz | 24.576MHz |

| RMCK            | 256fs | 128fs | 128fs          | 6.144MHz  | 12.288MHz |

|                 | 128fs | 64fs  | 64fs           | 3.072MHz  | 6.144MHz  |

|                 |       |       |                | 12.28     | 8MHz      |

| RBCK            |       | 64fs  |                | 6.144     | MHz       |

|                 |       |       |                | 3.072     | 2MHz      |

|                 |       |       |                | 192       | kHz       |

| RLRCK           |       | fs    |                | 96kHz     |           |

|                 |       |       |                | 48k       | κHz       |

|                 |       | 128fs |                | 12.28     | 8MHz      |

| SBCK            |       | 64fs  |                | 6.144MHz  |           |

|                 |       | 32fs  |                | 3.072     | 2MHz      |

|                 |       | 2fs   |                | 192       | kHz       |

| SLRCK           |       | fs    |                | 96k       | Hz        |

|                 |       | fs/2  |                | 48        | Hz        |

Table 9 Output Clock Frequencies (Bold Items = Initial Settings)

PP Rev 1.1 April 2004

# OUTPUT CLOCKS BLOCK DIAGRAM (RMCK, RBCK, RLRCK, SBCK, SLRCK, XMCK)

The relationships between the output clock and switch function are shown below.

Master Clock Generator in the figure indicates the PLL source, TMCK source or the XIN source.

The contents in the square brackets  $[\ast\ast\ast]$  of the switch function blocks correspond to the write command names.

The broken lines connecting the switches indicate coordinated switching.

Lock/Unlock switching is automatically performed through PLL locking/unlocking.

Master/slave switching is done through demodulation function master/slave function switching.

#### Figure 7 Clock Output Block Diagram

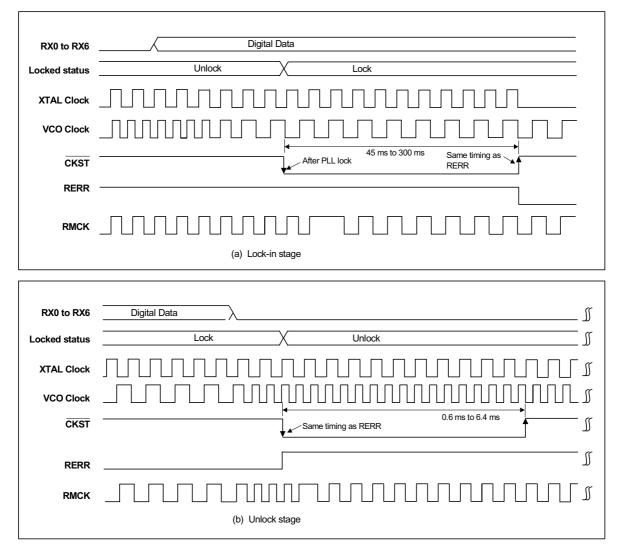

#### CLOCK SWITCH TRANSITION SIGNAL OUTPUT (CKST)

CKST outputs Low when the output clock changes during PLL lock/unlock.

In the lock-in stage (PLL locked following the detection <u>of input</u> data) the  $\overrightarrow{\text{CKST}}$  Low pulse falls at the word clock edge generated from the XIN clock. The  $\overrightarrow{\text{CKST}}$  Low pulse rises at the same timing as RERR following the lapse of a given period.

In the unlock stage, the CKST Low pulse falls at the same timing as the PLL lock detection signal RERR and rises following a given number of word clocks generated from the XIN clock.

The <u>PLL</u> lock status change and clock change timing is detected by the rising and falling edges of the CKST Low pulse.

Figure 8 Clock Switch Timing

## **BI-PHASE SIGNAL INPUT / OUTPUT**

#### **BI-PHASE SIGNAL INPUT RECEPTION RANGE**

The input data reception range depends on the PLL lock frequency setting set by PLLSEL. The relationship between this setting and the guaranteed reception range is shown below.

| PLL OUTPUT CLOCK SETTING | INPUT DATA RECEPTION RANGE |

|--------------------------|----------------------------|

| 512fs (PLLSEL = 0)       | 28kHz to 105kHz            |

| 256fs (PLLSEL = 1)       | 28kHz to 195kHz            |

#### Table 10 Relationship Between PLL Output Clock Setting and Reception Range (FSLIM[0:1] = 0)

The fs reception range for input data within the above PLL output clock setting range can be controlled. This setting is performed using FSLIM[0:1]. When this function is used, input data that exceeds the setting range is considered as an error and the clock source is automatically switched to the XIN source. The RDATA output data then depends on the RDTSEL setting.

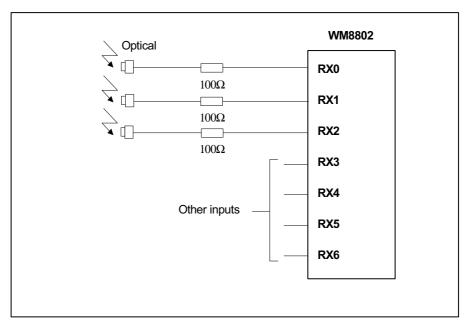

#### **BI-PHASE SIGNAL INPUT/OUTPUT PINS (RX0 TO RX6, RXOUT)**

There are 7 digital data input pins. Data modulated with the modulation function can also be selected, therefore selection from a total of 8 signals is possible. However, the pins that can be selected are restricted by the following conditions:

- 1. The six pins RX0 and RX2 to RX6 are TTL level input pins with 5V input level tolerable.

- 2. RX1 is a coaxial-compatible input pin with built-in amplifier that can receive up to 200mVp-p data.

The demodulation input and RXOUT output signals can also be selected independently.

- 1. The demodulation data is selected with RISEL[0:2].

- 2. The RXOUT output data is selected with ROSEL[0:2].

RXOUT can be muted with RXOFF. Muting is recommended when not using RXOUT in order to reduce clock jitter.

The data input status can be monitored with the RXMON setting. The status of each data input pin is stored in CCB address 0xEA and output registers DO0 to DO7. Since this function uses the XIN clock, the oscillation amplifier must be set to the continuous operation mode when RXMON is set.

Demodulation input pin switching can be performed during PLL unlock using the ULSEL setting. As a result, data switching can be accurately communicated to peripheral devices.

The interval from pin switching through RISEL[0:2] until data is received is about 250µs to 350µs. This function also requires that the oscillation amplifier is set to the continuous operation mode.

| Input pin selection  | RX0 | RX2 | RX3 | RX1          |

|----------------------|-----|-----|-----|--------------|

| ternal supply signal | RX0 | RX2 | RX3 | RX1          |

|                      |     |     |     | <b>←</b> →¦  |

|                      |     |     | 250 | )μs to 350μs |

Figure 9 Input Pin Selection Processing via PLL Unlock

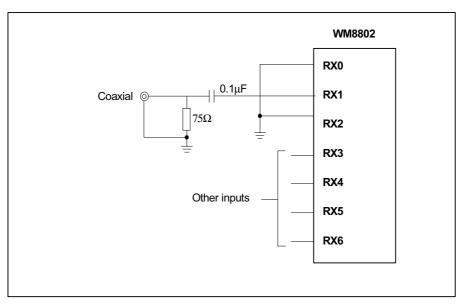

#### **BI-PHASE SIGNAL INPUT CIRCUITS (RX0, RX1, RX2)**

If RX1, which has a built-in amplifier, is used as a coaxial input signal corruption may occur due to the influence of the adjacent RX0 and RX2 input pins. RX0 and RX2 should be fixed to Low to prevent them from influencing RX1.

The input signal to RX1 is temporarily open if RX1 is selected. The RX0 and RX2 potential must be fixed due to coupling effects. In this case, 5 bi-phase signal input pins can be selected; RX1 and RX3 to RX 6.

If the input signal to RX1 is absolutely fixed to either High or Low then all 7 input pins can be used.

Figure 11 Bi-Phase Signal Input Circuits – Optical Input Circuit

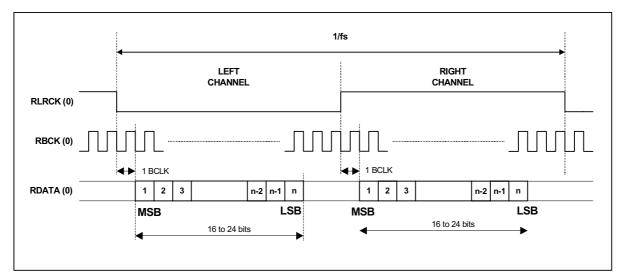

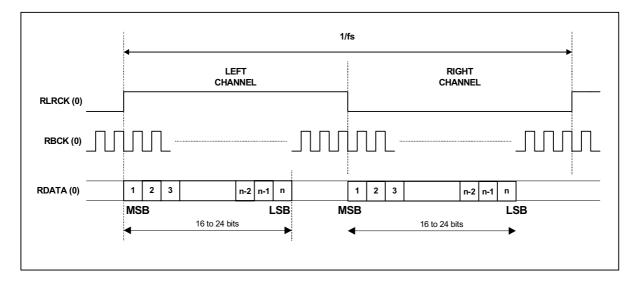

# SERIAL AUDIO DATA INPUT/OUTPUT

## **OUTPUT DATA FORMAT (RDATA)**

The output format is set with OFSEL[0:2].

$\mathsf{I}^2\mathsf{S}$  is the initial output format setting.

Right Justified outputs are only valid in master mode.

Output data is output in synchronization with the RLRCK edge immediately after the RERR output becomes Low.

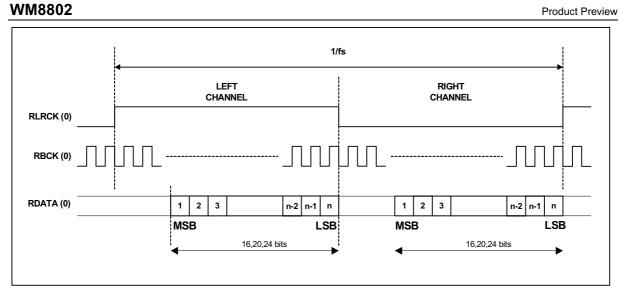

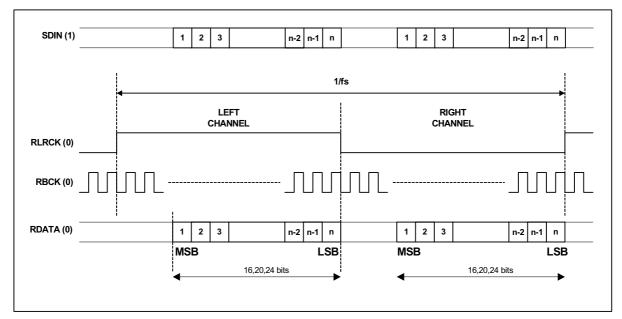

Figure 12 Data Output Timing – I2S

Figure 14 Data Output Timing – Right Justified

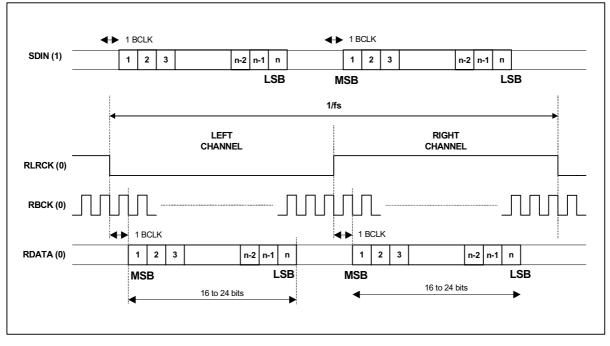

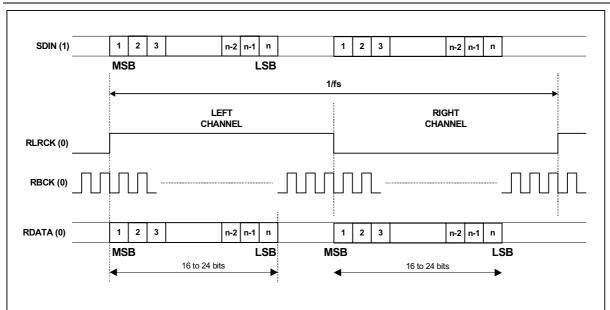

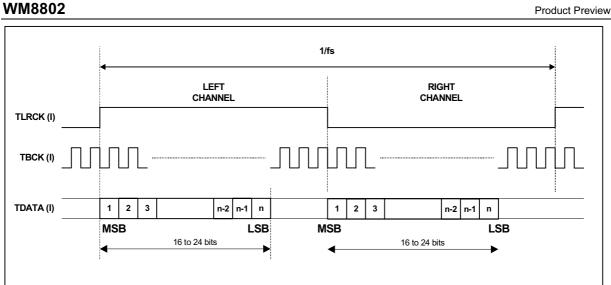

## SERIAL AUDIO DATA INPUT FORMAT (SDIN)

SDIN is a 24 bit serial digital audio data input pin.

The format of the serial audio data input to SDIN is the same as the demodulation data output format.

Figure 16 Serial Audio Data Input Timing – Left Justified

Figure 17 Serial Audio Data Input Timing – Right Justified

#### OUTPUT DATA SWITCHING (SDIN, RDATA)

RDATA demodulation data is output when the PLL is locked and the SDIN input is selected This switching is automatically performed according to the locked/unlocked status of the PLL. For details, see the timing charts below.

Switch to a clock source synchronized to the SDIN data when SDIN input data is selected.

The SDIN input data can be output to RDATA regardless of the locked/unlocked status of the PLL using RDTSTA setting.

The RDATA output data can be forcibly muted using the RDTMUT setting.

The PLL continues operating when the clock source is set to XIN using OCKSEL and RCKSEL as long as its operation is not stopped using PLLOPR. The PLL status is continuously output from RERR as long as error output is not forcibly set with RESTA. The processed information can also be read with the micro-controller interface regardless of the PLL status.

| PLL locked status | UNLOCK        | LOCK                   |                   |

|-------------------|---------------|------------------------|-------------------|

| CKST              |               |                        |                   |

| RERR              |               |                        |                   |

| RDATA             | SDIN data     | Muted                  | Demodulation data |

|                   |               |                        |                   |

|                   | (a) L         | ock-in stage           |                   |

| PLL locked status | (a) L<br>LOCK | ock-in stage<br>UNLOCK |                   |

| PLL locked status |               |                        |                   |

| PLL locked status |               |                        |                   |

Figure 18 RDATA Output Data Switch Timing Chart

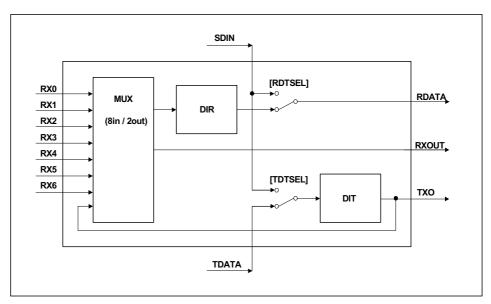

#### DATA BLOCK DIAGRAM (RX0 TO RX6, TX0, RXOUT, TDATA, RDATA, SDIN)

The RDATA output data is switched to SDIN input data using RDTSEL.

The SDIN input data can be input to the modulation function using TDTSEL.

The modulation output is an input to the Input Switch Multiplexer and can be output from RXOUT. It is possible to use a signal that has been digitized with an A/D converter for digital recording output, etc. using this function.

Figure 19 Data Block Diagram

## CALCULATION OF INPUT DATA SAMPLING FREQUENCY

The input data sampling frequency is calculated using the XIN clock.

When the oscillation amplifier automatically stops during PLL lock, the input data sampling frequency is calculated during the RERR error period. The calculation is completed at the same time that the oscillation amplifier stops. The value remains unchanged until the PLL becomes unlocked.

In the mode where the oscillation amplifier operates continuously, calculation processing is performed continuously The calculation results (which follows the input data) can be read even if sampling rate is changed within the PLL capture range, but only for a signal where channel status sampling information does not change,.

The calculation result can be read from CCB address 0xEB and output to registers DO4 to DO7 and DO8 to DO15. Registers DO4 through DO7 hold the encoded result, while DO8 through DO15 hold the calculation value. The sampling frequencies that can be calculated are greater than 24kHz as the calculation count value is output in 8-bit units. For details, see section Micro-controller Interface.

## **ERROR OUTPUT PROCESSING**

## LOCK ERROR, DATA ERROR OUTPUT (RERR)

An error flag RERR is output when a PLL lock error or a data error occurs.

Non-PCM data reception can be treated as an error with the RESEL setting.

The RERR output conditions are set using RESTA. Since the PLL status can be output at any time, the PLL status can be monitored even when the clock source is XIN.

#### PLL LOCK ERROR

The PLL becomes unlocked for input data that has lost bi-phase modulation regularity or input data where preambles B, M, and W cannot be detected.

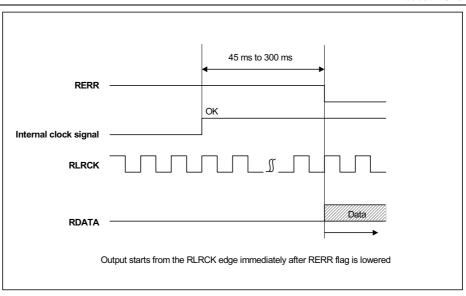

RERR goes High during the occurrence of a PLL lock error and returns to Low when data demodulation returns to normal. High is maintained between 45ms and 300ms.

The rising and falling edges of RERR are synchronized with RLRCK.

#### **INPUT DATA PARITY ERROR**

Input parity errors are detected if there are an odd number of parity bits in input data.

RERR goes High indicating that the PLL is locked if an input parity error occurs 9 or more times in succession, It returns to Low after being High for between 45ms and 300ms.

The error flag output format, for when an input parity error is output 8 times in succession, can be selected using REDER.

#### **OTHER ERRORS**

The channel status bits 24 to 27 (sampling frequency) are always read and the data of the previous block is compared with the current data, even if RERR goes Low. The input data sampling frequency is also calculated from the fs clock extracted from the input data and fs calculation value comparison is performed as described above. RERR is instantly made High if a difference is detected, and the same processing as for PLL lock errors is performed.

The PLL causes a lock error when the sampling frequency changes as described above. FSERR can be set to support sources with a variable sampling frequency (for example a CD player with a variable pitch function). No error flag is output if the sampling frequency variation falls within the PLL capture range while using FSERR.

For input data within the reception range, FSERR prevents fs calculation results from being reflected in the error flag that is set using FSLIM[0:1]. RERR goes Low if the PLL status changes to the locked status.

RERR changes to a High output upon detection of non-PCM data input if RESEL is set. The PLL locked status and various output clocks continue to be output according to the input data but the output data is muted.

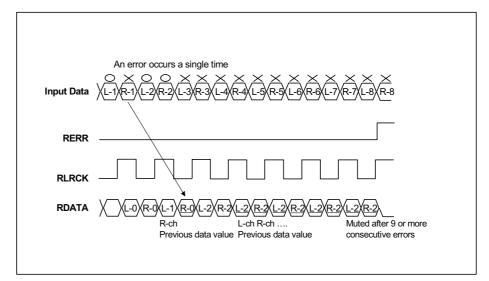

# DATA PROCESSING UPON ERROR OCCURRENCE (LOCK ERROR, PARITY ERROR)

The data processing after the occurrence of an error is described below. If 8 or fewer input parity errors occur in succession transfer data is replaced by the data saved to L-ch and R-ch in the previous frame of PCM audio data. The error data is output as it is if the transfer data is non-PCM data. Non-PCM data is based on data detected prior to occurrence of an input parity error when bit 1 of the channel status goes High.

Output data is muted upon occurrence of a PLL lock error or when a parity error occurs 9 or more times in succession.

For the channel status, the data of the previous block is held in 1-bit units when a parity error occurs.

| DATA                  | PLL LOCK<br>ERROR | INPUT PARITY<br>ERROR (A) | INPUT PARITY<br>ERROR (B) | INPUT PARITY<br>ERROR (C) |

|-----------------------|-------------------|---------------------------|---------------------------|---------------------------|

| RDATA output          | Low               | Low                       | Previous value data       | Output                    |

| fs calculation result | Low               | Output                    | Output                    | Output                    |

| Channel status        | Low               | Low                       | Previous value data       | Previous value data       |

| Validity flag         | Low               | Low                       | Output                    | Output                    |

| User data             | Low               | Low                       | Output                    | Output                    |

Table 11 Data Processing upon Error Occurrence

#### Notes:

- 1. Input parity error (A): Occurs 9 or more times in succession

- 2. Input parity error (B): Occurs 8 or fewer times in succession, in case of audio data

- 3. Input parity error (C): Occurs 8 or fewer times in succession, in case of non-PCM burst data

Figure 20 shows an example of data processing upon occurrence of a parity error.

Figure 20 Data Processing Upon Parity Error Occurrence

#### PROCESSING DURING ERROR RECOVERY

PLL becomes locked and data demodulation begins when preambles B, M and W are detected.

RDATA output data is output from the RLRCK edge after RERR goes Low.

Figure 21 Internal Lock Signal

# **CHANNEL STATUS OUTPUT**

## DATA CATEGORY SPECIFICATION BIT 1 OUTPUT (AUDIO)

The AUDIO <u>pin outputs</u> bit 1 of the channel status indicating that the input bi-phase data is PCM audio data. AUDIO status is immediately output upon detection of RERR even during High output.

An output ORed with IEC61937 or the DTS-CD/LD detection flag is also possible with AOSEL.

| AUDIO | OUTPUT CONDITIONS               |

|-------|---------------------------------|

| 0     | PCM audio data (CS bit 1 = Low) |

| 1     | Non-audio data (CS bit 1 = High |

Table 12 AUDIO Output

## **EMPHASIS INFORMATION OUTPUT (EMPHA)**

The EMPHA pin output indicates that the signal has the presence or absence of  $50/15\mu$ s emphasis for consumer and broadcast studio.

EMPHA status is immediately output upon detection of RERR even during High output.

| EMPHA | OUTPUT CONDITIONS     |

|-------|-----------------------|

| 0     | No pre-emphasis       |

| 1     | 50/15 μs pre-emphasis |

Table 13 EMPHA Output

# **OTHER OUTPUTS**

## VALIDITY FLAG OUTPUT (VO)

The validity flag can be output from the  $\overline{\text{AUDIO}}$  /VO pin by selecting the  $\overline{\text{AUDIO}}$  /VO output with VOSEL.

The validity flags transferred at each sub-frame are output as indicated in the timing diagram below.

| VO | OUTPUT CONDITIONS         |

|----|---------------------------|

| 0  | No error (not burst data) |

| 1  | Error (May be burst data) |

Table 14 VO Output

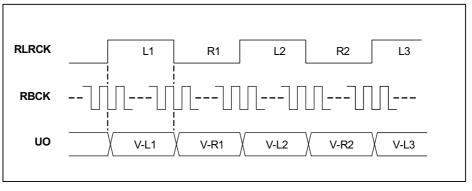

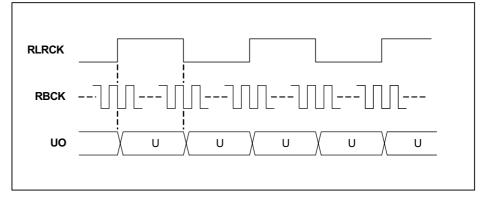

Figure 22 Validity Flag Output Timing

## **USER DATA OUTPUT (UO)**

User data can be output from the EMPHA/UO pin by selecting the EMPHA/UO output using UOSEL.

The user data transferred at each sub-frame is output as indicated in the following timing diagram.

Figure 23 User Data Output Timing

WM8802

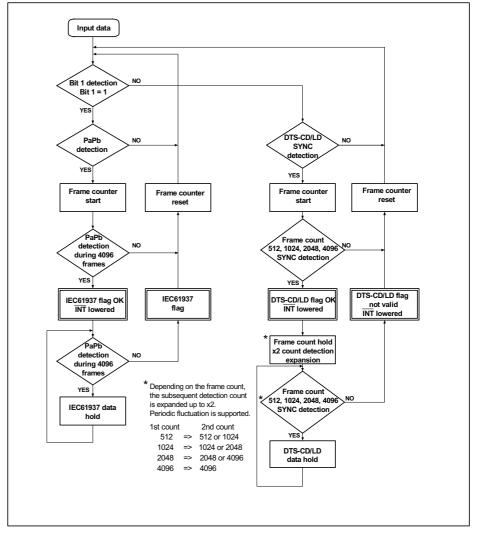

# IEC61937, DTS-CD/LD DETECTION FLAG OUTPUT

A function to output IEC61937 and DTS-CD/LD detection flags for non-PCM data is provided.

When the UNPCM non-PCM signal output setting is selected, as well as an indication on the AUDIO pin, an interrupt signal is output from INT upon detection of an IEC61937 or DTS-CD/LD sync signal. Non-PCM signal details can be known by reading this information from the output register.

The IEC61937 sync signal is detected and output when channel status bit 1 is non-PCM data ("1"). The IEC61937 sync signal is not output if bit 1 is PCM data ("0").

DTS-CD/LD sync signal detection is done based on the sync pattern and the base frequency. In the case of DTS-ES data detection, output is performed when the DTS5.1 channel sync signal is detected and the DTS-ES sync pattern has been verified.

The IEC61937 and DTS-CD/LD detection flags are cleared when fs has changed or upon occurrence of a PLL lock error or data error.

Since the DTS sync signal is provided within the audio data, digital data with the same code as the DTS sync signal may in rare cases exist for regular CD/LD records that are not recorded in the DTS format. Protection using the sync pattern or base frequency is provided so that such data is not misinterpreted as DTS-CD/LD detection flags. The detection sequence is shown below.

Figure 24 Detection Flag Output Flowchart

PP Rev 1.1 April 2004

# **DESCRIPTION OF MODULATION FUNCTION AND GENERAL-PURPOSE I/OS**

# MODULATION FUNCTION USAGE METHOD

#### **INITIAL SETTING**

The modulation function and general-purpose I/O port function cannot be used simultaneously because they share the same pins. INT should be pulled down with a 10k $\Omega$  resistor to select the modulation function. For the setting method, see page 10.

In the initial setting, the modulation function is stopped. The modulation function can be set using TXOPR.

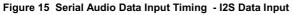

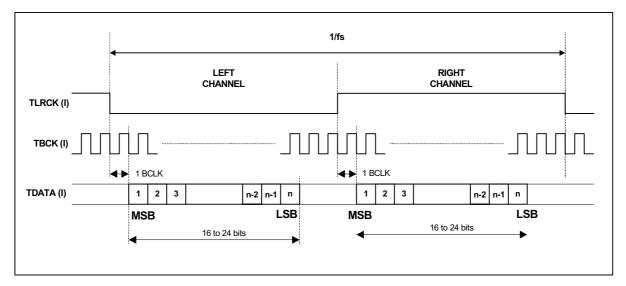

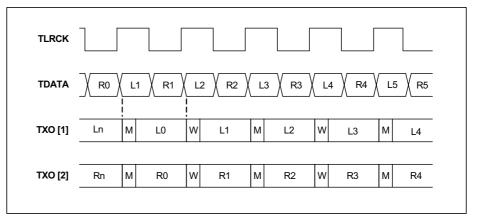

## DATA OUTPUT (TMCK, TBCK, TLRCK, TDATA, TXO)

Bi-phase modulated data is output from TXO by inputting a 256fs clock to TMCK, 64fs clock to TBCK, fs clock to TLRCK and audio data to TDATA.

The polarity of the TLRCK clock is set using TXLRP.

Input data can be modulated in the sampling range of 32kHz to 192kHz, TMCK rate of 4MHz to 25MHz and up to 24 bit data.

The initial value for the input data format is I<sup>2</sup>S. Switching to Left Justified format is set using TXDFS.

For the channel status, the first 48 bits of data can be written with the micro-controller interface.

TXO is fixed to Low by setting TXOPR to Stop.

Figure 25 Data Input Timing – I2S Data Input

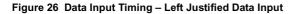

## VALIDITY FLAG INPUT (VI)

Validity flags can be input from RX5/VI by switching the RX5/VI input contents with VISEL.

The validity flag write timing is shown below. The validity flag can be written with the micro-controller interface but port settings have priority.

Writing validity flags with the micro-controller interface is done using VMODE.

| RX5/VI | OUTPUT CONDITIONS |

|--------|-------------------|

| 0      | No error          |

| 1      | Error             |

Table 15 RX5/V1 Input

Figure 27 Validity Flag Input Timing

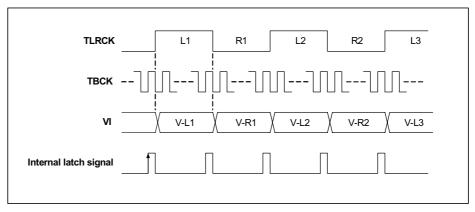

#### **USER DATA INPUT (UI)**

User data can be input from RX6/UI by switching the RX6/UI input contents using UISEL.

The user data write timing is shown below.

Figure 28 User Data Input Timing

#### MODULATED OUTPUT OF SDIN INPUT DATA

SDIN input data is modulated and can be output from TXO and RXOUT.

The setting to modulate SDIN input data is set using TDTSEL.

A clock should be input to synchronize SDIN to TMCK, TBCK and TLRCK.

Match the SDIN input data format to the setting used during modulation processing.

#### **MONAURAL OUTPUT**

It is possible to output the data of only one input data channel at the input rate of fs/2 with TXMOD[0:1].

This operation maintains the bi-phase modulation regularity but there is no correlation between the data and preambles.

Channel status write is synchronized with the output rate.

The validity flag and user data are written in frame units. Input the same data to the L and R channels.

Figure 29 Modulation of Data of Single Channel

## GENERAL PURPOSE I/O (GPIO0, GPIO1, GPIO2, GPIO3, GPIOEN)

#### **INITIAL SETTINGS**

The modulation function and general-purpose parallel I/O's share the same pins and therefore cannot be used simultaneously.  $\overline{\text{INT}}$  should be pulled down with a 10k $\Omega$  resistor to use the general-purpose I/O's. For the setting method, see page 10.

The general-purpose parallel I/O output function performs parallel conversion of the serial data input from the micro-controller interface and outputs the resulting data from GPIO0 GPIO1, GPIO2 and GPIO3. The input function saves the parallel data input to GPIO0, GPIO1, GPIO2, and GPIO3 to internal registers and reads the contents of these registers with the micro-controller interface.

It is not possible to mix the 4 bit general-purpose I/O's as inputs and outputs at the same time. Switching between input and output is done using GPIOEN The general-purpose I/Os all become input pins when GPIOEN is High and all output pins when GPIOEN is Low.

#### **INPUT/OUTPUT SETTINGS**

Data handling for general-purpose I/O is performed using the micro-controller interface and write/read registers.

General-purpose I/O write settings (Micro-controller  $\rightarrow$  Write register  $\rightarrow$  General-purpose I/O output)

- 1. Set GPIOEN to Low to output data from general-purpose I/O's.

- 2. Set the data to be output to CCB address 0xE8, command address 0x10 and input registers DI12 to DI15.

- 3. During write operation, make sure "0" is written to modulation function setting registers DI8 to DI11.

- 4. The data written to PI0 to PI3 is output from the general-purpose I/O's.

General-purpose I/O read settings (General-purpose I/O input → Read register → Micro-controller)

- 1. Set GPIOEN to High to input data to general-purpose I/O's.

- 2. The input data is saved to CCB address 0xEB and output registers DO0 to DO3.

- 3. Data can be sent to the micro-controller by reading GPO0 to GPO3.

# MICRO-CONTROLLER INTERFACE (INT, CL, CE, DI, DO)

#### **DESCRIPTION OF MICRO-CONTROLLER INTERFACE**

#### INTERRUPT OUTPUT (INT)

Interrupts are output when a change has occurred in the PLL lock status or output data information.

Interrupt output is determined by the register that selects the interrupt source, the INT pin that outputs that state transition and the registers that store the interrupt source data.

When  $\overline{INT}$  is set output High, the occurrence of an interrupt will set  $\overline{INT}$  output Low.  $\overline{INT}$  returns High after interrupt Low as dictated by the INTOPF setting.

INTOPF can be set to hold the Low pulse for a certain period and then clear it (to High) or clear it at the same time that the output register is read.

The interrupt sources can be selected from among the following items in Table 16. Multiple sources can be <u>selected</u> at the same time with the contents of CCB address 0xE8 and command address 0x08.  $\overline{\text{INT}}$  outputs the result of ORing (addition) the selected interrupt sources.

INT output = (selected source 1) + (selected source 2) + ... + (selected source n)

| NO. | COMMAND NAME | DESCRIPTION                                                                               |

|-----|--------------|-------------------------------------------------------------------------------------------|

| 1   | ERROR        | Output when RERR pin status has changed                                                   |

| 2   | INDET        | Output when input data pin status has changed (Oscillation amplifier operation condition) |

| 3   | FSCHG        | Output when input fs calculation result has changed. (Output amplifier condition)         |

| 4   | CSRNW        | Output when channel status data of first 48 bits has changed                              |

| 5   | UNPCM        | Output when AUDIO pin status has changed                                                  |

| 6   | PCRNW        | Output when burst preamble Pc has been updated                                            |

| 7   | SLIPO        | Output when data is read twice during slave setting and missing data is detected          |

| 8   | EMPF         | Output when emphasis information has changed                                              |

Table 16 Interrupt Source Setting Contents

The set interrupt source contents are saved to output registers DO8 to DO15 of CCB address 0xEA. The status of the RERR and AUDIO pins is output when the read registers for source items 1 and 5 are read. Except for source items 1 and 5, other data is saved to the registers upon occurrence of an interrupt source.

The oscillation amplifier must be set to the continuous operation mode for source items 2 and 3 when monitoring is performed even while the PLL is locked .

Following the occurrence of an interrupt from  $\overline{INT}$ , the interrupt is cleared at the same time that the output registers 0xEA is read.

In the interrupt Low pulse output mode the  $\overline{\rm INT}$  pulse width is between 1/2fs and 3/2fs for one interrupt pulse.

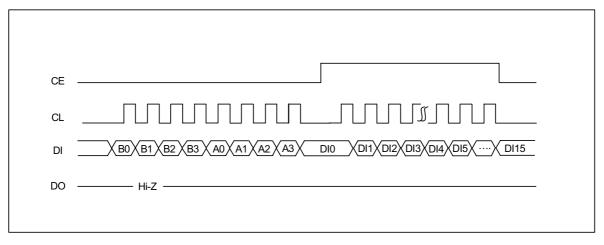

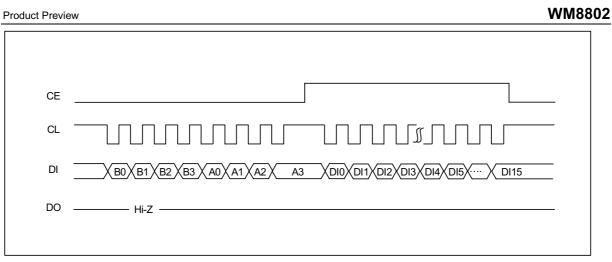

#### **CCB FORMAT**

Function settings as well as information writing and reading are performed by the micro-controller interface.

The data format of the micro-controller interface conforms to Sanyo's original serial bus format (CCB). Tri-state instead of open-drain is employed for the data output format.

Data input/output is performed following CCB address input. See the input/output timing chart

**Product Preview**

| REGISTER INPUT/OUTPUT<br>CONTENTS | R/W   | CCB<br>ADDRESS | В0 | B1 | B2 | В3 | A0 | A1 | A2 | A3 |

|-----------------------------------|-------|----------------|----|----|----|----|----|----|----|----|

| Function setting data input       | write | 0xE8           | 0  | 0  | 0  | 1  | 0  | 1  | 1  | 1  |

| CS data input                     | write | 0xE9           | 1  | 0  | 0  | 1  | 0  | 1  | 1  | 1  |

| Interrupt data output             | read  | 0xEA           | 0  | 1  | 0  | 1  | 0  | 1  | 1  | 1  |

| fs data output                    | read  | 0xEB           | 1  | 1  | 0  | 1  | 0  | 1  | 1  | 1  |

| CS data output                    | read  | 0xEC           | 0  | 0  | 1  | 1  | 0  | 1  | 1  | 1  |

| Pc data output                    | read  | 0xED           | 1  | 0  | 1  | 1  | 0  | 1  | 1  | 1  |

Table 17 Relationship between Register Input/Output Contents and CCB Addresses

#### DATA WRITE METHOD

Input is performed in the following sequence: CCB addresses of A0 to A3 and B0 to B3, chip addresses of DI0 and DI1, command addresses of DI4 to DI7 and data of DI8 to DI15. DI2 and DI3 are reserved for the system and should always be set to "0".

For the chip addresses, DI0 corresponds to CAL (low-order) and DI1 corresponds to CAU (high-order).

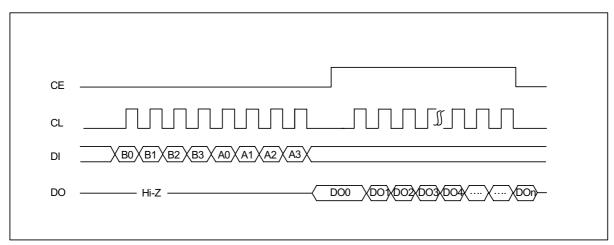

#### DATA READ METHOD

Read data is output from DO. DO is in the high impedance state when CE is Low and begins outputting at the rising edge of CE after the register address is recognised. DO then returns to the high impedance state at the falling edge of CE.

If DO outputs using multiple WM8802 units are to be shared the DO outputs of the WM8802 can be set to in a high impedance state using DOEN, This will prevent any misreading of registers from an unselected device.

#### **INPUT/OUTPUT TIMINGS**

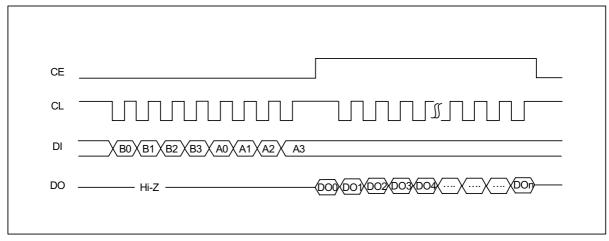

Figure 30 Input Timing Chart (Normal, Low Clock)

Figure 31 Input Timing Chart (Normal, High Clock)

Figure 32 Output Timing Chart (Normal, Low Clock)

WRITE DATA

#### WRITE COMMAND LIST

A list of the write commands is shown below.

To write the commands shown in the following table, set the CCB address to 0xE8.

| ADD. | SETTING ITEMS               | DI15    | DI14    | DI13   | DI12   | DI11    | DI10    | DI9    | DI8    |

|------|-----------------------------|---------|---------|--------|--------|---------|---------|--------|--------|

| 0    | All system setting          | TESTM   | 0       | TXOPR  | RXOPR  | INTOPF  | 0       | DOEN   | SYSRST |

| 1    | Demodulation system setting | 0       | 0       | FSLIM1 | FSLIM0 | RXMON   | AOSEL   | VOSEL  | UOSEL  |

| 2    | Master clock                | AMPOPR1 | AMPOPR0 | EXSYNC | PLLOPR | XMSEL1  | XMSEL0  | XINSEL | PLLSEL |

| 3    | R system output clock       | XRLRCK1 | XRLRCK0 | XRBCK1 | XRBCK0 | XRSEL1  | XRSEL0  | PRSEL1 | PRSEL0 |

| 4    | S system output clock       | XSLRCK1 | XSLRCK0 | XSBCK1 | XSBCK0 | PSLRCK1 | PSLRCK0 | PSBCK1 | PSBCK0 |

| 5    | Source switch               | 0       | RDTMUT  | RDTSTA | RDTSEL | 0       | RCKSEL  | OCKSEL | SELMTD |

| 6    | Data input/output           | RXOFF   | ROSEL2  | ROSEL1 | ROSEL0 | ULSEL   | RISEL2  | RISEL1 | RISEL0 |

| 7    | Output format setting       | SLRCKP  | SBCKP   | RLRCKP | RBCKP  | 0       | OFSEL2  | OFSEL1 | OFSEL0 |

| 8    | INT source selection        | EMPF    | SLIPO   | PCRNW  | UNPCM  | CSRNW   | FSCHG   | INDET  | ERROR  |

| 9    | RERR condition setting      | ERWT1   | ERWT0   | FSERR  | RESTA  | XTWT1   | XTWT0   | REDER  | RESEL  |

| 10   | Modulation system setting   | P13     | P12     | P11    | P10    | 0       | VMODE   | VISEL  | UISEL  |

| 11   | Modulation data setting     | 0       | 0       | TXMOD1 | TXMOD0 | TXMUT   | TDTSEL  | TWLRP  | TXDFS  |

| 12   | TEST                        | 0       | 0       | 0      | 0      | 0       | 0       | 0      | 0      |

| 13   | TEST                        | 0       | 0       | 0      | 0      | 0       | 0       | 0      | 0      |

| 14   | TEST                        | 0       | 0       | 0      | 0      | 0       | 0       | 0      | 0      |

| 15   | TEST                        | 0       | 0       | 0      | 0      | 0       | 0       | 0      | 0      |

The shaded parts in command area DI8 to DI15 are reserved bits with an input "0".

Command addresses 0x12 to 0x15 are reserved for testing purposes. Writing to these addresses is prohibited.

# WM8802

WRITE COMMAND DETAILS

|                    | All system se | ettings:                                                                                           |          |                                                 |                |               |                |        |  |  |  |  |

|--------------------|---------------|----------------------------------------------------------------------------------------------------|----------|-------------------------------------------------|----------------|---------------|----------------|--------|--|--|--|--|

| REGISTER ADDRESS   | DI7           | DI6                                                                                                | DI5      | DI4                                             | DI3            | DI2           | DI1            | DI0    |  |  |  |  |

| CCB address: 0xE8; | 0             | 0                                                                                                  | 0        | 0                                               | 0              | 0             | CAU            | CAL    |  |  |  |  |

| Command address: 0 |               |                                                                                                    |          | -                                               |                |               |                |        |  |  |  |  |

|                    | DI15          | DI14                                                                                               | DI13     | DI12                                            | DI11           | DI10          | DI9            | DI8    |  |  |  |  |

|                    | TESTM         | 0                                                                                                  | TXOPR    | RXOPR                                           | INTOPF         | 0             | DOEN           | SYSRST |  |  |  |  |

|                    | SYSRST        |                                                                                                    |          | reset<br>t reset (initial<br>circuits othe      | ,              | and registers |                |        |  |  |  |  |

|                    | DOEN          | DO output setting<br>0: Output (initial value)<br>1: Always high impedance state (read disabled)   |          |                                                 |                |               |                |        |  |  |  |  |

|                    | INTOPF        |                                                                                                    | 0: Outpu | output settin<br>t Low level d<br>t Low pulse o | uring source   |               | initial value) |        |  |  |  |  |

|                    | RXOPR         |                                                                                                    |          | lation functio<br>te (initial valu              | •              | setting       |                |        |  |  |  |  |

|                    | TXOPR         | TXOPR       Modulation function operation setting         0: Stop (initial value)       1: Operate |          |                                                 |                |               |                |        |  |  |  |  |

|                    | TESTM         |                                                                                                    | 0: Norma | de setting<br>al operation (<br>test mode       | initial value) |               |                |        |  |  |  |  |

RBCK and SBCK output Low and RLRCK and SLRCK output High when reset through SYSRST or the demodulation function stop setting is performed with RXOPR.